#### UNIVERSIDADE FEDERAL DE SANTA MARIA CENTRO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM INFORMÁTICA

# TÉCNICAS PARA REDUÇÃO DE CONSUMO EM CONVERSORES ANALÓGICO-DIGITAIS POR APROXIMAÇÃO SUCESSIVA E COMPARTILHAMENTO DE CARGA

DISSERTAÇÃO DE MESTRADO

**Taimur Gibran Rabuske Kuntz**

Santa Maria, RS, Brasil

2012

# TÉCNICAS PARA REDUÇÃO DE CONSUMO EM CONVERSORES ANALÓGICO-DIGITAIS POR APROXIMAÇÃO SUCESSIVA E COMPARTILHAMENTO DE CARGA

por

#### **Taimur Gibran Rabuske Kuntz**

Dissertação apresentada ao Curso de Mestrado do Programa de Pós-Graduação em Informática da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para a obtenção do grau de **Mestre em Computação**

Orientador: Prof. Cesar Ramos Rodrigues

Co-orientador: Prof. Jorge Manuel dos Santos Ribeiro Fernandes

Santa Maria, RS, Brasil

#### K96t Kuntz, Taimur Gibran Rabuske

Técnicas para redução de consumo em conversores analógico-digitais por aproximação sucessiva e compartilhamento de carga / por Taimur Gibran Rabuske Kuntz. – 2012.

61 f.: il.; 30 cm.

Orientador: Cesar Ramos Rodrigues

Co-orientador: Jorge Manuel dos Santos Ribeiro Fernandes Dissertação (Mestrado) - Universidade Federal de Santa Maria, Centro de Tecnologia, Programa de Pós-Graduação em Informática, RS, 2012.

1. Conversores analógico-digitais. 2. Eficiência energética. 3. Conversores por registrador de aproximação sucessiva. 4. Compartilhamento de carga. I. Rodrigues, Cesar Ramos. II. Fernandes, Jorge Manuel dos Santos Ribeiro. III. Título.

CDU 621.314

Ficha catalográfica elaborada por Alenir Inácio Coularte - CRB-10/990 Biblioteca Central da UFSM

(c) 2012

Todos os direitos autorais reservados a Taimur Gibran Rabuske Kuntz. A reprodução de partes ou do todo deste trabalho só poderá ser feita mediante a citação da fonte. E-mail: taimur.rabuske@gmail.com

#### Universidade Federal de Santa Maria Centro de Tecnologia Programa de Pós-Graduação em Informática

A Comissão Examinadora, abaixo assinada, aprova a Dissertação de Mestrado

### TÉCNICAS PARA REDUÇÃO DE CONSUMO EM CONVERSORES ANALÓGICO-DIGITAIS POR APROXIMAÇÃO SUCESSIVA E COMPARTILHAMENTO DE CARGA

elaborada por Taimur Gibran Rabuske Kuntz

como requisito parcial para obtenção do grau de **Mestre em Computação**

#### **COMISSÃO EXAMINADORA:**

Cesar Ramos Rodrigues, Dr. (Presidente/Orientador)

Cesar Augusto Prior, Dr. (UFSM)

Altamiro Amadeu Susin, Dr. (UFRGS)

Santa Maria, 16 de março de 2012.

## **DEDICATÓRIA**

Ao Seu Vitor...

The show must go on!

I'll face it with a grin!

I'm never giving in!

On with the show!

—Freddie Mercury

E à pessoa a quem devo tudo, e não tive tempo de retribuir...

Je ne te vois pas, je ne t'entends pas, tu n'es pas ici, tu n'es plus ici. Néanmoins, maman, je t'aimerai tous le jours.

#### **AGRADECIMENTOS**

Agradeço, sobretudo, à Maria Amália, pela paciência, carinho e apoio.

Agradeço também, em ordem alfabética, Alexandre Gheller Martini, Arlete Rodrigues, Professor Cesar Rodrigues, David Correia, Edinei Santin, Elvis Rabuske Hendges, Fábio Rabuske, Fárida Monireh Rabuske, Hugo Gonçalves, Professor Jorge Fernandes, Marcelo Dal Alba, Mateus Beck Fonseca, Miguel Martins, Renan Birck Pinheiro, Professor Saeid Nooshabadi, Tiago da Silveira.

"Um homem precisa viajar. Por sua conta, não por meio de histórias, imagens, livro ou TV. Precisa viajar por si, com seus olhos e pés, para entender o que é seu. Para um dia plantar suas próprias árvores e dar-lhes valor. Conhecer o frio para desfrutar do calor. E o oposto. Sentir a distância e o desabrigo para estar bem sob o próprio teto. Um homem precisa viajar para lugares que não conhece, para quebrar essa arrogância que nos faz ver o mundo como imaginamos e não simplesmente como ele é ou pode ser. Que nos faz professores e doutores do que não vimos, quando deveríamos ser alunos, e simplesmente ir ver... Il faut aller voir - é preciso ir ver! É preciso questionar o que se aprendeu. É preciso ir tocá-lo".

— Amyr Klink

#### **RESUMO**

Dissertação de Mestrado Programa de Pós-Graduação em Informática Universidade Federal de Santa Maria

#### TÉCNICAS PARA REDUÇÃO DE CONSUMO EM CONVERSORES ANALÓGICO-DIGITAIS POR APROXIMAÇÃO SUCESSIVA E COMPARTILHAMENTO DE CARGA

Autor: Taimur Gibran Rabuske Kuntz Orientador: Cesar Ramos Rodrigues, Dr. Co-orientador: Jorge Manuel dos Santos Ribeiro Fernandes, Dr. Local e data da defesa: Santa Maria, 16 de março de 2012.

As novas tendências e tecnologias emergentes motivam o projeto de conversores analógico-digitais (ADCs) que precisam suprir especificações cada vez mais restritivas. Nesse contexto, uma métrica de projeto que é constantemente forçada em direção à redução é o consumo de potência, fato esse que leva à concepção de melhorias tanto em nível arquitetural como em nível de circuito elétrico. Este trabalho tem como objetivo elevar a eficiência energética dos ADCs por aproximações sucessivas e compartilhamento de carga, visto que essa é uma arquitetura relativamente nova e inexplorada. Portanto, três ADCs completos são projetados ao longo deste trabalho, e cada um traz inovações que ajudam a reduzir o consumo de potência. As técnicas concebidas aqui incluem maneiras novas de efetuar a captura do sinal de entrada e um circuito para reduzir a potência drenada no ciclo de pré-carga. Além disso, três arquiteturas diferentes de controlador digital para essa topologia de ADC são expostas. Mais, um novo circuito de chave com *bootstrapping* é apresentado, o qual apresenta um número de dispositivos menor e uma eficiência energética extremamente alta.

**Palavras-chave:** Conversores analógico-digitais, Eficiência energética, Conversores por registrador de aproximação sucessiva, Compartilhamento de carga.

#### **ABSTRACT**

Master's Dissertation Computer Sciences Universidade Federal de Santa Maria

# TECHNIQUES FOR POWER REDUCTION IN SUCCESSIVE APPROXIMATION CHARGE SHARING ANALOG-TO-DIGITAL CONVERTERS

Author: Taimur Gibran Rabuske Kuntz Advisor: Cesar Ramos Rodrigues, Dr.

Coadvisor: Jorge Manuel dos Santos Ribeiro Fernandes, Dr.

New trends and emerging technologies motivate the design of analog-to-digital converters (ADCs) which must fit in increasingly constrained environments. Within this context, one design metric which is constantly forced towards reduction is the power consumption, leading the designers to come up with improvements in both the architecture and circuit levels. This work aims to push forward the energy efficiency of the successive approximation charge sharing ADC, which is a relatively new and unexplored architecture. Therefore, three complete ADCs are designed throughout this work, each one bringing novelties that help decreasing the power consumption. The techniques devised here include novel manners of dealing with the tracking of the input signal and a circuit to reduce power drained in the pre-charge cycle. Also, three different architectures of digital controller for this ADC topology are designed. Moreover, a novel bootstrapping switch circuit is presented, which provides lower devices-count and a extremely high energy efficiency.

**Keywords:** Analog-to-digital conveters, energy efficiency, successive approximation register converters, charge sharing.

# **SUMÁRIO**

| 1 I        | NTRODUÇÃO                                                              | 11 |

|------------|------------------------------------------------------------------------|----|

| 1.1        | Conversores por redistribuição e por compartilhamento de carga         |    |

| 1.2        | Escopo deste trabalho                                                  |    |

| 2 (        |                                                                        | `  |

|            | CONVERSORES DE APROXIMAÇÃO SUCESSIVAS POR COMPARTILHAMENTO<br>DE CARGA |    |

| L          | L CARGA                                                                | 10 |

|            | RTIGO I: A 54.2 $\mu$ W 5MSps 9-BIT ULTRA-LOW ENERGY ANALOG-TO-DIGITAL |    |

| (          | CONVERTER IN 180nm TECHNOLOGY                                          | 19 |

| 3.1        | Introduction                                                           | 20 |

| <b>3.2</b> | Operating Principle                                                    | 21 |

| 3.2.1      | Pre-Charge Cycle                                                       | 22 |

| 3.3        | Circuits Implementation                                                | 23 |

| 3.3.1      | Capacitive Array                                                       | 23 |

| 3.3.2      | Input Sample and Hold                                                  | 24 |

| 3.3.3      | Comparator                                                             | 25 |

| 3.3.4      | Control Logic                                                          | 25 |

| 3.4        | Layout                                                                 | 26 |

| 3.5        | Simulation Results                                                     |    |

| 3.6        | Conclusions                                                            | 28 |

| 3.7        | References                                                             | 28 |

| 4 A        | ARTIGO II: A 5MSps 13.25 $\mu$ W 8-BIT SAR ADC WITH SINGLE-ENDED OR    |    |

|            | DIFFERENTIAL INPUT.                                                    | 30 |

| 4.1        | Introduction                                                           |    |

| 4.1        | ADC Workint Principle                                                  |    |

| 4.2        | Track and Hold Circuit                                                 |    |

| 4.3.1      |                                                                        |    |

| 4.3.1      | TH Background TH Topology Derivation                                   |    |

| 4.3.3      | <u> </u>                                                               |    |

|            | TH Circuit Implementation                                              |    |

| 4.3.4      | Bootstrapping Switch                                                   |    |

| 4.3.5      | TH Simulation Results                                                  |    |

| 4.4        | ADC Circuit Implementation                                             |    |

| 4.4.1      | Comparator                                                             |    |

| 4.4.2      |                                                                        |    |

| 4.4.3      |                                                                        | 36 |

| 4.5        |                                                                        |    |

| 4.6        | Conclusion                                                             | 37 |

| 4.7                                                              | Bibliography                                                          | 37   |  |  |  |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------|------|--|--|--|--|--|

| 5 D                                                              | DISCUSSÃO                                                             | 39   |  |  |  |  |  |

| 6 C                                                              | CONCLUSÃO                                                             | 41   |  |  |  |  |  |

| 6.1                                                              | Sugestão de trabalho futuro                                           |      |  |  |  |  |  |

|                                                                  |                                                                       |      |  |  |  |  |  |

| APÊNDICE A ARTIGO III: A NOVEL ENERGY EFFICIENT DIGITAL CONTROL- |                                                                       |      |  |  |  |  |  |

|                                                                  | LER FOR CHARGE SHARING SUCCESSIVE APPROXIMATION ADC                   |      |  |  |  |  |  |

| A.1                                                              | Introduction                                                          |      |  |  |  |  |  |

| <b>A.2</b>                                                       | Charge Sharing ADC                                                    | 44   |  |  |  |  |  |

| <b>A.3</b>                                                       | Standard Cells Approach                                               |      |  |  |  |  |  |

| <b>A.4</b>                                                       | Full-Custom Approach                                                  | 45   |  |  |  |  |  |

| <b>A.5</b>                                                       | Simulation Results                                                    | 46   |  |  |  |  |  |

| <b>A.6</b>                                                       | Conclusion                                                            | 47   |  |  |  |  |  |

| <b>A.7</b>                                                       | References                                                            | 47   |  |  |  |  |  |

| A DÊN                                                            | IDICE B ARTIGO IV: AN ENERGY-EFFICIENT 1MSps $7\mu$ W 11.9fJ/CONVERSI | ΟNI  |  |  |  |  |  |

| APEN                                                             | STEP 7pJ/SAMPLE 10-BIT SAR ADC IN 90nm                                |      |  |  |  |  |  |

| B.1                                                              | • ·                                                                   |      |  |  |  |  |  |

| B.2                                                              | Introduction                                                          |      |  |  |  |  |  |

| B.3                                                              | Operation Principle                                                   |      |  |  |  |  |  |

| <b>в.з</b><br>В.3.1                                              | Circuits                                                              |      |  |  |  |  |  |

|                                                                  | Track and Hold                                                        |      |  |  |  |  |  |

| B.3.2<br>B.3.3                                                   | DAC                                                                   |      |  |  |  |  |  |

|                                                                  | Comparator                                                            |      |  |  |  |  |  |

| B.3.4                                                            | Custom Controller                                                     |      |  |  |  |  |  |

| B.4                                                              | Simulation Results                                                    |      |  |  |  |  |  |

| B.5                                                              | Conclusions                                                           |      |  |  |  |  |  |

| <b>B.6</b>                                                       | References                                                            | 52   |  |  |  |  |  |

| APÊN                                                             | IDICE C ARTIGO V: A TRACK AND HOLD FOR SINGLE-ENDED OR DIF-           |      |  |  |  |  |  |

|                                                                  | FERENTIAL INPUT WITH ADJUSTABLE OUTPUT COMMON MODE                    | E 53 |  |  |  |  |  |

| <b>C.1</b>                                                       | Introduction                                                          | 54   |  |  |  |  |  |

| <b>C.2</b>                                                       | TH Background                                                         | 54   |  |  |  |  |  |

| <b>C.3</b>                                                       | Topology Derivation                                                   | 55   |  |  |  |  |  |

| <b>C.4</b>                                                       | Implementation                                                        |      |  |  |  |  |  |

| <b>C.5</b>                                                       | Simulation Results                                                    | 56   |  |  |  |  |  |

| <b>C.6</b>                                                       | Conclusions                                                           | 57   |  |  |  |  |  |

| <b>C.7</b>                                                       | References                                                            | 57   |  |  |  |  |  |

| ANEXO A EMAIL DE ACEITAÇÃO DO ARTIGO II                          |                                                                       |      |  |  |  |  |  |

| ANEXO B OUTRAS PUBLICAÇÕES DURANTE O MESTRADO                    |                                                                       |      |  |  |  |  |  |

| REFERÊNCIAS                                                      |                                                                       |      |  |  |  |  |  |

## 1 INTRODUÇÃO

É trivial perceber um grau crescente de onipresença de elementos computacionais no cotidiano humano. O homem contemporâneo tem uma grande parcela das suas tarefas diárias guiadas ou intermediadas por computadores e sistemas eletrônicos. Esta afirmação pode ser clareada se recorrermos ao exemplo da trajetória evolutiva de dois aspectos fundamentais da vida moderna: os meios de comunicação e a economia.

Em (CLARK, 2007), o autor sumariza de maneira extremamente interessante a evolução da velocidade de propagação da informação no decorrer dos séculos. De acordo com o autor, antes da revolução industrial, as pessoas viviam em um mundo onde a informação se propagava tão lentamente que muitos morriam guerreando por questões que já haviam sido resolvidas. A Batalha de New Orleans, lutada aos 8 de janeiro de 1815 por britânicos e estado-unidenses, resultou em mais de mil mortos e ocorreu porque os comandantes de ambos os exércitos não sabiam que o Tratado de Gante havia estabelecido a paz entre os países em 24 de dezembro do ano anterior. Ainda de acordo com o autor, a informação viajava em velocidades da ordem de poucos quilômetros horários naquela era, barreira que veio somente a ser quebrada com a introdução do telégrafo em 1844 e da linha telegráfica submarina entre Inglaterra e França em 1851. Ainda no fim do século XIX, com a difusão dessa tecnologia pelo mundo, o grande terremoto de Nobi, no Japão, foi publicado em Londres com em torno de um dia de atraso desde o seu acontecimento, apesar dos mais de 9 mil quilômetros que separam os países. No entanto, por mais que essa evolução soe surpreendente, uma velocidade nessa ordem de grandeza soa ínfima se comparada aos padrões contemporâneos. Para exemplificar, informações sobre o terremoto na costa leste do Japão, ocorrido em 11 de março de 2011, estavam disponíveis em telefones móveis ligado à internet de praticamente todo o mundo minutos após o seu acontecimento.

Outro aspecto global que sofreu drástica mutação possibilitada pelas tecnologias eletrônicas diz respeito à economia. A história do sistema monetário se estende por milênios, partindo de sistemas arcaicos de troca (escambo), passando por sistemas baseados na ausência de reciprocidade explícita (denominadamente economias de doação), evoluindo para moedas de troca padronizadas(CLARK, 2007). No entanto, uma grande parcela das transações de capital atuais acontece sem troca de propriedade de bens físicos, como metais preciosos ou papel-moeda. O capital passou a ser abstraído por *bytes* em bancos de dados de instituições bancárias. Atualmente, é absolutamente plausível depender exclusivamente de meios de troca virtuais para comprar e vender (transferências bancárias *on-line*, compras por cartão de crédito ou pagamento por débito bancário). O dinheiro físico deixou de ser vital e deu espaço ao dinheiro eletrônico, sem qualquer impacto negativo ao sistema capitalista e, pelo contrário, facilitando e agilizando transações comerciais.

Essa tendência de crescente dependência de computadores para as tarefas diárias sugere que os sistemas eletrônicos sofram uma progressiva redução de volume visando ao conforto de seus usuários. De fato, as tecnologias emergentes em sistemas eletrônicos cada vez mais se focam em miniaturização e portabilidade. Um acessório eletrônico portátil típico é alimentado por baterias, mas o objetivo máximo destas aplicações é que elas operem autossuficientes em termos de energia, retirando a potência elétrica necessária do próprio ambiente. Para alcançar este fim, torna-se necessário recorrer a transdutores para transformar energia de diversas formas em corrente elétrica. Como exemplos, podem ser citados células solares e transdutores piezelétricos e termoelétricos. Ultimamente, o uso da energia cada vez mais abundante no espectro eletromagnético de radiofrequência aparece como uma alternativa viável de suprimento. O projeto de sistemas autossuficientes é atualmente inviabilizado pela incompatibilidade da potência gerada por essas fontes alternativas com a potência necessária para alimentar sistemas convencionais. Portanto, a redução de potência dos blocos de circuito nesses sistemas eletrônicos portáteis é de evidente benefício, pois maximiza o tempo de vida das baterias nos sistemas dependentes destas e pode, idealmente, viabilizar a concepção de sistemas autossuficientes em energia.

Um dispositivo requerido para uma larga gama de aplicações de baixa potência é o conversor analógico-digital (ADC). ADCs são circuitos capazes de transformar uma

grandeza física do mundo real e analógico em uma representação abstrata aproximada no domínio digital. De um lado, o domínio analógico representa fielmente uma variedade de situações do mundo real, enquanto o domínio digital sofre desenvolvimento massivo em tecnologias para processamento de sinais e transmissão e armazenamento de dados. Existem diversas topologias de ADCs, cobrindo diferentes gamas de especificações, em torno da tríade de requisitos: frequência de amostragem, potência e resolução.

Os conversores flash, por exemplo, apresentam baixa latência, fruto do funcionamento altamente paralelizado. São utilizados  $2^N-1$  comparadores, onde N é o número de bits do conversor, e todos são ativados ao mesmo tempo para cada conversão. Disto, decorre que o consumo de potência dos conversores flash é relativamente alto se comparado às demais topologias. Por outro lado, é uma boa opção para aplicações que demandam taxa de conversão alta e resolução baixa.

Outras topologias populares são a sigma delta ( $\Sigma\Delta$ ), capaz de efetuar conversões a resoluções mais altas com taxas de amostragens moderadas; os conversores *pipeline*, que desempenham bem em resoluções e taxas de amostragem médias; e os conversores por aproximações sucessivas, que são explicados na próxima seção.

#### 1.1 Conversores por redistribuição e por compartilhamento de carga

Entre as diversas topologias de ADCs atualmente disponíveis, os conversores por registrador de aproximações sucessivas, ou *successive approximation register* (SAR), são conhecidos pela sua elevada eficiência energética. Eles são muito atrativos em aplicações que demandam baixas taxas de amostragem e com requisitos de potência restritivos, sobretudo por causa da sua dependência logarítmica de complexidade com relação à resolução. Baseados em um laço de realimentação, os conversores SAR convergem iterativamente à palavra digital final, comparando o valor de um conversor digital-analógico (DAC) com uma representação amostrada do sinal de entrada, capturado por um circuito de *track-and-hold*. O ciclo de conversão é guiado pelo algoritmo da busca binária.

Os conversores SAR mais utilizados se baseiam no método da redistribuição de carga, proposto em (MCCREARY; GRAY, 1975), chamado assim devido à topologia de DAC que eles empregam. Nesta abordagem, o DAC capacitivo é também usado como

*track-and-hold*, e a cada passo do algoritmo de conversão, um dos capacitores de peso binário é conectado ao nó de terra ou tensão de referência, fazendo a tensão de erro diminuir em direção a zero.

Em (CRANINCKX; PLAS, 2007), os autores apresentam um método para implementar conversores SAR capacitivos baseando-se em compartilhamento de carga, ao invés de redistribuição de carga. Como vantagem, o DAC é totalmente pré-carregado uma vez no início do ciclo de conversão, ao invés de interações com as linhas de alimentação na resolução de cada *bit*. Além disso, os requerimentos de tempo de acomodação para o DAC podem ser relaxados durante o ciclo de projeto e, ainda mais importante, tornando desnecessário o emprego de um amplificador operacional como *buffer* da tensão de referência. Erroneamente, esse amplificador é geralmente desconsiderado nas medições de potência de conversores por redistribuição de carga, embora possa ser significante e até mesmo dominante. O princípio de funcionamento dessa topologia de ADC é explicado com mais detalhes nos Capítulos 3 e 4.

Em (GIANNINI et al., 2008), um ADC por compartilhamento de carga com desempenho superior em termos de ruído térmico é apresentado. A robustez do projeto é garantida com um ciclo a mais na conversão, um comparador com nível de ruído programável e um pequeno processamento digital.

De fato, (CRANINCKX; PLAS, 2007) e (GIANNINI et al., 2008) são as únicas publicações de maior relevância tratando dessa arquitetura. O ADC por aproximações sucessivas e compartilhamento de carga é uma arquitetura relativamente recente, com aproximadamente cinco anos desde a sua concepção em (CRANINCKX; PLAS, 2007). Deste modo, esta é uma topologia parcamente explorada que, por consequência, oferece grande margem para desenvolvimento tecnológico e científico.

#### 1.2 Escopo deste trabalho

Este trabalho foca-se em otimizar o consumo de potência em ADCs por aproximações sucessivas utilizando compartilhamento de carga. Para isso, são apresentadas inovações em nível de topologias e circuitos.

Os elementos textuais deste trabalho são apresentados na forma de artigos científicos. Esta modalidade é prevista em (UNIVERSIDADE FEDERAL DE SANTA MA-RIA. Pró-Reitoria de Pós-Graduação e Pesquisa, 2010), sendo que cada capítulo corresponde a um artigo científico publicado, submetido ou escrito para periódico indexado. A produção científica relativa a conferências internacionais foi incluída no formato de apêndices, e deve ser considerada como parte importante deste trabalho.

O Capítulo 2 apresenta a topologia de conversor analógico-digital explorada neste trabalho, e explica o seu funcionamento.

O Capítulo 3, publicado no periódico *Springer Analog Integrated Circuits and Sig-nal Processing* sob o título de *A 54.2µW 5MSps 9-bit Ultra-low Energy Analog-to-Digital Converter in 180nm*, propõe um ADC por compartilhamento de carga que faz uso de escalonamento de tensão e ciclo de pré-carga iterativo para aumentar a eficiência energética. Também é apresentado um circuito de controle eficiente projetado utilizando *standard cells*.

O Capítulo 4, entitulado *A 5MSps 13.25µW 8-bit SAR ADC with Single-Ended or Dif- ferential Input*, corresponde ao artigo aceito para publicação no periódico *Elsevier Mi- croelectronics Journal* (carta de aceitação no Anexo A). O artigo traz um ADC que faz uso de um circuito de *track-and-hold* que ajusta automaticamente o nível de modo comum da saída recorrendo a técnica de capacitores comutados. Esta técnica foi apresentada anteriormente em conferência (Apêndice C). A topologia de ADC é fortemente baseada no trabalho anteriormente publicado em conferência e incluído no Apêndice B. O circuito de controle para esse ADC foi também apresentado anteriormente em conferência e é incluído no Apêndice A.

Por último, o Capítulo 5 apresenta uma discussão geral a respeito dos resultados obtidos e o Capítulo 6 conclui este trabalho e propõe trabalhos futuros.

## 2 CONVERSORES DE APROXIMAÇÃO SUCESSIVAS POR COMPARTILHAMENTO DE CARGA

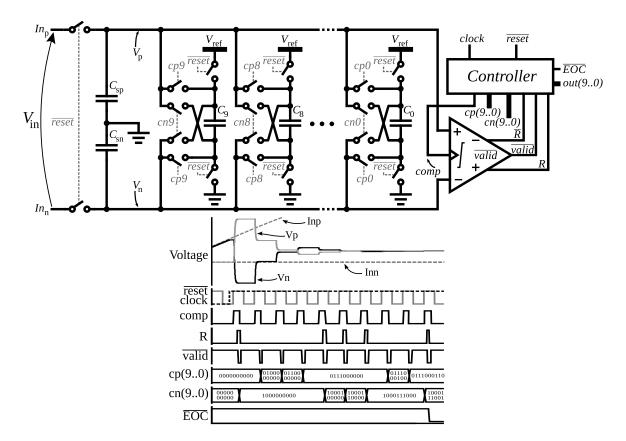

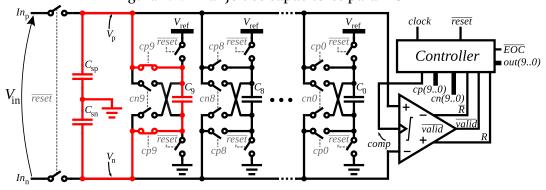

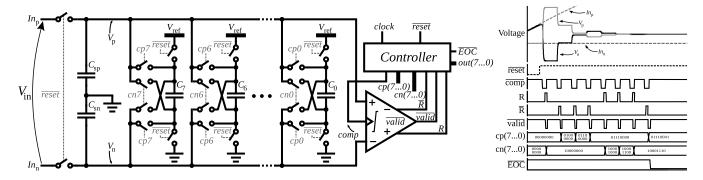

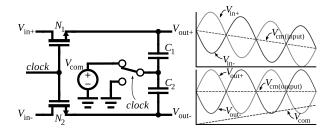

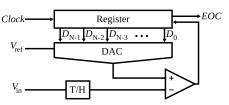

De forma similar aos conversores analógico-digitais por redistribuição de carga, a arquitetura baseada em compartilhamento de carga requer um controlador, um comparador de tensão e um conversor digital-analógico. Entretanto, devido ao seu princípio de operação, um circuito de *track-and-hold* é necessário, visto que o sinal capturado não pode ser mantido apenas pelas capacitâncias do conversor digital-analógico. A topologia é ilustrada na Figura 2.1, para um conversor de 10 bits.

Uma conversão se dá na borda de descida da entrada reset. Enquanto esta entrada

Figura 2.1: Diagrama de blocos do SAR por compartilhamento de carga e formas de onda ilustrativas.

Figura 2.2: Ciclo de pré-carga do DAC e amostragem da entrada

Figura 2.3: Ciclo de decisão do bit mais significativo

Figura 2.4: Arranjo dos capacitores para MSB=1

Figura 2.5: Arranjo dos capacitores para MSB=0

está baixa, o circuito track-and-hold está acompanhando a entrada; enquanto isso, o conversor digital-analógico está sendo pré-carregado (Figura 2.2). Para o conversor de 10 bits aqui descrito, o conversor digital-analógico é constituído por 10 capacitores com valores de carga definidos conforme pesos binários. Durante o processo de précarga, estas capacitâncias são ligadas à referência de tensão  $V_{ref}$ , e desconectadas dos capacitores de track-and-hold e entre si. Quando  $\overline{reset}$  retorna ao nível lógico alto, o sinal acompanhado pelo track-and-hold é mantido estável, e o conversor digital-analógico é desconectado de  $V_{ref}$ .

Após, o circuito SAR (registrador de aproximação sucessiva) começa a executar o algoritmo de busca binária, adicionando ou subtraindo carga nos capacitores de amostragem. Na próxima borda de subida do clock, o comparador é inicializado de forma a comparar as tensões  $V_p$  e  $V_n$  (Figura 2.3). O resultado da comparação é o bit mais significativo (MSB) da conversão. Após, alguma carga precisa ser adicionada ou subtraída das capacitâncias do track-and-hold, de forma a fazer a diferença de tensão (erro de tensão) entre  $V_p$  e  $V_n$  menor. Se, por exemplo,  $V_p$  for mais alta que  $V_n$ , nós removemos a quantidade de carga equivalente a um MSB (bit mais significativo), ativando o sinal de controle cn9 (Figura 2.4). Assim, o capacitor  $C_9$  seria conectado em antiparalelo com a combinação em série de  $C_{sp}$  e  $C_{sn}$ . Se, por outro lado,  $V_p$  fosse menor que  $V_n$ , a mesma quantidade de carga seria adicionada a  $C_9$ , por meio da ativação do sinal de controle cp9 (Figura 2.5). O processo repete-se progressivamente para os outros bits, adicionando ou subtraindo carga da carga amostrada em  $V_{in}$ . Ao final, cn(9...0) representa a saída de 10 bits desejada.

# 3 ARTIGO I: A 54.2 $\mu$ W 5MSps 9-BIT ULTRA-LOW ENERGY ANALOG-TO-DIGITAL CONVERTER IN 180nm TECHNOLOGY

RABUSKE, T. G.; NOOSHABADI, S.; RODRIGUES, C. R. A 54.2  $\mu$ W 5 MSps 9-bit ultralow energy analog-to-digital converter in 180 nm technology. **Analog Integrated Circuits and Signal Processing**, Springer. doi:10.1007/s10470-011-9821-4. Pré-publicado em dez. 2011.

# A 54.2 µW 5 MSps 9-bit ultra-low energy analog-to-digital converter in 180 nm technology

Taimur Gibran Rabuske · Saeid Nooshabadi · Cesar Ramos Rodrigues

Received: 23 December 2010/Revised: 20 October 2011/Accepted: 14 December 2011 © Springer Science+Business Media, LLC 2011

**Abstract** This paper aims to address the growing need for ultra-low power analog-to-digital converters (ADC). For this purpose, we pushed the limitations of conventional successive approximation register ADCs through the use of deep voltage scaling, a novel iterative precharging scheme, and topological improvements over recent works. From the simulations results we achieve a figure of merit of 31 fJ per conversion step, with an 8.45 effective number of bits, working at 5 MSps.

**Keywords** SAR ADC · Ultra-low power · Ultra-low energy · Step-wise · Charge sharing

#### 1 Introduction

Lower system power consumption is a requirement for an ever increasing range of applications. Beyond the energy critical health applications, like pacemakers or hearing aids, there are new application frontiers where power budgets are becoming very tight. One example is wireless sensor networks, where sometimes the only energy available for the nodes to work comes from scavenging, or lossy inductive coupling with a radio-frequency source. Also, the

T. G. Rabuske · C. R. Rodrigues Universidade Federal de Santa Maria (UFSM), Santa Maria, Brazil e-mail: taimur@mail.ufsm.br

C. R. Rodrigues e-mail: cesar@ieee.org

S. Nooshabadi (⊠) Michigan Technological University (Michigan Tech), Houghton, MI 49931, USA e-mail: saeid@mtu.edu

Published online: 28 December 2011

concept of wearable computing demands power-aware solutions, in order to increase battery lifetime.

In the field of analog to digital data converters, the successive approximations register (SAR) topology has been proved to be very attractive for low data rates, in applications where power is the main constrain. Part of the merit comes from the presence of a single comparator independently of resolution. Few approaches have been tried to extend the power efficiency further. In [11] authors present a low energy successive approximation charge-redistribution (CR) analog-to-digital converters (ADC) focusing on distributed sensor networks, where both active and standby power must be minimized. In [8], the design of an ADC working at 0.6 V that relies on a time-domain comparator is presented. In [13] a very energy efficient SAR ADC is designed that realizes the CR process based on a multi-step charging.

This paper extends the traditional energy-efficient SAR ADC, with improvements on the topological level and other circuit-level novelties. In the inspiring work in [3], the authors present a method to increase the efficiency of a successive approximation converter by doing the signal processing using charge sharing (CS), instead of CR. As a consequence, low output impedance operational amplifiers can be eliminated on the input and reference signals, indirectly reducing the power consumption of the ADC itself. In this paper, we will present a further improvement to this methodology, in a way which the area is substantially reduced. Further, the power drained from input signal is also reduced. The CS methodology made another innovation possible, that could push the limits of standard SAR further, reducing the amount of energy necessary to precharge the same values of capacitance.

Further improvements on the circuit implementation level are also made towards power reduction. We have

implemented the logic control circuit with both gate-level optimization and deep voltage-scaling, and proved this choice to have a great overall impact on ADC power efficiency.

We describe the operating principle in Sect. 2, together with the architectural innovations. The circuit level implementation is discussed in Sect. 3, where a more detailed description of each circuit block is provided. The proposed layout is presented and explained in Sect. 4. The simulation results including transient noise and further information on the simulation environment are both described in the Sect. 5. Section 6 concludes this work.

#### 2 Operating principle

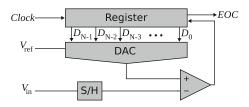

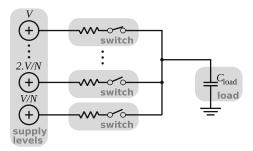

A successive approximation ADC converts a continuous analog waveform into a discrete digital representation via a binary search algorithm. In practice, binary search can be implemented based on a comparator, that compares at each step a sampled representation of the input signal to the output of a digital-to-analog converter (DAC) fed with a register representing a successively evaluated digital value, as in Fig. 1.

Conventional SAR ADCs rely on the CR method, socalled due to the DAC topology they employ. In that approach, the capacitive DAC is also used as tracking

Fig. 1 SAR ADC topology

circuit, and at every step, one of the binary-weighted capacitors is tied to ground or reference terminal, leading the error voltage to diminish towards zero.

In [3] authors present a method to implement capacitive SAR based on CS, rather than CR. As an advantage, the DAC is totally precharged once in the beginning of a conversion cycle, instead of per bit active interactions with the supply lines. Still, the settling requirements for DAC can be relaxed during design cycle, and most importantly, avoiding any power-hungry opamp buffering the reference signal. Misleadingly, this opamp is often not accounted for in the energy measurement of a given converter, which could be significant, or even dominant.

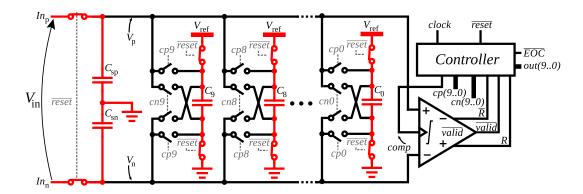

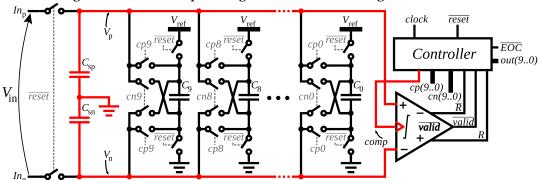

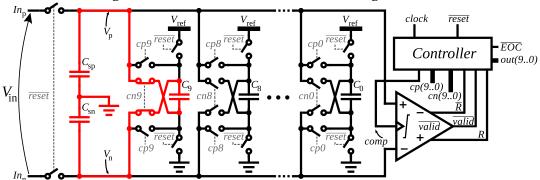

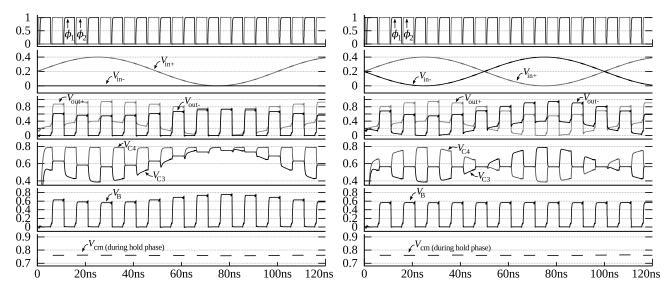

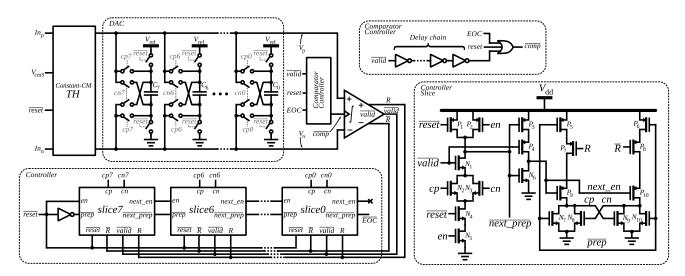

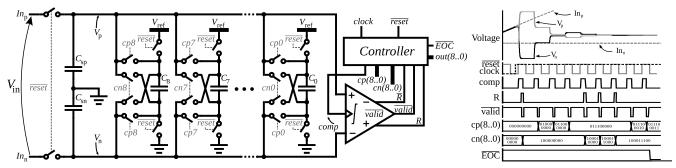

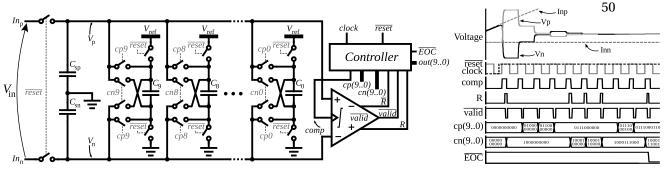

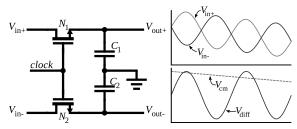

In this paper, we extended the passive CS ADC with topological improvements. Figure 2 shows a schematic representation of the architecture together with illustrative waveforms.

The circuit is composed of a digital controller, a voltage comparator, an analog multiplexing track and hold and a DAC with its pre-charge circuitry. Notice the DAC is made by binary weighted capacitive network and associated MOS-switches.

Assume that the DAC capacitive matrix in Fig. 2 is initially pre-charged to  $V_{ref}$ . Also, assume all cn and cp switches are off. One of the capacitor pairs between  $C_{pA}$ – $C_{nA}$  and  $C_{pB}$ – $C_{nB}$  is tracking the input signal, while the other pair is connected to DAC. The conversion cycle is started by a pulse on the *start* input pin. The analog multiplexer then switches the capacitor pair that was initially in tracking mode to the Qp and Qn nodes. A pulse on the *comp* pin signals the comparator to compare the sampled voltages on IN+ and IN- nodes. The output from comparator forms the most significant bit (MSB) of the conversion. This bit is fed back into the controller. This first bit can also be treated as the sign (positive or negative) of the

Fig. 2 Block diagrams and corresponding waveforms for the proposed ADC topology

input signal. The controller uses this bit to set the controlling pairs of switches cn8 and cp8 to add/subtract charge to the input capacitor in order to converge the voltage difference between Qp and Qn nodes to zero. If the first resolved bit was an 1, the switches cn8 are turned on, forcing an amount of charge equal to half of the input range  $(\pm V_{ref}C_8)$  to be subtracted from the equivalent capacitance formed by input capacitance pair and  $C_8$ . Otherwise, in the case of MSB resolved as 0, cp8 switches turn on, adding charge to the equivalent capacitance. The operation is continued for all the other bits of the converter and, at the end, an N-bit representation of the sampled input is available at the output.

In conventional CR ADCs, an offset voltage in the comparator results in an offset of the transfer function of the converted signal, and does not manifest as non-linearity in the converter. On the other hand, for the passive CS topology, this is not the case. One can see that the total equivalent capacitance is different for each step during the search algorithm. Initially, the only capacitance connected to the comparator is one of the sampling capacitor pairs  $(C_{pA}-C_{nA} \text{ or } C_{pB}-C_{nB})$ . During the course of binary search, more capacitors are added in parallel to the sampling pair, increasing the equivalent capacitance. Even though the whole processing happens in the charge domain, the comparator is only able to make decisions regarding voltage levels on Qp and Qn nodes. The voltage forced on the terminals of a capacitor due to electrical charge is given by  $\frac{Q}{C}$ . However, C varies at each step of the search. Therefore, any mismatch on the comparator manifest as nonlinearity in the converter.

Nevertheless, conversion in CS domain has some important advantages over the standard CR. The first advantage is at the input track and hold side. On CR scheme, the DAC capacitors are also used to sample the signal. So, for the input signal to be sampled in a sufficiently short time, generally voltage buffers with low output impedance are needed on the input signal. This indirectly increases the overall power consumption, reducing energy efficiency. In the proposed modified architecture, with the use of an analog multiplexer, one input capacitor pair is used to perform the conversion, while other pair is made to track  $V_{in}$ . So, signal source impedance on the input can be relaxed to reduce the settling time to one conversion period.

Another important characteristic of CS architecture is with regard to the DAC pre-charge. In the CR scheme, on each step of the search, one capacitor is charged or discharged to reference voltages. Once again, for this charging to happen in a short time requires a buffer on the reference signal. However, for the CS scheme, the whole DAC is precharged only once per conversion, in the beginning of the cycle. This feature allows us to increase the energy

efficiency further, using a novel pre-charge mechanism, as be presented next.

#### 2.1 Pre-charge cycle

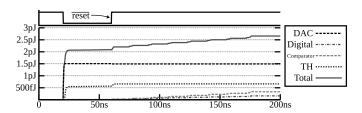

A significant part of energy spent by the ADC is due to precharge of capacitive DAC in the beginning of conversion cycle. To save energy we employ the stepwise pre-charge technique proposed in [12].

Consider a simple circuit composed by a capacitor being charged by a voltage source, through a simple switch. For the sake of simplicity, the switch is represented by a single resistor. At time  $t=t_0$ , the switch is turned on, and some charge is drained off the source towards the capacitor, and after some RC time constants, the current flow virtually stops. The total energy dissipated in the voltage source is given by,

$$E_{T,conventional} = E_S + E_C \tag{1}$$

where  $E_S$  and  $E_C$  are the energies dissipated in the switch and capacitor, respectively.

On the situation above, resistance of the switch only affects the settling time, and does not change the energy needed to completely charge the capacitor. The energy drawn from the voltage source is equally distributed among the switch and the capacitor as,

$$E_S = E_C = \frac{1}{2}CV^2 (2)$$

Since the energy is quadratic function of the voltage value, one can reduce the power dissipated in the switches performing the charge in multiple steps, as presented in [12]. This way the power dissipation is reduced at the cost of decreased circuit speed.

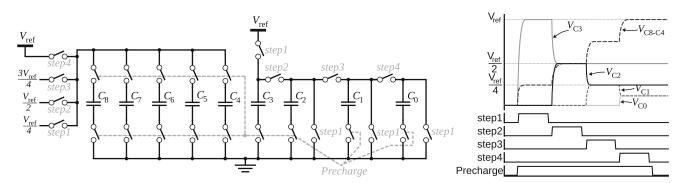

Figure 3 shows a basic implementation of this stepwise charging scheme. A bank of N equidistant voltage supplies is used, for an N-step pre-charge. To charge the load capacitance to V, all the sources are connected in succession to the load, in a non-overlapping manner.

For each charge step of  $\frac{V}{N}$ , the dissipation on the switch is given by,

Fig. 3 Pre-charge cycle schematic diagram

$$E_{S, step} = \frac{1}{2} C \frac{V^2}{N^2}.$$

(3)

The energy lost in the switch for the complete charge cycle is equal to

$$E_{S, stepwise} = N \cdot E_{S, step} = \frac{E_S}{N}. \tag{4}$$

Therefore, it is N times smaller than in the conventional 1-step charging. Putting it all together, the total energy dissipated in the pre-charge process is

$$E_{T,stepwise} = \frac{E_S}{N} + E_C. \tag{5}$$

These calculations exclude the energy required by the logic circuit overload necessary to perform multiple steps charging. The benefits and drawbacks of this implementation technique are discussed in Sect. 3.

#### 3 Circuits implementation

In this section, we will plunge deeper in the circuit level implementation of each one of the blocks that together make up the proposed SAR ADC. The low energy nature of the proposed ADC also implies an low average power. This is typically achievable eliminating any source of static power. An energy-efficient circuit must be able to dissipate power only when doing something useful, and the standby power needs to be small compared to active power. All the circuits that are presented here satisfy these requirements, providing an ADC where the power consumption is a linear function of sampling rate for a wide range of operation.

#### 3.1 Capacitive array

In this presented topology, size of the capacitive array is limited by two factors: noise and mismatch. For the given accuracy, mismatch is the dominating factor over noise, and dictates the minimum size of the binary weighted capacitors matrix. The capacitors are implemented with metal-insulator-metal layers, available in the process.

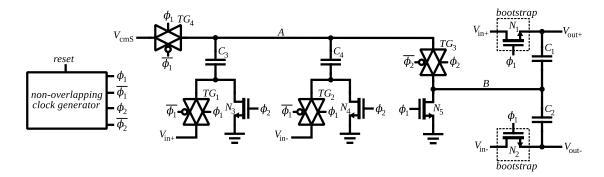

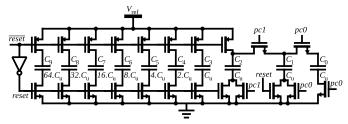

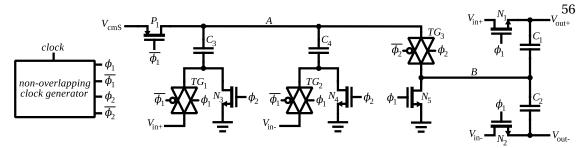

In order to satisfy linearity constraints, the MSB capacitor is sized to meet the constraint  $3\sigma_{INL} < 1$ , where  $\sigma_{INL}$  is the standard deviation for integral non-linearity (INL). This corresponds to around 99.73% of the dies satisfying the INL constraints. With the MSB capacitor dimensioned to be 1 pF, minimum values for LSBs are impractical due to technology design rules and low tolerance to charge injection effects from the switches. To avoid this problem, for the 4 LSBs we implemented the circuit proposed in [3] (Fig. 4). This comes at the expense of a more complex pre-charge cycle.

The pre-charge cycle can be described as follows. The MSB capacitors  $(C_8-C_3)$  are pre-charged to reference voltage, while the least significant bits capacitors  $(C_2-C_0)$  are discharged. Next, the charge from the  $C_3$  is shared among the LSB capacitances iteratively. When the step2 signal is pulled high, half the charge from  $C_3$  goes to  $C_2$ , since they have the same capacitance value. In the next step, the resulting charge from  $C_2$  is shared with  $C_1$ . The process is repeated for  $C_0$  also, and in the end, the amount of charge in each capacitor is proportional to its weight in the SAR algorithm. This behavior is also shown in the waveforms of Fig. 4.

The increased complexity in the pre-charge cycle does not come at the cost of more complex control logic, as the controller is quite simple, and was implemented using a simple shift register and glue logic generating a sequence of non-overlapping signals. As a further simplification of the controller, energy-smart stepwise pre-charge circuitry uses the same logic control signals used for the LSB capacitors precharging.

The intermediate voltage steps are assumed to be available inside the chip. To keep the energy gain close to the theoretical relation derived before in (5), the intermediate voltage steps would have to be made close to the theoretical steps derived. However, the intermediate steps does not affect any linearity or accuracy aspect of the ADC, being responsible only for increasing the energy

Fig. 4 DAC circuitry

Fig. 5 Pre-charge energy as a function of supply voltage and steps

efficiency. So one can relax the precision of the intermediate steps or even ignore them (tie to ground) towards reduced design complexity, paying with a increased power consumption.

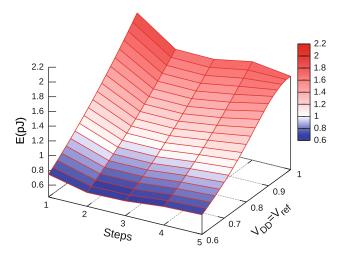

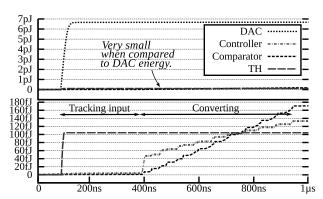

Figure 5, plots the total energy spend on the pre-charge cycle as a function of supply voltage and number of steps. The measured energy includes the energy consumed for the *N*-step capacitors divider network, logic overhead, level converters and of course the DAC itself. One can see that it is not a linear function of the number of steps. This is because the introduction of more voltage steps increases the number of the level converters, the register width, and the controller complexity. Unfortunately the the power consumption of level converters is not a linear function of the supply voltage.

#### 3.2 Input sample and hold

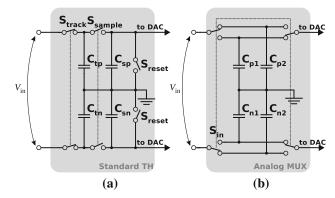

The sampling circuit in our architecture has a distinct advantage over the work in [3]. Consider the schematic shown in Fig. 6(a), representing the standard approach in [3] for tracking and holding the input signal on CS ADCs. Initially, the switch  $S_{track}$  is closed, while  $S_{sample}$  is opened. This way, the input signal is tracked by capacitors  $C_{tp}$  and  $C_{tn}$ . When a conversion is requested,  $S_{track}$  is opened and S<sub>sample</sub> is closed after some short delay (non-overlapping control signals). Tracking and sampling capacitors are made the same size, and half the charge held in  $C_t$  is transferred to  $C_s$ . Switch  $S_{sample}$  is opened again, and the charge in  $C_s$  is used for the ADC conversion. Note that since  $C_{sp}$  and  $C_{tp}$  are not tied together anymore,  $S_{track}$  can be closed again and start tracking  $V_{in}$  early in preparation for the next conversion cycle. The settling time is not a critical factor anymore, relaxing any requirement for the switches, and more importantly, avoiding an opamp for the input signal.

Fig.  $\mathbf{6}$  Track and hold schemes. a Standard approach. b Novel input multiplexer sampling approach

One caveat of this topology is the voltage swing of the sampling circuit. Since the charge is divided between  $C_t$  and  $C_s$ , the voltage swing available for processing is half the voltage swing on the input. This reduces the signal to noise ratio (SNR) on the DAC.

The size of the capacitors on the standard approach, is a function of the size of the DAC capacitors, which in turn are limited by noise and mismatch. To maintain the binary weight relations during the conversion steps, the charge kept on the MSB capacitance of the DAC ( $C_{MSB}$ ) must be half the charge kept on  $C_s$ , if the input sampled was full scale signal,

$$\frac{Q_{sampled}}{2}\bigg|_{V_{in}=V_{ref}} = C_{MSB} \cdot V_{ref} \tag{6}$$

since just half the charge tracked on the input is transferred to the sampling capacitor,

$$Q_{sampled} = \frac{Q_{tracked}}{2} \tag{7}$$

Looking at the circuit in Fig. 6(a), one can see that the charge is tracked on the two capacitors  $C_{tp} = C_{tn}$ . However, the capacitance seen from the input is  $\frac{C_{tp}}{2}$ , and then

$$Q_{tracked} = \frac{C_{tp}}{2} V_{ref} \bigg|_{V_{in} = V_{ref}} \tag{8}$$

Combining (6), (7) and (8) results in,

$$C_{tp} = C_{tn} = C_{sp} = C_{sn} = 8C_{MSB}$$

(9)

Next consider our novel multiplexer sampling scheme shown in Fig. 6(b). The circuit works as follows. Initially, one capacitor pair is tracking the input, while the other one is tied to the DAC. So, when a conversion starts, the capacitor pairs switch roles, and the tracked input signal is fed to the DAC for further processing, while the other capacitor pair starts tracking the input signal again. In doing so, we have maintained the benefits of the standard

track and sample circuitry; the constraints on the switches are relaxed due availability of longer settling time, and the absence of the opamp to buffer the input signal. However, in our design, the voltage swing for the sampled signal is the same that of the input signal, therefore resulting in an improvement in the SNR. To appreciate the benefit of this we need to examine the size necessary for the sampling capacitances. Having the same relation as in (6) the sampled charge is given by,

$$Q_{sampled} = Q_{tracked} \tag{10}$$

Now, combining (6), (8) and (10), it leads to (11).

$$C_{p1} = C_{n1} = C_{p2} - C_{n2} = 4C_{MSB} (11)$$

Reducing the input capacitance by half results in 50% area saving in the input capacitance, which is responsible for the larger area portion in this type of converter. Also, there is no need for a reset on the sampling capacitor; as the charge left from earlier conversions just present as an energy gain, since less energy must be drawn from the input signal for the sampling.

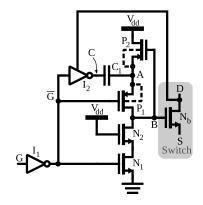

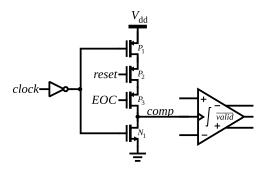

#### 3.3 Comparator

From the energy point of view, the comparator must consume very little or no power while not performing a comparison. The other requirements include a minimum offset, since the CS SAR is much more sensitive to this non-ideality as it manifest as non-linearity. Moreover, the noise will limit the size and power consumption of the comparator. As a design trade-off, the noise was kept under quantization noise, as in (12), following the design guidelines for dynamic comparators and estimation techniques presented in [7, 9].

$$P_{noise} < \frac{\left(V_{LSB}\right)^2}{12} \tag{12}$$

As discussed before, unlike conventional active CR SARs, this ADC topology has it linearity performance degraded due to comparator offset. To rectify this problem the comparator topology chosen for this design has a programmable binary array of capacitors which has been used for the purpose of offset calibration. A binary search for the optimal point permits the offset to be kept under very low voltage levels (hundreds of  $\mu V$ ). The comparator offset is very sensitive to the common-mode (CM) voltage in its input terminals. Although, the ADC topology guarantees that the CM fed into the comparator is the same of the input sampled signal for every conversion cycle. Thus, if the input CM is kept constant, the offset is also kept constant. Moreover, the simulations show that, for the 9-bit converter, temperature and voltage supply variations cause just subtle variation on the offset and does not lead to significant non-linearity in the

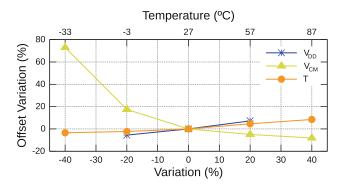

**Fig. 7** Percent offset deviation as function of percent change in  $V_{DD}$  and  $V_{CM}$  and absolute temperature T, normalized for typical operation conditions  $V_{DD}=1.8~\rm{V},~V_{CM}=450~\rm{mV}$  and  $T=27^{\circ}\rm{C}$

ADC. Then, if the input CM is made constant, the calibration procedure is performed just once before the start of circuit operation. In Fig. 7 we plot the standard deviation of the variation on the offset voltage after calibration as function of the supply voltage  $V_{DD}$ , the CM voltage  $V_{CM}$  and the temperature. The results are extracted from Monte-Carlo simulations and normalized for the typical operating conditions:  $V_{DD} = 1.8 \text{ V}$ ,  $V_{CM} = 450 \text{ mV}$  and at the temperature of 27°C.

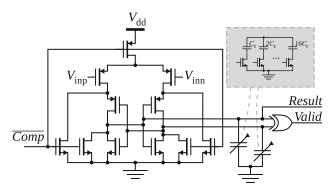

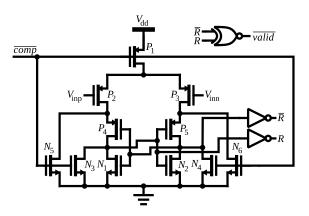

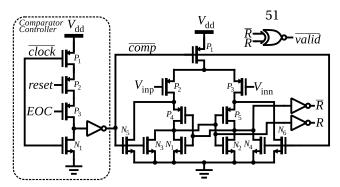

The topology chosen is shown in Fig. 8.

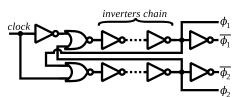

#### 3.4 Control Logic

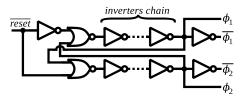

For the execution of the SAR conversion algorithm, a digital control block is needed. In the conventional synchronous SAR topologies, the frequency of the clock signal is, at least, N (number of bits) times faster than the sampling rate. This is required because the algorithm works iteratively, with N comparisons and decisions. For our work, we need additional clock cycles for the pre-charging scheme. The number of additional cycles needed due to the iterative pre-charge is equal to the number of DAC pre-charge steps. This work employs a 4-step pre-charge scheme, that are executed while the input signal is tracked. Therefore, the designed ADC requires a total of 13 clock

Fig. 8 Comparator schematic

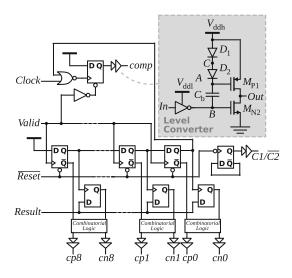

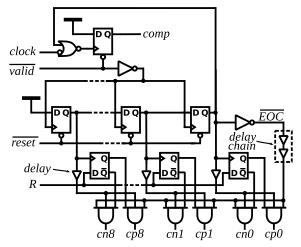

Fig. 9 Logic circuit schematic with the level converter

cycles per conversion. With no step-wise pre-charging the number of conversion clock cycles reduces to 10. In terms of maximum sampling frequency, the actual 5 MSps would increase to 6.5 MSps if no step-wise pre-charge was employed.

A simplified schematic of the logic block implementation is shown in Fig. 9. The switching power dissipated by a digital circuit using static CMOS gates is approximated as [10],

$$P_{SW} = C \cdot V^2 \cdot f \tag{13}$$

with C the total capacitance switched per clock cycle, V the supply voltage and f the switching frequency. So, there is a significant power saving in reducing the supply voltage. Also, the short-circuit power and leakage currents reduce at lower supply voltages, specially in the situation where voltage swing is less than the sum of P and N transistor thresholds. For this reason, low power MOS technology with higher threshold voltages have been employed. In applications where energy is critical, one can scale down digital supply voltage and accept a slower circuit operation. However, scaling down the supply for the whole circuit increases the DAC (capacitive matrix) noise sensitivity, with an effect on the resolution of the ADC. One solution is to use a higher supply voltage for the DAC and a scaled down voltage for digital controller. For this to work across the interfaces, we have employed voltage shifters to connect the digital controller and the ADC. The topology chosen was proposed in [5], and shown together with the logic circuit in Fig. 9.

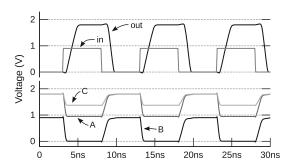

The circuit performs voltage shifting as follows: considering the input node transitions from high to low level; node B at the output of the inverter transitions to  $V_{DD_L}$ , switching node A to  $V_{DD_H} - 2 \cdot V_{diode} + V_{DD_L} \approx V_{DD_H}$ , due to bootstrap effect across the  $C_b$  capacitor. Note that  $C_b$  was already

**Fig. 10** Voltages levels during level conversion, with  $V_{DD_L} = 900 \text{ mV}$

charged to  $V_{DD_H} - 2 \cdot V_{diode}$  before the transition. After, the transition diodes  $D_1$  and  $D_2$  are reverse biased, and gate of  $M_{P1}$  is tied to  $V_{DD_H}$ , turning this transistor off.  $M_{N2}$  is on because of the inverter, and the output node is pulled down to ground. During this process, bootstrap capacitor is charged to  $V_{DD_H} - V_{DD_L}$ . When input node transitions to high, node B will pull to ground, turning the diodes on, and causing the voltage at node A to settle to  $V_{DD_H} - 2 \cdot V_{diode}$ .  $M_{N2}$  turns off, and  $M_{P1}$  pulls up output node to  $V_{DD_H}$ , and the bootstrap capacitor voltage charges to  $V_{DD_H} - 2 \cdot V_{diode}$ . The whole process is energy efficient and the circuit does not show static power consumption. Figure 10 plots the voltages waveforms during the operation of the ADC. The input is switched at a frequency of 100 MHz in the plot.

The limit on the voltage scaling in the digital voltage supply is set by the minimum voltages required at the input of voltage level-converters, and needed for the proper operations of the logic gates. Table 1 shows the propagation delays from  $V_{DD_L}$  to  $V_{DD_H}$  for transition from 0 to 1 and 1 to 0 in the level-converter. The propagation delay grows exponentially as the value of  $V_{DD_L}$  drops, and the circuit is unusable for the ADC sampling at 5 MSps when  $V_{DD_L}$  drops below 0.8 V. With a digital supply of 900 mV, power dissipation (with level converters included) for the same sampling rate is more than twice smaller than using the typical 1.8 V.

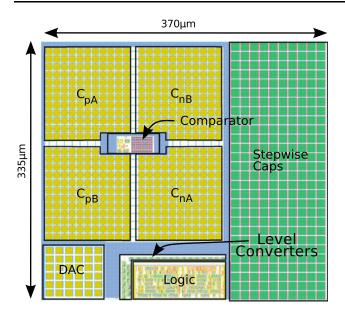

#### 4 Layout

In Fig. 11 we present the proposed layout for the ADC, with some routing omitted for clarity. The input capacitors

**Table 1** Delays as function of  $V_{DD_L}$

| $\overline{V_{DD_L}}$ | $t_{d,0 ightarrow1}$ (ns) | $t_{d,1 ightarrow0}$ (ns) |

|-----------------------|---------------------------|---------------------------|

| 0.9                   | 1.27                      | 1.62                      |

| 0.8                   | 1.43                      | 3.04                      |

| 0.7                   | 1.82                      | 9.45                      |

| 0.6                   | 3.75                      | 62.09                     |

Fig. 11 Proposed layout

were placed in a common-centroid form, in order to reduce the effects of fabrication gradients. The DAC just occupies a small portion of the whole design. The logic controller, surrounded by the voltage shifters on the layout, was designed using standard cells methodology. Stepwise capacitors, even though have a much larger capacitance than the input capacitors, have a total area not much larger than one third of the whole ADC area. This was possible because we used MOS transistor thin oxide for their implementation. The dimensions are shown in the figure, and the total area is 0.124 mm<sup>2</sup>.

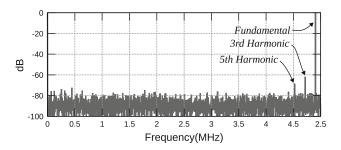

Fig. 12 FFT plot with the input near Nyquist frequency

#### **5** Simulation results

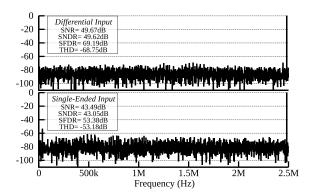

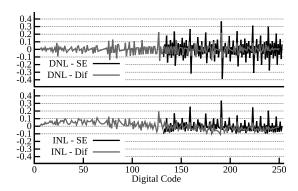

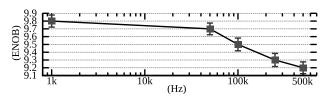

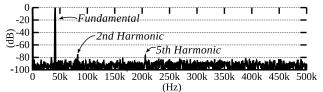

In order to characterize and measure converters performance, a set of simulations were performed. A 0.8 V peak-to-peak input signal with a frequency of about 2.45 MHz was applied to the converter, with a sampling frequency of 5 MSps. This rate was achieved with a clock frequency of 65 MHz. Transient noise had been included in the simulation, in order to account for thermal noise. Transient noise feature has been used before, as in [2] to determine an ADC performance. Since transient noise simulation relies on statistical data, 10 runs has been performed. Also, packaging parasitics were included to the extracted layout, to achieve a more accurate test condition.

A total of 4,096 samples per run has been simulated, and the FFT frequency spectrum for one of these runs is shown in Fig. 12, with more significant harmonics. An effective number of bits (ENOB) mean  $\mu_{ENOB}$  of 8.45 is achieved (with the standard deviation  $\sigma_{ENOB} = 0.02$ ), reflecting a mean signal to noise and distortion ratio of 52.63 dB. Third and fifth harmonics are 61.76 and 68.51 dB under the fundamental signal, respectively, for this run.

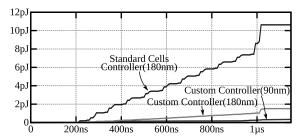

Under the test conditions, power is distributed among the blocks as follows; the largest power consumption comes from the logic controller, contributing to 41.5% of the consumption of the whole chip. The next dominant component of power dissipation comes from the comparator, with 39.21%. The reference voltage circuitry and the voltage shifter array contribute 13.86 and 1.5%, respectively. The input signal drains the other 3.93% of the power needed for the circuit operation. The total power consumed is 54.2  $\mu W$ .

A common figure of merit (FOM) in ADCs, is expressed in terms of energy necessary per conversion step, and is expressed as,

$$FOM = \frac{P}{2^{ENOB}F_{s}} \tag{14}$$

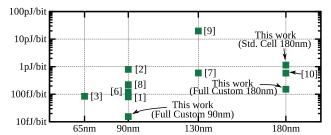

with P being the total power consumed by the circuit and  $F_s$  the sampling frequency. The converter designed achieves a mean FOM of 31 fJ/conv. step. Table 2 shows a comparison between recent SAR ADC works and our design.

Table 2 Comparison with state-of-the-art designs

| Parameter           | [3]     | [4]       | [14]     | [13]   | [1]      | [6]     | This work |

|---------------------|---------|-----------|----------|--------|----------|---------|-----------|

| Technology (nm)     | 90      | 140       | 180      | 65     | 180      | 90      | 180       |

| Bits                | 9       | 12        | 12       | 10     | 10       | 8       | 9         |

| ENOB                | 7.8     | 10.99     | 10.55    | 8.75   | 9.4      | 7.8     | 8.45      |

| Sampling rate       | 50 MSps | 6.25 kSps | 100 kSps | 1 MSps | 100 kSps | 10 MSps | 5 MSps    |

| FOM (fJ/conv. step) | 65      | 66        | 167      | 4.4    | 56       | 30      | 31        |

#### 6 Conclusion

We have presented a extremely energy-efficient ADC. The limits of the current SAR topology were pushed towards the maximum power saving employing several innovative design techniques. The achieved results are close to similar designs in more advanced silicon processes. The use of a non-state-of-the-art mature 0.18  $\mu$ m technology, can also reduce the production cost.

#### References

- Agnes, A., Bonizzoni, E., Malcovati, P., & Maloberti, F. (2008). A 9.4-ENOB 1 V 3.8 μW 100 kS/s SAR ADC with time-domain comparator. In *Proceedings of IEEE international solid-state circuits conference (ISSCC)*, Digest of Technical Paper, Feb (pp 246–610). San Francisco, CA, USA. doi:10.1109/ISSCC.2008.4523149.

- Cheon, J., & Han, G. (2008). Noise analysis and simulation method for a single-slope ADC with CDS in a CMOS image sensor. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 55(10), 2980–2987. doi:10.1109/TCSI.2008.923434.

- Craninckx, J., & Van der Plas, G. (2007). A 65 fJ/conversion-step 0-to-50 MS/s 0-to-0.7 mW 9b charge-sharing SAR ADC in 90 nm digital CMOS. In *Proceedings of IEEE international* solid-state circuits conference (ISSCC), Digest of Technical Paper, Feb (pp 246–600). San Francisco, CA, USA. doi:10.1109/ ISSCC.2007.373386.

- De Venuto, D., Castro, D. T., Ponomarev, Y., & Stikvoort, E. (2010). 0.8 μW 12-Bit SAR ADC sensors interface for RFID applications. *Microelectronics Journal*, 41, 746–751. doi:10.1016/j.mejo.2010.06.019.

- Garcia-Montesdeoca, J., Montiel-Nelson, J., & Nooshabadi, S. (2009). High performance bootstrapped CMOS dual supply level shifter for 0.5 V input and 1 V output. In *Proceedings of 12th Euromicro conference on digital system design, architectures, methods and tools*, DSD, Aug (pp 311–314). Patras, Greece. doi:10.1109/DSD.2009.180.

- Harpe, P., Zhou, C., Wang, X., Dolmans, G., & de Groot, H. (2010). A 30 fJ/conversion-step 8b 0-to-10 MS/s asynchronous SAR ADC in 90 nm CMOS. In *Proceedings of IEEE international solid-state circuits conference (ISSCC)*, Digest of Technical Paper, Feb (pp 388–389). San Francisco, CA, USA. doi:10.1109/ISSCC.2010.5433967.

- Kim, J., Leibowitz, B., Ren, J., & Madden, C. (2009). Simulation and analysis of random decision errors in clocked comparators. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 56(8), 1844–1857. doi:10.1109/TCSI.2009.2028449.

- Lee, S. K., Park, S. J., Suh, Y., Park, H. J., & Sim, J. Y. (2009). A

1.3 μW 0.6 V 8.7-ENOB successive approximation ADC in a

0.18 μm CMOS. In Symposium on VLSI circuits (pp 242–243).

- Nuzzo, P., De Bernardinis, F., Terreni, P., & Van der Plas, G. (2008). Noise analysis of regenerative comparators for reconfigurable ADC architectures. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 55(6), 1441–1454. doi:10.1109/TCSI.2008.917991.

- Rabaey, J. (2009). Low power design essentials (1st ed.). New York, NY: Springer Publishing Company, Incorporated.

- Scott, M., Boser, B., & Pister, K. (2003). An ultra low-energy ADC for smart dust. *IEEE Journal of Solid-State Circuits*, 38(7), 1123–1129. doi:10.1109/JSSC.2003.813296.

- Svensson, L. J., & Koller, J. (1994). Adiabatic charging without inductors. In *Proceedings of international workshop on low*power design, April (pp 159–164). Napa, CA, USA.

- van Elzakker, M., van Tuijl, E., Geraedts, P., Schinkel, D., Klumperink, E., & Nauta, B. (2008). A 1.9 μW 4.4 fJ/conversion-step 10b 1 MS/s charge-redistribution ADC. In *Proceedings* of *IEEE international solid-state circuits conference (ISSCC)*, Digest of Technical Paper, Feb (pp 244–610). San Francisco, CA, USA. doi:10.1109/ISSCC.2008.4523148.

- Verma, N., & Chandrakasan, A. (2007) An ultra low energy 12-bit rate-resolution scalable SAR ADC for wireless sensor nodes. *IEEE Journal of Solid-State Circuits*, 42(6), 1196–1205. doi:10.1109/JSSC.2007.897157.

Taimur Gibran Rabuske was born in Rio Grande do Sul, Brazil. He received the BS degree in Electrical Engineering from Universidade Federal de Santa Maria (UFSM), Brazil, in 2009, and is currently pursuing the MSc degree at the same institution. From July December 2009, he was an intern at Gwangju Institute of Science and Technology (GIST), in Gwangju, South Korea, and from July 2010 to July 2011, he was a visiting

researcher at Instituto de Engenharia de Sistemas e Computadores—Investigação e Desenvolvimento (INESC-ID), in Lisbon, Portugal. His research interests include design and optimization of analog and mixed-signal circuits, ultra-low power circuits, data converters and design methodologies.

Saeid Nooshabadi received the MTech and PhD degrees in Electrical Engineering from the Indian Institute of Technology, Delhi, India, in 1986 and 1992, respectively. Currently, he is the Professor of Computer Systems Engineering, having a joint appointment, with the Department of Electrical and Computer Engineering, and the Department of Computer Science, Michigan Technological University, Michigan. Prior to his current appointment he has

held multiple academic and research positions. His last two appointments were with the Department of Information and Communications, Gwangju Institute of Science and Technology, Republic of Korea (2007–2010), and with the School of Electrical Engineering and Telecommunications, University of New South Wales, Sydney, Australia (2000–2007). His research interests include VLSI information processing and low-power embedded processors.

Ramos Rodrigues Cesar received the BS in Electrical Engineering from Federal University of Santa Maria (UFSM) in 1987, and obtained master and doctor degrees from State University of Campinas (Unicamp, 1991 and 1993). He's currently working at UFSM and his activities comprehend: lecturing (Electrical and Electronic Materials, Analog Design) graduated students supervision, and projects management. The research topics of his interest include:

analog and mixed signal IC design, and engineering education.

# 4 ARTIGO II: A 5MSps $13.25\mu$ W 8-BIT SAR ADC WITH SINGLE-ENDED OR DIFFERENTIAL INPUT

RABUSKE, T. G.; RODRIGUES, C. R.; NOOSHABADI, S. A 5MSps 13.25 $\mu$ W 8-bit SAR ADC with Single-Ended or Differential Input. **Microelectronics Journal**, Elsevier. Inpress.

#### A 5MSps 13.25 $\mu$ W 8-bit SAR ADC with Single-Ended or Differential Input

Taimur Gibran Rabuske<sup>a,1</sup>, Cesar Ramos Rodrigues<sup>a,2</sup>, Saeid Nooshabadi<sup>b,3</sup>

<sup>a</sup> Federal University of Santa Maria (UFSM), Santa Maria, Brazil <sup>b</sup> Michigan Technological University (MTU), Houghton, MI, 49931, USA

#### **Abstract**

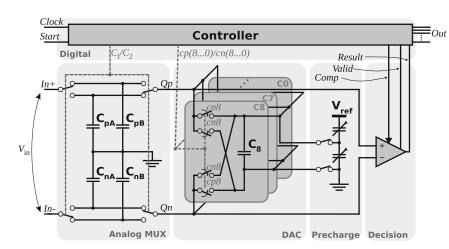

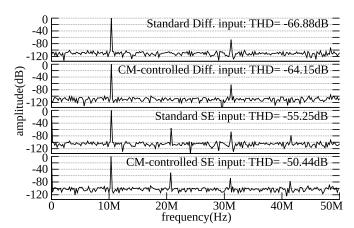

An ultra-low energy analog-to-digital converter (ADC) able to process single-ended and differential signals, with a flexible wide-range common-mode voltage is presented. This ability has been made possible through a novel track-and-hold (TH) circuitry, which provides a differential output with a fixed common mode voltage for the ADC, and relies on switched-capacitors technique for operation. The ADC is designed in a 90nm technology and simulated for both single-ended and differential inputs. The ADC consumes  $13.25\mu$ W from a 1V source, while providing 6.86 and 7.95 effective bits, when acquiring single-ended and differential signals, respectively. The proposed technique contributes to improve power consumption and compactness, eliminating the requirements of a power-hungry amplifier and external components.

Keywords: ADC, ultra-low power, SAR, single-ended to differential conversion.

#### 1. Introduction

A tight power budget is present in an ever increasing range of applications. New trends and emerging technologies often focus on miniaturization and portability, bringing devices which are mostly battery-powered. Therefore, in order to increase battery lifetime, every block in a system in this environment must consume the minimum possible energy.

One required circuit for a wide range of low-power applications is the analog-to-digital converter (ADC). Among the diversity of available topologies, the successive approximation register (SAR) is well-known for its energy efficiency. It is very attractive in applications which demand low data-rates, with tight power constraints, mainly due to the logarithmic dependence of architecture on the resolution. Based on a feedback loop, the SAR converter converges iteratively to the final digital word, comparing the value of a digital-to-analog converter (DAC) to a sampled representation of the input signal, captured by a track-and-hold (TH) circuit. The conversion cycle is guided by the binary search algorithm.

Conventional SAR ADCs rely on the charge redistribution (CR) method, so-called due to the DAC topology they employ. In this approach, the capacitive DAC is also used as tracking circuit, and at every step of the conversion, one of the binary-weighted capacitors is tied to ground or reference terminal, leading the error voltage to diminish towards zero.

In [1], the authors present a method to implement a capacitive SAR based on charge sharing (CS), rather than CR. As an advantage, the DAC is totally pre-charged once in the beginning of a conversion cycle, instead of per bit active in-

teractions with the supply lines. Moreover, the settling requirements for DAC can be relaxed during design cycle, and most importantly, avoiding any power-hungry opamp buffering the reference signal. Misleadingly, this opamp is often not accounted for in the energy measurement of the CR converters, which could be significant.

Additionally, three common structures exist for the construction of ADCs: fully-differential input, pseudodifferential input, and single-ended (SE) input [2]. The input signal source (e.g. sensor) and the ADC structure must be consistent, imposing severe limitations on the choice of ADC in a given application. Performing the signal processing of the sampled signal, past the TH block, differentially presents some advantages over the single-ended processing, including increased noise rejection and dynamic range. However, most sensors and transducers only produce a single-ended output or a differential output with an incompatible common-mode (CM) voltage with that of the succeeding signal processing block. Traditionally, in order to match the signal types, designers have been relying on more complex coupling circuits, that may include electromagnetic transformers [3] or powerhungry programmable amplifiers [4].

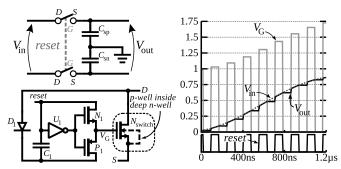

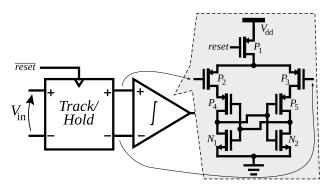

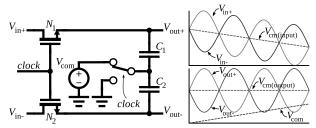

We present a novel TH circuit that is able to maintain a desired stable CM voltage at its output, independent from the changes at the input CM voltage. This is a significant circuit design advantage when the TH is connected to a circuit block (e.g. comparator) that requires a stable CM voltage for its proper operation. Another advantage of these circuits is that it readily performs TH on both single-ended and differential voltage inputs, yet producing differential output around the desired output CM voltage.

This paper presents the design of a SAR ADC based on the CS principle, that employs the proposed novel TH. Thus, the ADC is very flexible in terms of input signal type, allow-

<sup>&</sup>lt;sup>1</sup>taimurgibran@ieee.org

<sup>&</sup>lt;sup>2</sup>cesar@ieee.org

<sup>&</sup>lt;sup>3</sup>saeid@mtu.edu

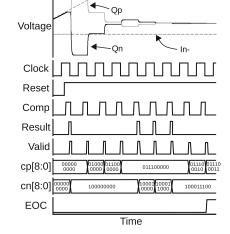

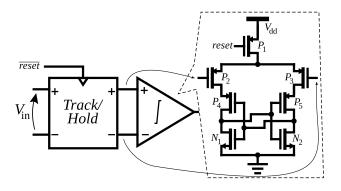

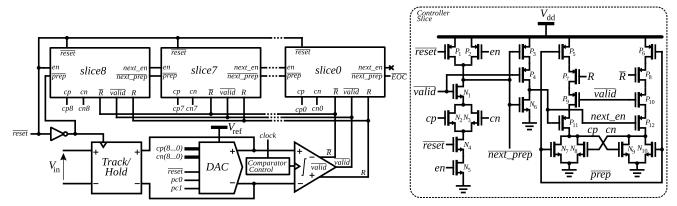

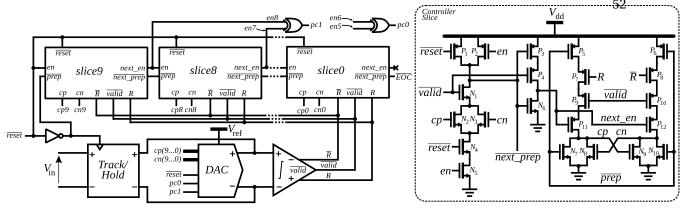

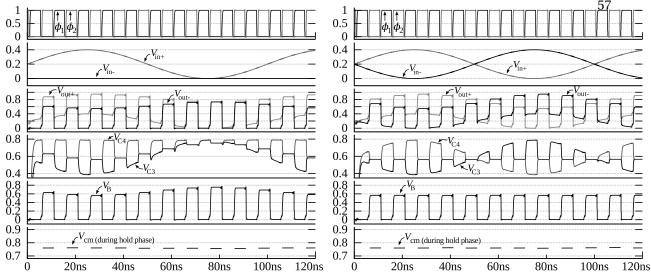

Figure 1: Charge Sharing ADC blocks diagram and illustrative waveforms

ing the conversion of signals coming from a wide range of sources, and yet eliminating the requirement of any matching circuitry.

Section 2 describes the ADC architecture. In Section 3 we present a background on TH circuits, the motivation for the proposed novel circuit, its topology derivation and implementation. In Section 4, we show in detail the circuit implementation of the remaining blocks of the ADC. The simulation results are presented in Section 5, and Section 6 finally concludes this work.

#### 2. ADC Working Principle

The employed CS-based architecture comprises a controller, a comparator, a switched capacitor DAC and a TH circuitry, as depicted in Fig. 1. Moreover, the circuit is differential to increase noise tolerance and dynamic range [5].

A conversion cycle begins on the falling edge of the  $\overline{reset}$  input. While this input is low, the TH circuit is tracking the input, and the DAC is being pre-charged. For the 8-bit converter, the DAC consists of 8 binary-weighted capacitors. During the pre-charge cycle, these capacitors are tied to reference voltage  $V_{\rm ref}$ , and disconnected from TH capacitors and from each other. When  $\overline{reset}$  is returned to high logic level, the input signal tracked on the TH is held steady, and DAC is disconnected from  $V_{\rm ref}$ .

Next, the SAR circuit starts performing the binary search algorithm adding or subtracting charge to or from the sampling capacitors. Triggered by the logic controller, the comparator is requested to compare voltages  $V_p$  and  $V_n$ . The comparison result is the most significant bit (MSB) of the actual conversion. Subsequently, some charge must be added to or subtracted from these nodes, in order to make the voltage difference (error voltage) between  $V_{\rm p}$  and  $V_{\rm n}$  smaller. If, for instance,  $V_{\rm p}$  is evaluated larger than  $V_{\rm n}$ , we remove an MSBequivalent (one half) amount of charge from sampling capacitors, by turning on control signal cn7. Therefore, capacitor  $C_7$  would be connected anti-parallel to the capacitors of TH,  $C_{\rm sp}$  and  $C_{\rm sn}$ . If, on the other hand,  $V_{\rm p}$  is smaller than  $V_{\rm n}$ , the same amount of charge should be added placing  $C_7$ in parallel to the sampling capacitances, by turning the control signal cp7 on. The process progressively repeats for the other bits, adding to or subtracting charge from the sampled

charge from  $V_{\text{in}}$ . At the end, cn(7...0) represents the desired 8-bit output.

#### 3. Track and Hold Circuit

#### 3.1. TH Background

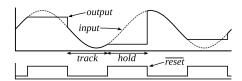

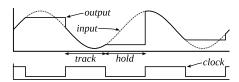

Fig. 2 presents two operation phases of the *reset* signal in an ideal TH circuit. In the tracking phase, the circuit works like a closed switch, passing the input signal to the output, ideally not affecting it. During the hold phase, the magnitude of the input, captured in in the preceding phase, is kept steady until the next tracking phase. Also, during hold phase the circuit block that feeds from TH processes the sampled signal. An ideal TH has a zero output impedance, and an infinite input impedance.

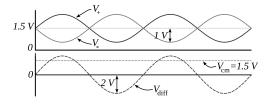

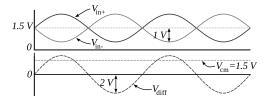

In differential signaling, there are two quantities of primary interest (see Fig. 3). The first is the differential amplitude itself, that is given by

$$V_{\text{diff}} = V_+ - V_- \tag{1}$$

where  $V_+$  and  $V_-$  are the analysed signal amplitudes.

The other quantity is the common-mode voltage  $V_{\rm cm}$  which is the DC offset of the signal, or in other words, the mean amplitude of  $V_+$  and  $V_-$ , as given by

$$V_{\rm cm} = \frac{V_+ + V_-}{2}.$$

(2)

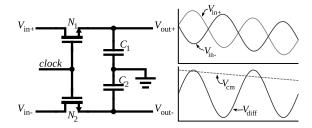

The CM voltage sets the operating point of the circuits. As an example, Fig. 4 shows the case where the TH feeds a comparator directly (e.g. 1-bit ADC). In this circuit the transconductance of the transistors in the differential pair at the comparator input, is set by the CM voltage of the TH circuit. The transconductance parameter determines some of the performance metrics of the comparator, such as speed, offset and

Figure 2: Working principle of a TH

Figure 3: Decomposition of differential and common-mode levels in a differential signal

noise susceptibility [6, 7] and, therefore, should remain stable for every comparison.