### UNIVERSIDADE FEDERAL DE SANTA MARIA CENTRO DE TECNOLOGIA ENGENHARIA DE COMPUTAÇÃO

## PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO EM TECNOLOGIAS CMOS

TRABALHO DE CONCLUSÃO DE CURSO

Raphael Andreoni Camponogara Viera

Santa Maria, RS, Brasil

# PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO EM TECNOLOGIAS CMOS

### Raphael Andreoni Camponogara Viera

Trabalho de Conclusão de Curso apresentado ao curso de Engenharia de Computação da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para a obtenção do grau de

Engenheiro de Computação

Orientador: Prof. Dr. César Augusto Prior

Santa Maria, RS, Brasil

#### Camponogara Viera, Raphael Andreoni

Projeto e análise de moduladores sigma-delta em tempo contínuo em tecnologias CMOS / por Raphael Andreoni Camponogara Viera. – 2014.

92 f.: il.; 30 cm.

Orientador: César Augusto Prior

Monografia (Graduação) - Universidade Federal de Santa Maria, Centro de Tecnologia, curso de Engenharia de Computação, RS, 2014.

1. Conversão AD. 2. Modulador Sigma-Delta em Tempo Contínuo. 3. Análise de Estabilidade. I. Prior, César Augusto. II. Título.

#### © 2014

Todos os direitos autorais reservados a Raphael Andreoni Camponogara Viera. A reprodução de partes ou do todo deste trabalho só poderá ser feita mediante a citação da fonte.

E-mail: raphael@ieee.org

### Universidade Federal de Santa Maria Centro de Tecnologia Engenharia de Computação

A Comissão Examinadora, abaixo assinada, aprova o Trabalho de Conclusão de Curso

## PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO EM TECNOLOGIAS CMOS

elaborado por Raphael Andreoni Camponogara Viera

como requisito parcial para obtenção do grau de **Engenheiro de Computação**

### **COMISSÃO EXAMINADORA:**

César Augusto Prior, Dr. (Presidente/Orientador)

César Ramos Rodrigues, Dr. (UFSM)

Paulo César Comassetto de Aguirre, Me. (UNIPAMPA)

Santa Maria, 05 de Dezembro de 2014.

#### **AGRADECIMENTOS**

Aos meus pais, Cecília Camponogara Viera e Edison Roberto Costa Viera pelo amor fraternal e incondicional, pelo apoio, confiança e incentivo.

À minha mais cara companheira e amiga Suzane Franciscatto de Paula pela compreensão e suporte. E à sua família pela excelente acolhida e convívio.

Ao colega de laboratório (Gmicro) Jorge de La Cruz pelas valiosas dicas e disposição para auxiliar.

Ao professor João Baptista pela amizade e por ter proporcionado o contato com o projeto de moduladores Sigma-Delta.

Aos Professores Cesar Augusto Prior pela colaboração e sugestões durante o projeto e também pela amizade fora do ambiente acadêmico.

Aos professores Paulo César Comassetto e César Ramos Rodrigues pela análise do trabalho, e trocas de informações ao longo do projeto.

Ao professor André Luiz Aita pela colaboração e críticas sempre construtivas.

Aos professores Marcelino Bicho dos Santos e Jorge Fernandes do Instituto Superior Técnico de Lisboa que mostraram de uma forma bastante interessante o caminho para o projeto de circuitos analógicos.

Ao meu mais caro amigo Alonso Aymone de Almeida Schmidt pela amizade incondicional. E à sua família pela amizade desde a infância.

Aos demais que porventura fizeram parte da minha formação acadêmica.

#### **RESUMO**

Trabalho de Conclusão de Curso Engenharia de Computação Universidade Federal de Santa Maria

## PROJETO E ANÁLISE DE MODULADORES SIGMA-DELTA EM TEMPO CONTÍNUO EM TECNOLOGIAS CMOS

AUTOR: RAPHAEL ANDREONI CAMPONOGARA VIERA ORIENTADOR: CÉSAR AUGUSTO PRIOR Local da Defesa e Data: Santa Maria, 05 de Dezembro de 2014.

Este trabalho apresenta o projeto de moduladores sigma-delta ( $\Sigma\Delta M$ ) em tempo contínuo para sinais com largura de banda do sinal de 0,2 MHz e razão sinal ruído (SNR) de 78 dB, os quais são as especificações para o padrão GSM. São implementados três moduladores singlebit de laço único com filtro do tipo passa-baixa, onde um dos moduladores é de segunda ordem e dois de terceira ordem, sendo que um dos moduladores de ordem superior terá uma função de transferência do ruído (NTF) mais agressiva, desta forma, é feita uma análise sobre a estabilidade e a real performance dos moduladores quando comparados à sua performance ideal. A análise sobre a estabilidade poderá ser aplicada para moduladores sigma-delta em tempo contínuo ou tempo discreto de modo que será utilizada teoria de controle e de filtros. Simulações no nível de abstração do sistema mostram que a arquitetura de segunda ordem apresenta uma razão sinal ruído equivalente ao de terceira ordem quando a estabilidade é considerada. Além disso, várias não idealidades são analisadas de modo a confirmar a robustez do modulador de segunda ordem. Os resultados da implementação elétrica mostram que o modulador de segunda ordem atinge uma SNR superior a dos moduladores de alta ordem devido a outras não idealidades presentes no projeto de circuitos CMOS. Os resultados finais representam uma redução significativa na complexidade do projeto do modulador assim como no consumo de energia. Portanto, este trabalho enfatiza que o projetista deverá avaliar o sistema antes de partir para a implementação baseando-se apenas na equação que prediz a SNR ideal de um modulador sigma-delta, de modo que a implementação de um modulador mais simples poderá resultar em uma performance semelhante.

**Palavras-chave:** Conversão AD. Modulador Sigma-Delta em Tempo Contínuo. Análise de Estabilidade.

#### **ABSTRACT**

Undergraduate Final Work Computer Engineering Federal University of Santa Maria

## DESIGN AND ANALYSIS OF SIGMA-DELTA MODULATORS IN CONTINUOUS TIME IN CMOS TECHNOLOGIES

AUTHOR: RAPHAEL ANDREONI CAMPONOGARA VIERA ADVISOR: CÉSAR AUGUSTO PRIOR Defense Place and Date: Santa Maria, December 05<sup>th</sup>, 2014.

This work presents the design of a continuous time sigma-delta modulator with a 0.2 MHz signal bandwidth and 78 dB signal-to-noise ratio (SNR), which are the specifications for the GSM standard. Three single-loop, single-bit, low-pass modulators are implemented, being one of second order and two of third order, where the one with higher order has a more aggressive noise transfer function. A stability analysis is performed together with the real modulators performance when compared with the ideal one. The stability analysis can be applied for continuous or discrete time modulators since control and filter theory are used. System level results show that the second and third order architectures have equivalents signal-to-noise ratios when stability is considered. Besides, several non-idealities are compared in order to verify the second order modulator robustness. Results from the electrical implementation show that the modulator achieves a superior signal-to-noise ratio than the counterparts due to other non-idealities present in CMOS circuits. Final results reveals a significant reduction in the modulator design and power consumption. Therefore, this work emphasizes that the designer should perform a thorough system analysis before implement the modulator resorting only in the ideal equation that predict the sigma-delta modulator performance in order to verify if a simple architecture could result in a similar performance than a more complex system.

**Keywords:** Analog-to-Digital Converter. Continuous Time Sigma-Delta Modulator. Stability Analysis.

## LISTA DE FIGURAS

| Figura 2. | 1 – Diagrama de blocos generalizado de um conversor A/D do tipo Nyquist                        | 20  |

|-----------|------------------------------------------------------------------------------------------------|-----|

| Figura 2. | 2 – Filtro anti-alias para ADC do tipo Nyquist                                                 | 21  |

| Figura 2. | 3 – Filtro anti-alias para ADC sobreamostrado                                                  | 21  |

| Figura 2. | 4 – Diagrama de blocos de um quantizador <i>single-bit</i>                                     | 22  |

| Figura 2. | 5 – Processo de quantização <i>singe-bit</i>                                                   | 22  |

| Figura 2. | 6 – Erro de quantização <i>singe-bit</i>                                                       | 23  |

| Figura 2. | 7 – Modelo linear de um quantizador com ruído branco                                           | 23  |

| Figura 2. | 8 – Ruído de quantização (a) função densidade de probabilidade (b) densidade                   |     |

|           | de potência espectral                                                                          | 24  |

| Figura 2. | 9 – Efeito de <i>noise-shaping</i>                                                             | 25  |

| Figura 2. | $10$ – Modulador $\Sigma\Delta$ . (a) Diagrama de blocos (b) modelo com aproximação linear.    | 26  |

| _         | 11 – Métricas de performance de um $\Sigma \Delta M$                                           | 29  |

| -         | <u> </u>                                                                                       | 30  |

|           |                                                                                                | 31  |

|           | 1 – Diagrama de blocos de um modulador $\Sigma\Delta$ em tempo contínuo                        | 32  |

| _         | 1 – Diagrama de blocos do modulador. (a) Segunda ordem (b) Terceira ordem                      | 38  |

| _         | 1 – Efeito do <i>jitter</i> no sinal do DAC                                                    | 41  |

| -         | 2 – Modelagem do <i>jitter</i> em Matlab/Simulink®                                             | 41  |

|           | 3 – Efeito do jitter na performance do modulador                                               | 41  |

| -         | 4 – Efeito do ELD no sinal de realimentação do sistema                                         | 42  |

|           | 5 – Modelagem do ELD em Matlab/Simulink®                                                       | 42  |

| _         | 6 – Efeito do ELD na performance do modulador                                                  | 43  |

| _         | 7 – Modelo do integrador RC ativo                                                              | 43  |

| _         | 8 – Efeito do ganho na performance do modulador. (a) Primeiro integrador. (b)                  |     |

| E:        | Segundo integrador                                                                             | 44  |

| Figura 5. | 9 – Efeito do GBW na performance do modulador. (a) Primeiro integrador (b)                     | 4 ~ |

| г         | segundo integrador.                                                                            | 45  |

|           | 10 – Modelagem do integrador em Matlab/Simulink®                                               | 46  |

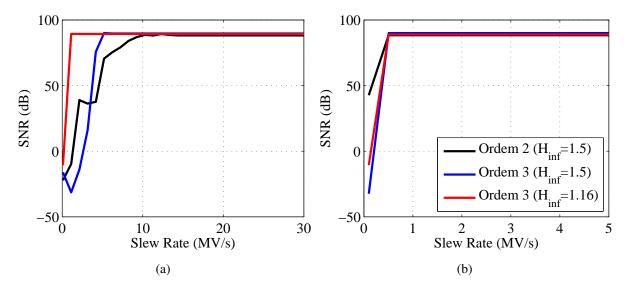

| Figura 5. | 11 – Efeito do SR na performance do modulador. (a) Primeiro integrador (b) segundo integrador. | 47  |

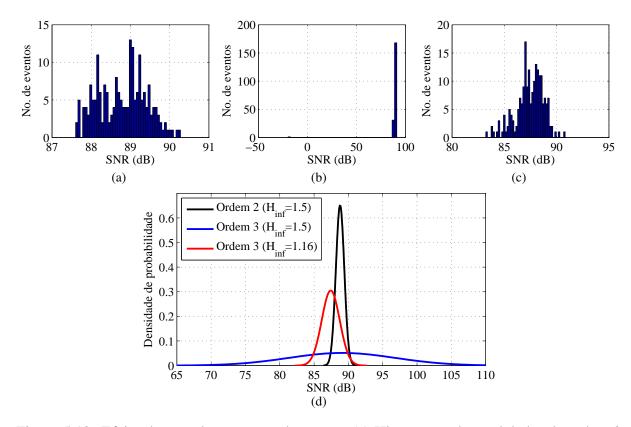

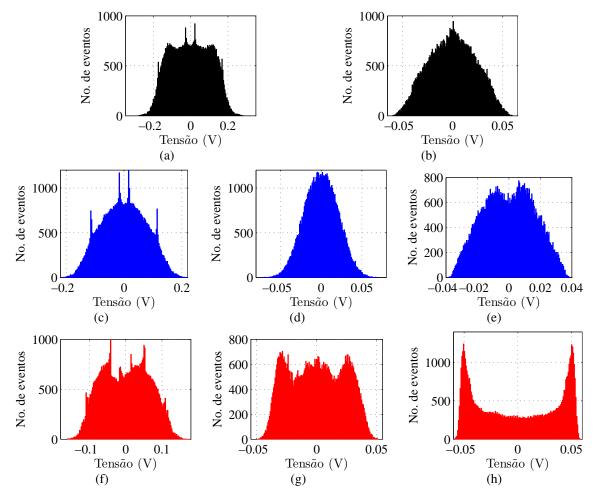

| Figura 5. | 12 – Efeito do erro da constante de tempo. (a) Histograma do modulador de                      |     |

|           | ordem 2 com $\ H\ _{\infty}=1,5$ (b) histograma do modulador de ordem 3 com                    |     |

|           | $\ H\ _{\infty}=1,5$ (c) histograma do modulador de ordem 3 com $\ H\ _{\infty}=1,16$          |     |

|           | (d) distribuição gaussiana normal                                                              | 48  |

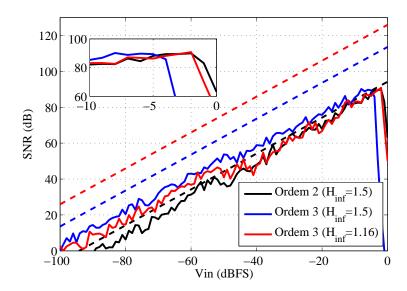

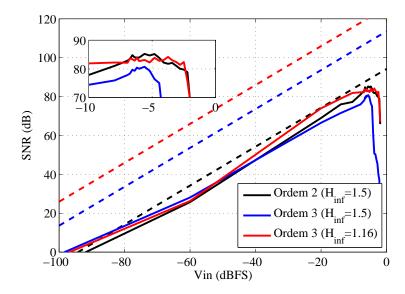

| Figura 5. | 13 – SNR versus amplitude do sinal de entrada. Performance no nível de abstra-                 |     |

|           | ção do sistema                                                                                 | 51  |

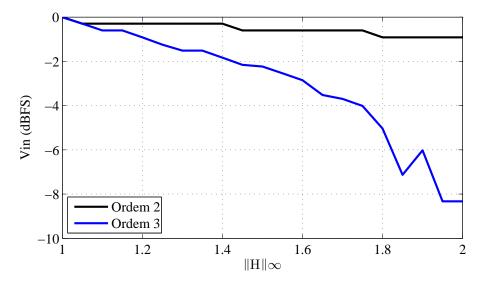

| Figura 6. | 1 – Máxima amplitude estável do sinal                                                          | 53  |

| Figura 6. | 2 – Root Locus                                                                                 | 54  |

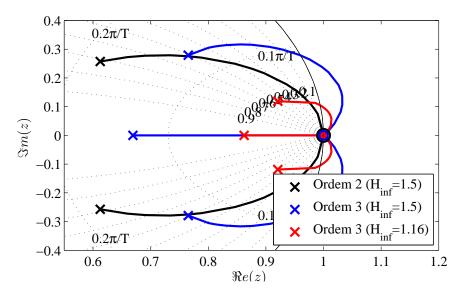

| Figura 6. | 3 – Modulador $\Sigma\Delta$ (a) NTF (b) STF                                                   | 55  |

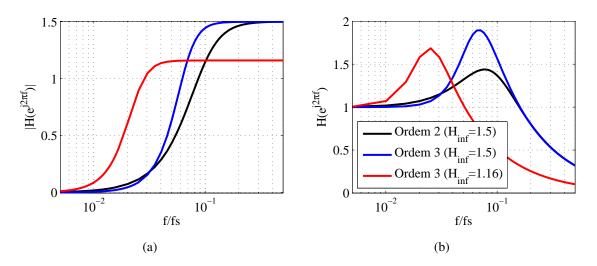

|           | 4 – Critério de estabilidade                                                                   | 56  |

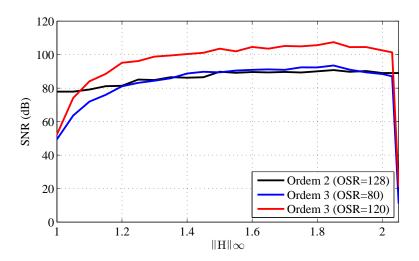

| Figura 7. | 1 – Esquemático do modulador $\Sigma\Delta$ em nível elétrico. (a) Segunda ordem (b)           |     |

|           | terceira ordem                                                                                 | 57  |

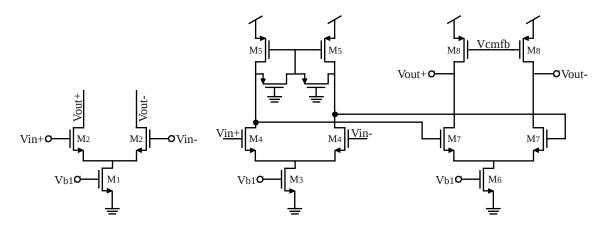

| Figura 7. | 2 – Esquemático amplificador                                                                   | 60  |

|           | 3 – Esquemático do circuito de modo comum                                                      | 60  |

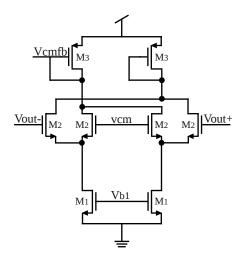

| Figura 7. | 4 – Resposta em frequência. (a) Primeiro amplificador (b) segundo amplificador.                | 61  |

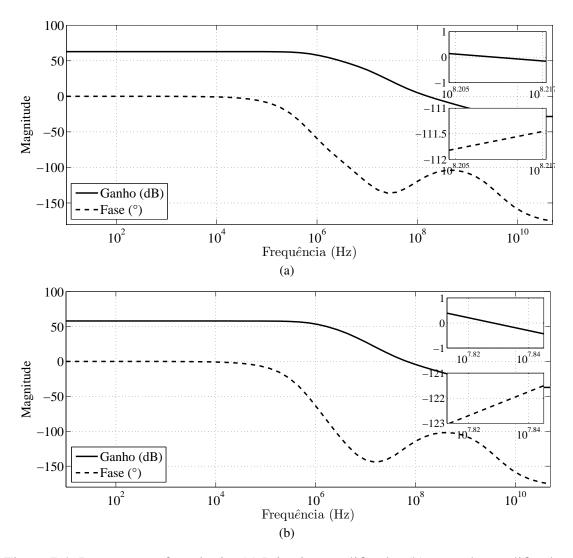

| Figura 7.5 – | Esquemático. (a) Comparador dinâmico (b) Latch                                           | 63 |

|--------------|------------------------------------------------------------------------------------------|----|

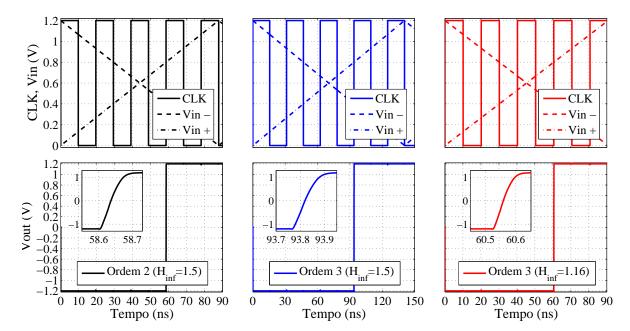

| Figura 7.6 – | Resultados de simulação do comparador                                                    | 64 |

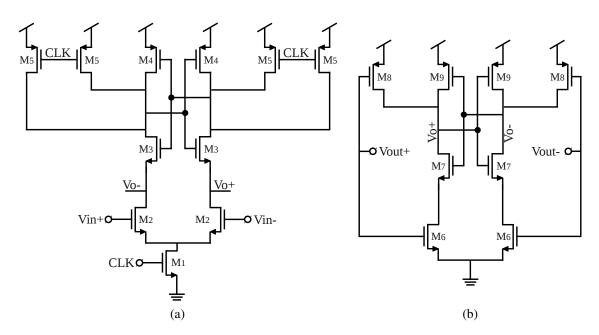

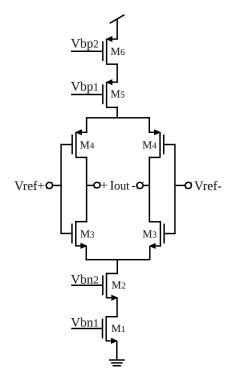

| Figura 7.7 – | Esquemático do DAC                                                                       | 65 |

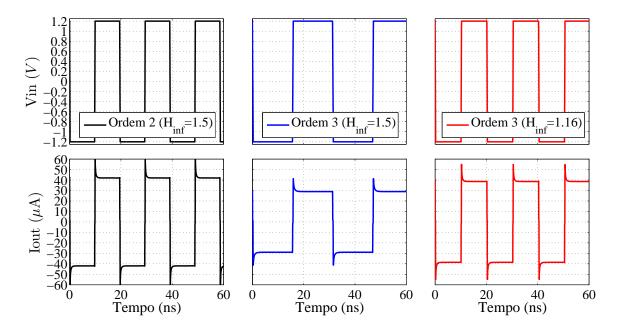

| Figura 7.8 – | Resultados de simulação DAC                                                              | 66 |

| Figura 8.1 – | Histogramas. (a) 1° e 2° integrador (Ordem 2, $H_{inf} = 1, 5$ ) (b) 1° a 3°             |    |

| _            | integrador (Ordem 3, $H_{inf} = 1, 5$ ) (c) 1° a 3° integrador (Ordem 3, $H_{inf} =$     |    |

|              | 1, 16)                                                                                   | 67 |

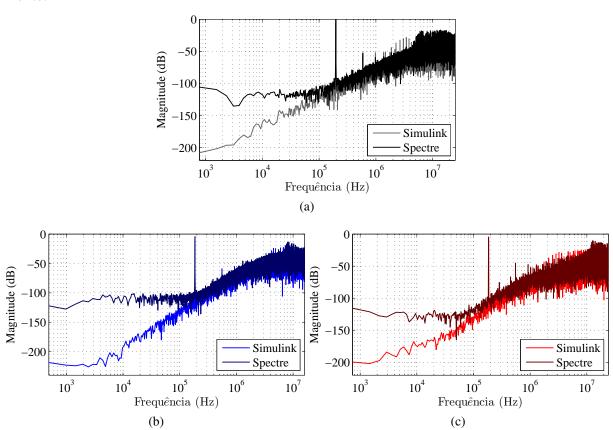

| Figura 8.2 – | Spectra do modulador $\Sigma\Delta$ . (a) Ordem 2, $H_{inf}=1,5$ (b) Ordem 3, $H_{inf}=$ |    |

| _            | 1, 5 (c) Ordem 3, $H_{inf} = 1, 16$                                                      | 68 |

| Figura 8.3 – | SNR versus amplitude do sinal de entrada. Performance a nível de circuito                | 69 |

| Figura A.1 – | Janela de configuração do quantizador no Simulink                                        | 81 |

| Figura B.1 – | Janela de configuração do DAC no Simulink                                                | 85 |

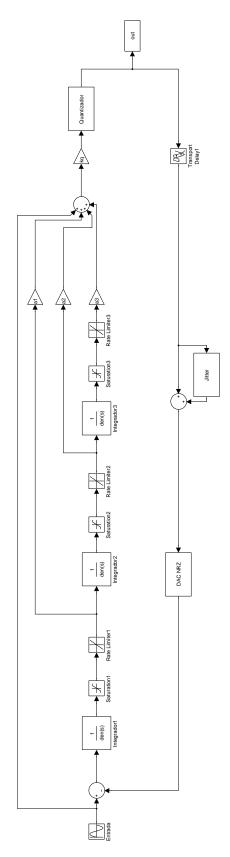

| Figura C.1 – | Diagrama de blocos do modulador de terceira ordem no Simulink                            | 88 |

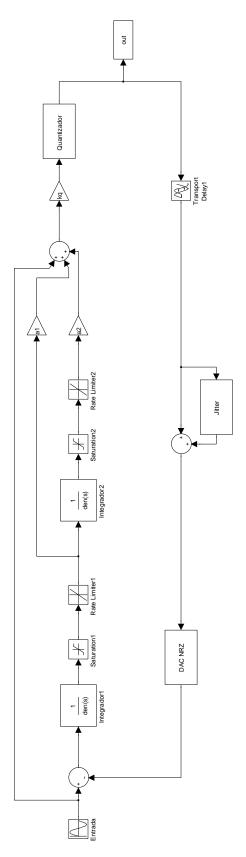

| Figura D.1 – | Diagrama de blocos do modulador de segunda ordem no Simulink                             | 89 |

| C            |                                                                                          |    |

|              |                                                                                          |    |

## LISTA DE TABELAS

| Tabela 1.1 – | Performance de moduladores                         | 18 |

|--------------|----------------------------------------------------|----|

| Tabela 3.1 – | Vantagens de moduladores $\Sigma\Delta$ em CT e DT | 33 |

| Tabela 4.1 – | Especificações de projeto.                         | 37 |

| Tabela 4.2 – | Parâmetros dos moduladores $\Sigma\Delta$          | 38 |

| Tabela 4.3 – | Coeficientes dos moduladores $\Sigma\Delta$ em CT  | 39 |

| Tabela 5.1 – | Especificações de algumas não-idealidades          | 50 |

| Tabela 5.2 – | Performance no nível de abstração do sistema       | 51 |

| Tabela 7.1 – | Dimensão dos dispositivos RC                       | 58 |

| Tabela 7.2 – | Dimensão dos dispositivos dos amplificadores       | 62 |

| Tabela 7.3 – | Dimensão dos dispositivos do CMFB                  | 62 |

| Tabela 7.4 – | Dimensão dos dispositivos do quantizador           | 64 |

| Tabela 7.5 – | Dimensão dos dispositivos do DAC                   | 66 |

| Tabela 8.1 – | Performance no nível de abstração do circuito      | 70 |

## LISTA DE APÊNDICES

| APÊNDICE A - Código C do quantizador                             | 81 |

|------------------------------------------------------------------|----|

| APÊNDICE B - Código C do DAC                                     |    |

| APÊNDICE C - Diagrama de blocos do modulador de terceira ordem   |    |

| APÊNDICE D – Diagrama de blocos do modulador de segunda ordem    | 89 |

| APÊNDICE E – Comparador ideal em VHDL-AMS                        | 90 |

| APÊNDICE F - DAC (com slew rate e excess loop delay) em VHDL-AMS | 91 |

| APÊNDICE G - Amplificador (com ganho e GBW) em VHDL-AMS          |    |

#### LISTA DE ABREVIATURAS E SIGLAS

AD Analógico-Digital

ADC Analog-to-Digital Converter, Conversor Analógico-Digital

CIFF Cascade of Integrators in Feed-Forward, Cascata de Integradores com Alimentação

em Avanço

CIFB Cascade of Integrators Feedback, Cascata de Integradores com Realimentação

CMFB Common Mode Feedbak, Realimentação de Modo Comum

CMOS Complementary Metal Oxide Semiconductor, Semicondutor Metal-Óxido Comple-

mentar

CT Continuous Time, Tempo Contínuo

DAC Digital-to-Analog Converter, Conversor Digital-Analógico

DR Dynamic Range, Faixa Dinâmica

DT Discrete Time, Tempo Discreto

ELD Excess Loop Delay, Atraso Excessivo do Laço de Realimentação

ENOB Effective Number of Bits, Número efetivo de bits

FOM Figure of Merit, Figura de Mérito

GBW Gain Bandwidth Product, Produto Ganho-Banda

IBN In Band Noise, Ruído Dentro da Banda de Interesse

LHP Left Half-Plane, Semi-Plano Esquerdo

MASH Multi-Stage Noise-Shaping, Noise-Shaping de Múltiplos Estágios

NRZ Non Return-to-Zero, Não Retorna para Zero

NTF Noise Transfer Function, Função de Transferência do Ruído

OSR Oversampling Ratio, Taxa de Sobreamostragem

PSD Power Spectrum Density, Densidade Espectral de Potência

RHP Right Half-Plane, Semi-Plano Direito

RZ Return-to-zero, Retorna para Zero

SC Switched-Capacitor, Capacitor Chaveado

SD Sigma-Delta

SDM Modulador Sigma-Delta

SFDR Spurious Free Dynamic Range, Faixa Dinâmica Livre de Espúrios

SNDR Signal to Noise plus Distortion Ratio, Razão Sinal-Ruído mais Distorção

SNR Signal to Noise Ratio, Razão Sinal Ruído

SQNR Signal to Quantization Noise Ratio, Razão-Sinal Ruído de Quantização

STF Signal Transfer Function, Função de Transferência do Sinal

## **SUMÁRIO**

| 1 INTRODUÇÃO                                                      | 17 |

|-------------------------------------------------------------------|----|

| 1.1 Motivação                                                     | 18 |

| 1.2 Objetivos                                                     | 19 |

| 1.3 Organização do Trabalho                                       | 19 |

| 2 PRINCÍPIOS DA CONVERSÃO A/D                                     | 20 |

| 2.0.1 Amostragem                                                  | 20 |

| 2.0.2 Quantização                                                 | 21 |

| 2.0.3 Ruído de quantização                                        | 23 |

| 2.0.3.1 Limitações do modelo linear com ruído branco              | 24 |

| 2.0.4 <i>Noise-shapping</i>                                       | 25 |

|                                                                   | 26 |

| 2.2 Métricas de performance                                       | 27 |

| 2.2.1 Métricas espectrais                                         | 27 |

| 2.2.2 Métricas de potência e ruído                                | 28 |

| <u> </u>                                                          | 29 |

| 2.3.1 Moduladores $\Sigma\Delta$ de ordem superior                | 30 |

| 2.3.2 Moduladores $\Sigma\Delta$ com alta taxa de sobreamostragem | 31 |

|                                                                   | 31 |

| 3 MODULADORES $\Sigma\Delta$ EM CT                                | 32 |

| 3.1 Vantagens de moduladores $\Sigma\Delta$ em CT e DT            | 33 |

| 3.2 Escolhas de projeto                                           | 33 |

| 3.2.1 Taxa de sobreamostragem                                     | 33 |

| 3 1                                                               | 33 |

| 3.2.3 Topologia de laço único ou cascata                          | 34 |

| 3.2.4 Topologia feedforward versus feedback                       | 34 |

|                                                                   | 35 |

| 4 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO SISTEMA           | 37 |

| <b>4.1</b> Especificações                                         | 37 |

| <b>4.2 Parâmetros</b>                                             | 37 |

| 4.3 Topologia                                                     | 38 |

| 4.4 Projeto do laço                                               | 38 |

| 5 ANÁLISE, MODELAGEM E EFEITOS DAS NÃO-IDEALIDADES DE MODU-       |    |

| LADORES $\Sigma\Delta$ EM CT                                      | 40 |

| 5.1 Clock Jitter                                                  | 40 |

| 5.2 Excess loop delay                                             | 42 |

| 5.3 Ganho finito dos amplificadores                               | 43 |

| 5.4 Produto ganho banda finito dos amplificadores                 | 45 |

| 5.5 Slew rate finito dos amplificadores                           | 46 |

| 5.6 Output swing limitado                                         | 46 |

| 5.7 DAC e Quantizador                                             | 47 |

| 5.8 Erro da constante de tempo                                    | 48 |

| 5.9 Ruído térmico                                                 | 49 |

| 5 10Egnocificações dos não idealidades                            |    |

| 5.10Especificações das não-idealidades                            | 49 |

| 6.3 Agressividade da NTF546.4 Critério de estabilidade567 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO CIRCUITO577.1 Esquemático do modulador $ΣΔ$ no nível de abstração elétrica577.2 Implementação dos coeficientes587.3 Projeto em tecnologia CMOS597.3.1 Projeto dos amplificadores597.3.2 Projeto do quantizador627.3.3 Projeto do DAC658 RESULTADOS DE PERFORMANCE DO MODULADOR678.1 Histogramas das saídas dos integradores678.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS74 | 6 ESTABILIDADE                                                             | 52 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|----|

| 6.3 Agressividade da NTF546.4 Critério de estabilidade567 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO CIRCUITO577.1 Esquemático do modulador $ΣΔ$ no nível de abstração elétrica577.2 Implementação dos coeficientes587.3 Projeto em tecnologia CMOS597.3.1 Projeto dos amplificadores597.3.2 Projeto do quantizador627.3.3 Projeto do DAC658 RESULTADOS DE PERFORMANCE DO MODULADOR678.1 Histogramas das saídas dos integradores678.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS72 | 6.1 Máximo sinal de entrada estável                                        | 52 |

| 6.4 Critério de estabilidade567 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO CIRCUITO577.1 Esquemático do modulador ΣΔ no nível de abstração elétrica577.2 Implementação dos coeficientes587.3 Projeto em tecnologia CMOS597.3.1 Projeto dos amplificadores597.3.2 Projeto do quantizador627.3.3 Projeto do DAC658 RESULTADOS DE PERFORMANCE DO MODULADOR678.1 Histogramas das saídas dos integradores688.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS74                             | 6.2 Root Locus                                                             | 53 |

| 6.4 Critério de estabilidade567 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO CIRCUITO577.1 Esquemático do modulador ΣΔ no nível de abstração elétrica577.2 Implementação dos coeficientes587.3 Projeto em tecnologia CMOS597.3.1 Projeto dos amplificadores597.3.2 Projeto do quantizador627.3.3 Projeto do DAC658 RESULTADOS DE PERFORMANCE DO MODULADOR678.1 Histogramas das saídas dos integradores688.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS74                             | 6.3 Agressividade da NTF                                                   | 54 |

| 7.1 Esquemático do modulador $\Sigma\Delta$ no nível de abstração elétrica577.2 Implementação dos coeficientes587.3 Projeto em tecnologia CMOS597.3.1 Projeto dos amplificadores597.3.2 Projeto do quantizador627.3.3 Projeto do DAC658 RESULTADOS DE PERFORMANCE DO MODULADOR678.1 Histogramas das saídas dos integradores678.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS74                                                                                                         |                                                                            | 56 |

| 7.2 Implementação dos coeficientes       58         7.3 Projeto em tecnologia CMOS       59         7.3.1 Projeto dos amplificadores       59         7.3.2 Projeto do quantizador       62         7.3.3 Projeto do DAC       65         8 RESULTADOS DE PERFORMANCE DO MODULADOR       67         8.1 Histogramas das saídas dos integradores       67         8.2 Resposta em frequência dos moduladores       68         8.3 SNR       69         9 CONCLUSÕES       72         REFERÊNCIAS       74              | 7 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO CIRCUITO                   | 57 |

| 7.3 Projeto em tecnologia CMOS597.3.1 Projeto dos amplificadores597.3.2 Projeto do quantizador627.3.3 Projeto do DAC658 RESULTADOS DE PERFORMANCE DO MODULADOR678.1 Histogramas das saídas dos integradores678.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS74                                                                                                                                                                                                                         | 7.1 Esquemático do modulador $\Sigma\Delta$ no nível de abstração elétrica | 57 |

| 7.3.1 Projeto dos amplificadores 59 7.3.2 Projeto do quantizador 62 7.3.3 Projeto do DAC 65 8 RESULTADOS DE PERFORMANCE DO MODULADOR 67 8.1 Histogramas das saídas dos integradores 67 8.2 Resposta em frequência dos moduladores 68 8.3 SNR 69 9 CONCLUSÕES 72 REFERÊNCIAS 74                                                                                                                                                                                                                                        | 7.2 Implementação dos coeficientes                                         | 58 |

| 7.3.2 Projeto do quantizador 62 7.3.3 Projeto do DAC 65  8 RESULTADOS DE PERFORMANCE DO MODULADOR 67  8.1 Histogramas das saídas dos integradores 67  8.2 Resposta em frequência dos moduladores 68  8.3 SNR 69  9 CONCLUSÕES 72  REFERÊNCIAS 74                                                                                                                                                                                                                                                                      | 7.3 Projeto em tecnologia CMOS                                             | 59 |

| 7.3.3 Projeto do DAC  8 RESULTADOS DE PERFORMANCE DO MODULADOR  8.1 Histogramas das saídas dos integradores  8.2 Resposta em frequência dos moduladores  8.3 SNR  9 CONCLUSÕES  72  REFERÊNCIAS                                                                                                                                                                                                                                                                                                                       | 7.3.1 Projeto dos amplificadores                                           | 59 |

| 8 RESULTADOS DE PERFORMANCE DO MODULADOR 678.1 Histogramas das saídas dos integradores 678.2 Resposta em frequência dos moduladores 688.3 SNR 69 CONCLUSÕES 72 REFERÊNCIAS 74                                                                                                                                                                                                                                                                                                                                         | 7.3.2 Projeto do quantizador                                               | 62 |

| 8 RESULTADOS DE PERFORMANCE DO MODULADOR 678.1 Histogramas das saídas dos integradores 678.2 Resposta em frequência dos moduladores 688.3 SNR 69 CONCLUSÕES 72 REFERÊNCIAS 74                                                                                                                                                                                                                                                                                                                                         | 7.3.3 Projeto do DAC                                                       | 65 |

| 8.2 Resposta em frequência dos moduladores688.3 SNR699 CONCLUSÕES72REFERÊNCIAS74                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                            | 67 |

| 8.3 SNR       69         9 CONCLUSÕES       72         REFERÊNCIAS       74                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.1 Histogramas das saídas dos integradores                                | 67 |

| 9 CONCLUSÕES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.2 Resposta em frequência dos moduladores                                 | 68 |

| REFERÊNCIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.3 SNR                                                                    | 69 |

| REFERÊNCIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9 CONCLUSÕES                                                               | 72 |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                            | 74 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •                                                                          | 80 |

## 1 INTRODUÇÃO

O conversor analógico digital sigma-delta ( $\Sigma\Delta$  ADC) é uma das arquiteturas de ADCs mais adequadas para uma grande variedade de aplicações, principalmente para aplicação em circuitos eletrônicos de comunicação sem fio. Um ADC  $\Sigma\Delta$  é composto basicamente por um modulador sigma-delta ( $\Sigma\Delta M$ ) e um filtro digital. O  $\Sigma\Delta M$  emprega técnicas de sobreamostragem e *noise-shaping* para obter alta razão sinal ruído (SNR) utilizando quantizadores de baixa resolução. De modo a aumentar a resolução do modulador, há três parâmetros que geralmente são incrementados, i.e., taxa de sobreamostragem (M), número de bits do quantizador (B) e ordem do filtro (L), no entanto, o incremento de cada parâmetro implica no aumento da complexidade de projeto em nível de circuito. Arquiteturas que utilizam quantizadores *multi-bit* tem a linearidade degradada, a taxa de sobreamostragem é limitada pela tecnologia e consumo de energia, e a ordem do filtro é limitada principalmente pela estabilidade do sistema. Uma alternativa para arquiteturas com alta ordem é utilizar o sistema em cascata, no entanto, a complexidade do projeto se dará de forma a manter a correlação entre ambos os estágios. Assim, moduladores com baixa ordem e com quantizadores *single-bit* são mais lineares e menos complexos de serem projetados, além disso, consomem menos energia.

A busca por ADCs com maior velocidade e resolução cresce de modo que aumentam as especificações dos padrões de comunicação sem fio. Em tais sistemas, geralmente são empregados ADCs do tipo pipeline. No entanto,  $\Sigma\Delta Ms$  em tempo contínuo (CT) têm sido cada vez mais utilizados. A maioria dos moduladores reportados na literatura são projetados em tempo discreto (DT) (ROSA, 2011), isto se deve principalmente à maturidade das metodologias de projeto e à robustez do circuito perante as variações de processo (VLEUGELS; RABII; WOO-LEY, 2001) e (OLIAEI; CLEMENT; GORISSE, 2002). Apesar dos ADCs em tempo discreto oferecerem um grau de precisão elevado, a velocidade do circuito é limitada pelo *settling* do integrador projetado com capacitor chaveado. Comparando com o ADC tradicional em DT, ADCs em CT têm a vantagem de possuir maior velocidade e ao mesmo tempo, menor consumo de energia. Além disso, moduladores em CT tem filtro anti-alias implícito, reduzindo ainda mais a complexidade de projeto. Apesar de moduladores em CT não terem problemas de injeção de carga, *settling time* e outros problemas característicos de moduladores em DT, moduladores em CT sofrem de várias não-idealidades como *clock jitter, excess loop delay* e variação dos coeficientes devido a variações de processo de fabricação dos componentes ativos e

passivos (MALOBERTI, 2007). Todas essas e outras não-idealidades somadas exercem grande efeito sobre a performance do modulador.

#### 1.1 Motivação

Este trabalho surgiu da necessidade de se implementar um  $\Sigma\Delta M$  em tempo contínuo capaz de suprir as especificações para o padrão GSM. Desta forma, foi estudada uma metodologia de projeto (ROSA; RÍO, 2013), onde percebeu-se que os resultados obtidos estavam muito abaixo do estimado pela equação da SNR ideal quando fazia-se uso de moduladores *single-bit* com ordem superior a 2. Sendo assim, procurou-se referências de autores que projetaram moduladores similares, ou seja, moduladores *single-bit* com ordem superior a 2. Com isso, a Tabela 1.1 resume algumas implementações de  $\Sigma\Delta M$  em tempo contínuo *single-bit* de ordem 2 e 3. Percebe-se na Tabela 1.1 que os moduladores de terceira ordem (L=3) têm uma maior perda de faixa dinâmica (DR<sub>perda</sub>) em relação à faixa dinâmica ideal (DR<sub>ideal</sub>) quando comparados aos moduladores de segunda ordem (L=2). Portanto, com estas informações, percebeu-se que moduladores de terceira ordem quando considerados, além da resolução do modulador, o consumo de energia e a complexidade de projeto.

DR (dB) Autor M L  $\mathbf{DR}_{ideal}$  (dB)  $\mathbf{DR}_{perda}$  (dB)  $B_{\mathbf{W}}$  (MHz) В [1] 90,9 127,9 37,0 0,024 128 1 78,5 260,4 0,010 3 1 [2] 181,9 10000 1 45,6 0,002 3 [3] 68,0 113,6 80 77,0 19,2 2 [4] 96,2 1,000 140 1 [5] 70,0 84,4 14,4 1,920 81 2 1 72,0 91,1 19,1 0,000256 2 1 [6] 111

Tabela 1.1: Performance de moduladores.

[1] - (PAVAN; SANKAR, 2010). [2] - (ZARE-HOSEINI; KALE; RICHARD, 2010). [3] - (GARCIA; RODRIGUEZ; RUSU, 2013). [4] - (PUTTER, 2004). [5] - (ANDERSON; SUNDSTROM, 2009). [6] - (CANNILLO et al., 2011)

#### 1.2 Objetivos

Existem várias técnicas propostas na literatura visando a redução do consumo de energia em  $\Sigma\Delta M$  no nível de abstração do circuito (CHAE; HAN, 2009)(PENA-PEREZ; BONIZ-ZONI; MALOBERTI, 2012) e até mesmo no nível de abstração do sistema, onde (MARQUES et al., 1998) apresenta coeficientes otimizados para implementação de moduladores de laço único, no entanto é apenas válido para moduladores em tempo discreto (DT). Este trabalho apresenta o projeto de  $\Sigma\Delta M$  de alta performance considerando a estabilidade e a ordem do modulador. Uma relação entre taxa de sobreamostragem, ordem do filtro e máxima amplitude do sinal de entrada serão analisadas de modo a encontrar a NTF apropriada, implicando diretamente na redução da complexidade de projeto. A abordagem sobre a estabilidade proposta neste trabalho baseia-se em teoria de controle, sendo assim, é válida para moduladores em tempo discreto e contínuo. Também é feita neste trabalho uma análise e modelagem das principais não-idealidades no nível de abstração do sistema de modo que a performance do modulador seja garantida dentro dos limites impostos. Por fim, para validar o estudo feito, são implementados três moduladores em tecnologia CMOS de 130nm com as especificações obtidas no nível de abstração do sistema.

#### 1.3 Organização do Trabalho

Este trabalho está organizado em 9 capítulos. O capítulo a seguir apresenta os principais conceitos sobre ADCs, enquanto o Capítulo 3 apresenta os conceitos sobre  $\Sigma\Delta M$ s. O Capítulo 4 apresenta as especificações e o projeto dos  $\Sigma\Delta M$ s no nível de abstração do sistema. O Capítulo 5 apresenta a modelagem e análise das principais não-idealidades presentes nos  $\Sigma\Delta M$ s em tempo contínuo. No Capítulo 6 é feita uma análise sobre a estabilidade do sistema. O Capítulo 7 apresenta em detalhes o projeto elétrico em tecnologia CMOS de 130 nm dos  $\Sigma\Delta M$ s projetados. Os resultados obtidos e discussões referentes ao projeto e simulação no nível de abstração do circuito dos moduladores são apresentados no Capítulo 8. Finalmente, no Capítulo 9 são apresentadas e discutidas as principais conclusões do trabalho.

## 2 PRINCÍPIOS DA CONVERSÃO A/D

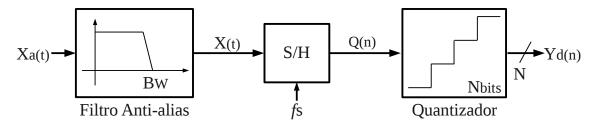

Um ADC efetua a transformação de sinais analógicos (contínuos) em sinais digitais (discretos). A Figura 2.1 mostra o diagrama de blocos generalizado de um conversor A/D que consiste basicamente de um filtro anti-alias (AAF), um amostrador (*sample & hold*) e um quantizador. Seu funcionamento dá-se da seguinte forma:

- 1. O sinal de entrada analógico  $X_a(t)$  passa pelo filtro anti-alias que neste caso é representado como um filtro do tipo passa-baixa (LP);

- 2. O sinal X(t) que passou pelo filtro é amostrado a uma taxa de amostragem  $f_s$  pelo bloco S/H resultando no sinal Q(n) discreto;

- 3. Os valores de Q(n) são quantizados usando N bits de modo que cada valor contínuo seja mapeado em um valor discreto resultando no sinal Yd(n).

Figura 2.1: Diagrama de blocos generalizado de um conversor A/D do tipo Nyquist.

O funcionamento dos blocos ilustrados na Figura 2.1 serão analisados nas próximas seções.

#### 2.0.1 Amostragem

De acordo com o teorema de Nyquist, para que não haja perda da informação, X(t) na Figura 2.1 deve ser amostrado a uma frequência  $f_{\rm N} \geq 2 \times B_W$  onde  $f_{\rm N}$  é a frequência de Nyquist e  $B_W$  é a largura de banda do sinal. Sendo assim, ADCs nos quais o sinal de entrada é amostrado a uma frequência  $f_s = f_{\rm N}$  são denominados ADCs do tipo Nyquist, enquanto que ADCs na qual o sinal de entrada é amostrado a uma frequência  $f_s > f_{\rm N}$  são denominados ADCs sobreamostrados (MALOBERTI, 2007). O valor da sobreamostragem (M) em que o sinal de entrada é amostrado acima da frequência de Nyquist pode ser definido como

$$M = \frac{f_s}{2 \times B_W} \tag{2.1}$$

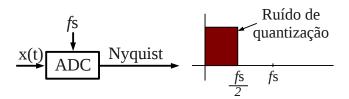

A Figura 2.2 mostra o espectro de um ADC do tipo Nyquist, onde o sinal de entrada x(t) está entre  $\{DC, \frac{fs}{2}\}$  com o ruído de quantização distribuído uniformemente dentro da banda do sinal.

Figura 2.2: Filtro anti-alias para ADC do tipo Nyquist.

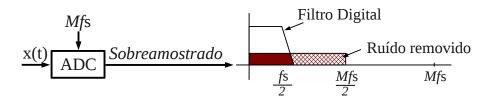

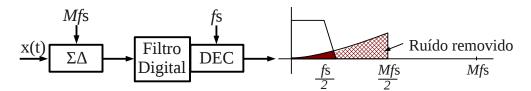

Na Figura 2.3 a frequência de amostragem foi aumentada pelo fator M, no entanto, o sinal de entrada continua imutável, desta forma, o ruído de quantização é distribuído no intervalo  $\{DC, \frac{M \times fs}{2}\}DC$ . O ruído presente fora da banda do sinal é então removido com um filtro digital. Após, o sinal de saída passa pelo decimador (DEC) que reduz a frequência deste sinal novamente para  $f_s$ .

Este processo de sobreamostragem, seguido da remoção do ruído pelo filtro digital e logo após a decimação, faz com que a razão sinal-ruído (SNR) aumente a uma taxa de 3 dB a cada duplicação de M.

Figura 2.3: Filtro anti-alias para ADC sobreamostrado.

#### 2.0.2 Quantização

Em princípio, o processo de amostragem não resulta em nenhuma perda de informação, desde que a condição  $f_{\rm N} \geq 2B_W$  seja satisfeita. No entanto, isto não acontece para a quantização do sinal amostrado, pois, neste processo irreversível, um intervalo contínuo de amplitudes é mapeado em um conjunto de valores finitos que resultarão em códigos discretos. Desta forma, mesmo o processo de quantização ideal introduz limitação na performance do ADC e este erro

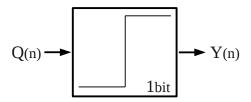

denominado erro de quantização. O diagrama de blocos de um quantizador *single-bit* é mostrado na Figura 2.4.

Figura 2.4: Diagrama de blocos de um quantizador single-bit.

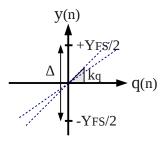

A característica predominante de um quantizador é o número de bits (N), sendo que quantizadores com N=1 são denominados single-bit e para N>1 multi-bit. A Figura 2.5 ilustra a curva de transferência do processo de quantização para um quantizador single-bit, de modo que a saída do quantizador é determinada apenas pelo sinal (positivo ou negativo) da entrada, independente da sua magnitude. Sendo assim, o ganho  $k_q$  pode ser escolhido arbitrariamente e geralmente é definido como unitário.

Figura 2.5: Processo de quantização singe-bit.

O espaçamento uniforme entre dois níveis de quantização  $(\Delta)$  é definido como o passo de quantização

$$\Delta = \frac{Y_{FS}}{2^N - 1} \tag{2.2}$$

onde  $Y_{FS}$  é a faixa *full-scale* de saída do quantizador.

Como o sinal na entrada do quantizador está entre  $-Y_{FS}$  e  $+Y_{FS}$ , a saída é quantizada em um destes valores, resultando em um sinal discreto. O erro de quantização resultante desta operação é definido como a diferença entre sinal de entrada e o sinal de saída do quantizador. Este erro pode ser observado na Figura 2.6 onde o erro de quantização é limitado por  $-\Delta/2$  e  $+\Delta/2$ .

Figura 2.6: Erro de quantização singe-bit.

#### 2.0.3 Ruído de quantização

De modo a analisar o ruído de quantização, a saída do quantizador pode ser escrita como a soma do sinal de entrada Q(n), com o erro de quantização e(n), na qual é o resultado de uma operação não linear  $q\{\cdot\}$  em Q(n):

$$Y_d(n) = Q(n) + e(n) = Q(n) + q\{Q(n)\}$$

(2.3)

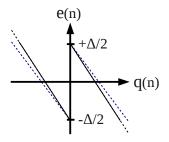

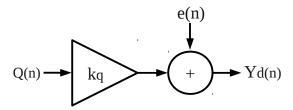

Entretanto, torna-se difícil analisar o efeito do quantizador usando (2.3) devido à natureza não linear e dependente de sinal do erro de quantização. Para simplificar a análise, este erro de quantização  $e(n) = q\{Q(n)\}$  pode ser aproximado como um ruído aditivo. Sendo assim, o quantizador é analisado usando métodos estatísticos. Apesar na natureza determinística do erro de quantização, a aproximação utilizando ruído branco como ilustra a Figura 2.7 é válida se as seguintes condições forem satisfeitas (GERFERS; ORTMANNS, 2010):

- O sinal de entrada não pode exceder  $Y_{FS}$ ;

- O quantizador tem níveis suficientes de quantização;

- O sinal de entrada percorre vários níveis de quantização.

Figura 2.7: Modelo linear de um quantizador com ruído branco.

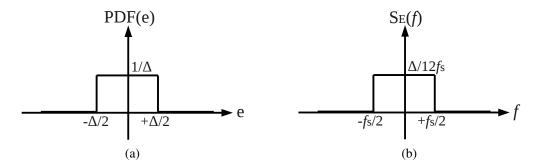

Dentro das condições listadas acima, é aceitável assumir que o erro de quantização, e(n), é distribuído uniformemente dentro do intervalo  $-\Delta/2$  e  $+\Delta/2$  com a função densidade de probabilidade ilustrada na Figura 2.8a.

Figura 2.8: Ruído de quantização (a) função densidade de probabilidade (b) densidade de potência espectral.

A potência do erro de quantização é expressa por

$$\overline{e^2} = \sigma_e^2 = \frac{1}{\Delta} \int_{\frac{-\Delta}{2}}^{\frac{\pm \Delta}{2}} e^2 de = \frac{\Delta^2}{12}$$

(2.4)

O pressuposto acima implica que, como ilustra a Figura 2.8b, a potência do ruído também será distribuída uniformemente no intervalo -fs/2 e +fs/2, sendo assim,

$$\overline{e^2} = \int_{\frac{-fs}{2}}^{\frac{+fs}{2}} df = \frac{\Delta^2}{12}$$

(2.5)

logo, a densidade de potência espectral do erro de quantização no intervalo -fs/2 e +fs/2 é dada por

$$S_E = \frac{\overline{e^2}}{fs} = \frac{\Delta^2}{12fs} \tag{2.6}$$

#### 2.0.3.1 Limitações do modelo linear com ruído branco

Devido ao fato de que o ruído de quantização é correlacionado com o sinal de entrada, o espectro da saída do quantizador pode obter pulsos discretos que não são preditos pelo modelo linear (GERFERS; ORTMANNS, 2010). Esta correlação é mais acentuada no caso de quantizadores *single-bit* (SCHREIER; TEMES, 2004). Entretanto, a modelagem do quantizador desta maneira é bastante vantajosa. Mesmo que o quantizador *single-bit* viole as condições do modelo, este ainda permite uma estimativa bastante precisa da performance do ADC que poderá ser confirmada através de simulações.

#### 2.0.4 Noise-shapping

Para aumentar a performance do ADC, é incluído um laço de realimentação na malha para que o ruído dentro da banda de interesse seja reduzido, no entanto o ruído fora da banda será aumentado, o que não é preocupante, de modo que este ruído será removido posteriormente pelo filtro digital.

A Figura 2.9 ilustra um diagrama de blocos semelhente à Figura 2.3, no entanto, o ADC convencional foi substituído por um modulador  $\Sigma\Delta$ . O modulador exerce o efeito de modelar o ruído de quantização (*noise shaping*) para que este fique em sua maior parte fora da banda de interesse, aumentando a performance do ADC no intervalo  $\{DC, \frac{fs}{2}\}$ .

Figura 2.9: Efeito de noise-shaping.

A função de transferência criada neste laço de realimentação é usualmente denominada *noise transfer function* (NTF) e a ordem desta função indica a ordem no modulador (L), neste caso, quanto maior a ordem, maior será a redução do ruído dentro da banda de interesse. A NTF ideal no domínio discreto é dada por (ROSA; RÍO, 2013)

$$NTF(z) = (1 - z^{-1})^{L} (2.7)$$

Considerando  $z=e^{j2\pi/fs}$ , M maior ou igual a 1 e  $\Delta$  modelado como ruído branco, neste caso, a potência do ruído dentro da banda passa a ser (ROSA; RÍO, 2013)

$$P_Q = \frac{\Delta^2}{12} \frac{\pi^{2L}}{(2L+1)M^{2L+1}} \tag{2.8}$$

Sendo assim, se a sobreamostragem é utilizada em conjunto com noise-shapping, a performance do modulador aumenta a uma taxa aproximada de  $6L\,dB/oitava$  (ROSA; RÍO, 2013).

#### 2.1 Princípios de moduladores $\Sigma\Delta$

Conversores  $\Sigma\Delta$  usam um caminho de realimentação de modo a fechar a malha do sistema e desta forma controlar o erro de quantização.

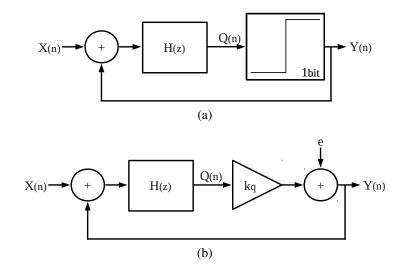

O diagrama de blocos básico de um  $\Sigma\Delta M$  é ilustrado na Figura 2.10a e consiste de uma função de transferência do laço H(z) e um quantizador em um sistema de malha fechada.

Figura 2.10: Modulador  $\Sigma\Delta$ . (a) Diagrama de blocos (b) modelo com aproximação linear.

Utilizando o modelo linear para o quantizador, o  $\Sigma\Delta M$  da Figura 2.10b pode ser modelado por um sistema linear representado no domínio discreto por:

$$Y(z) = STF(z)X(z) + NTF(z)E(z)$$

(2.9)

onde STF e NTF são a função de transferência do sinal e função de transferência do ruído, respectivamente, e podem ser representadas por

$$STF(z) = \frac{k_q H(z)}{1 + k_q H(z)}, NTF(z) = \frac{1}{1 + k_q H(z)}$$

(2.10)

Uma configuração ideal para STF e NTF seria a completa remoção do ruído dentro da banda do sinal [0, BW] para um conversor passa-baixa. Fora da banda do sinal o ganho da NTF poderá ser elevado, enquanto o ganho da STF poderá ser baixo. Assim, pode-se então afirmar que uma NTF ideal é o inverso da STF, ou seja,

$$NTF_{ideal} = \overline{STF_{ideal}} = \begin{cases} 0 & \text{se BW} \le f \le BW \\ 1 & \text{do contrário.} \end{cases}$$

(2.11)

Em um  $\Sigma\Delta M$  do tipo passa-baixas, a função de transferência do laço H(z) pode ser descrita como um integrador, i.e.,

$$ITF(z) = \frac{z^{-1}}{1 - z^{-1}}. (2.12)$$

Onde ITF(z) é a função de transferência do integrador. Sendo assim, em combinação com o quantizador, a saída do  $\Sigma\Delta M$  de primeira ordem no tempo discreto é dada por

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z).$$

(2.13)

#### 2.2 Métricas de performance

As métricas de performance dos conversores AD podem ser divididas em duas categorias: métricas de performance estática e dinâmica. A primeira inclui monotonicidade, *offset*, erro de ganho, não-linearidade diferencial (DNL) e não-linearidade integral (INL). Já as métricas de performance dinâmicas incluem ruído dentro da banda do sinal (IBN), SNR, razão sinal-ruído mais distorção (SNDR), distorção harmônica total (THD), faixa dinâmica (DR), faixa dinâmica livre de espúrios (SFDR), razão sinal-ruído de quantização (SQNR), número efetivo de bits (ENOB) e *overload level* (OL).

Uma introdução a respeito das características estáticas é dada por (GERFERS; ORT-MANNS, 2010), no entanto, a performance de um  $\Sigma\Delta M$  geralmente é definida pelas características dinâmicas e estas podem ainda ser divididas em métricas espectrais e de potência.

#### 2.2.1 Métricas espectrais

Basicamente dois aspectos devem ser considerados para as métricas de performance espectrais em  $\Sigma\Delta M$ :

- Distorção harmônica total é a razão entre a soma de todas as frequências harmônicas acima da frequência fundamental pela potência desta.

- Faixa dinâmica livre de distorção é a razão da potência do sinal pela potência do tom espectral mais intenso dentro da banda do sinal (GERFERS; ORTMANNS, 2010).

#### 2.2.2 Métricas de potência e ruído

As métricas de potência e ruído são as mais utilizadas em  $\Sigma\Delta M$ . Estas métricas geralmente são obtidas por integração ou inspeção. Sendo elas:

Ruído dentro da banda do sinal é uma métrica de performance obtida por integração que mensura o ruído e distorção na saída do modulador presente dentro da banda de interesse. Proporciona uma visão direta sobre a influência de determinada arquitetura, comportamento não ideal dos blocos (GERFERS; ORTMANNS, 2010).

$$IBN(dB) = \frac{\Delta^2}{12M} \tag{2.14}$$

Razão sinal-ruído é a razão entre a potência do sinal pela potência do ruído na saída do conversor, e é específica para determinada amplitude de sinal. Matematicamente, o SNR pode ser representado como

$$SNR(dB) = 10 \log_{10}(\frac{P_{sinal,sada}}{IBN}). \tag{2.15}$$

- Razão sinal-ruído mais distorção é a razão entre a potência do sinal pela potência do ruído mais as distorções presentes dentro da banda do sinal.

- Faixa dinâmica é definida como a razão do valor rms do máximo sinal de entrada para o qual o modulador opera estável pelo valor rms do menor sinal de entrada.

$$DR(dB) = 10 \log_{10}(\frac{(Y_{FS}/2)^2}{2IBN})$$

(2.16)

Razão sinal-ruído de quantização é definida similarmente como o SNR, no entanto, o

SQNR considera o ruído de quantização e pode ser definido como

$$SQNR(dB) = 6,02N + 10\log_{10}(M) + 1,76.$$

(2.17)

• Número efetivo de bits é definido como o número de bits necessários para que um conversor do tipo Nyquist ideal atinja a mesma DR que um conversor  $\Sigma\Delta$ , desta forma, a performance de ADCs do tipo Nyquist e  $\Sigma\Delta$  podem ser facilmente comparadas. Também pode-se utilizar o SNDR no lugar da DR para expressar a precisão da conversão A/D em bits de um  $\Sigma\Delta$ M (BOSER; WOOLEY, 1988). Considerando que o sinal de entrada esteja na máxima amplitude suportada pelo conversor, ENOB pode então, ser matematicamente descrito como

$$ENOB(bit) = \frac{DR(dB) - 1,76}{6,02}$$

(2.18)

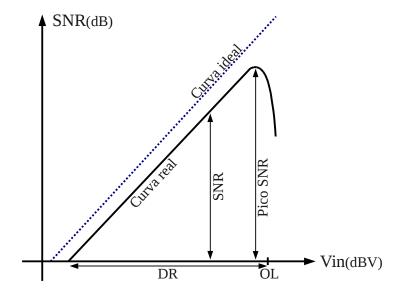

• *overload level* define a máxima amplitude do sinal de modo que o modulador ainda opere com estabilidade. OL é geralmente considerado como 6dB abaixo do SNR de pico.

A maioria das métricas de performance podem ser observadas através da Figura 2.11 (GERFERS; ORTMANNS, 2010).

Figura 2.11: Métricas de performance de um  $\Sigma \Delta M$ .

#### 2.3 Aumento da performance

A saída de um  $\Sigma\Delta M$  do tipo passa-baixas com ordem L pode ser representado no domínio discreto como (ROSA; RÍO, 2013)

$$Y(z) = z^{-L}X(z) + (1 - z^{-1})^{L}E(z).$$

(2.19)

Se um quantizador com B bits é empregado e tendo em conta que  $Y_{FS}=(2b-1)\Delta$  e que o ruído de quantização é a única fonte de ruído, a DR do  $\Sigma\Delta M$  poder ser definida como (ROSA; RÍO, 2013)

$$DR(dB) \approx 10 \log_{10} \left[ \frac{3}{2} (2^B - 1)^2 \frac{(2L+1)M^{(2L+1)}}{\pi^{2L}} \right]$$

(2.20)

Note que a partir de (2.20), a DR de um  $\Sigma\Delta M$  é determinada pelos valores de L, M e B. Desta forma, pode-se afirmar que estes três parâmetros são os necessários para determinar a performance ideal de um  $\Sigma\Delta M$ . Os prós e contras em relação ao aumento de cada parâmetro é discutido em (ROSA; RÍO, 2013), (GERFERS; ORTMANNS, 2010), (SCHREIER; TEMES, 2004) e (MALOBERTI, 2007).

#### 2.3.1 Moduladores $\Sigma\Delta$ de ordem superior

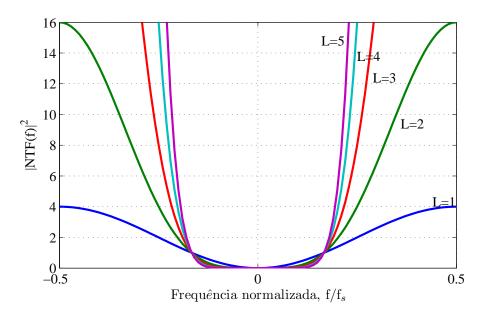

Moduladores  $\Sigma\Delta$  têm o princípio de operação baseado em *noise-shaping*, i.e., o ruído de quantização é retirado da banda do sinal para frequências superiores, sendo assim, quanto maior a ordem do modulador, mais ruído será removido da banda de interesse e, consequentemente, maior será o SNR resultante. A Figura 2.12 ilustra as funções de noise-shaping para moduladores até a quinta ordem.

Figura 2.12: Efeito do *noise-shaping* para  $\Sigma \Delta M$  com ordem até 5.

#### 2.3.2 Moduladores $\Sigma\Delta$ com alta taxa de sobreamostragem

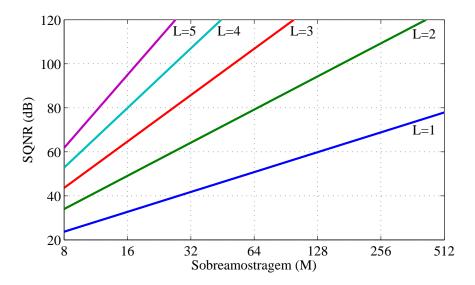

A Figura 2.13 ilustra o SQNR máximo de um  $\Sigma\Delta M$  single-bit com ordem variando de 1 a 5 e taxa de sobreamostragem de 8 a 512. Como pode ser verificado, a combinação da sobreamostragem com a ordem do modulador aumenta significativamente a resolução deste.

#### 2.3.3 Moduladores $\Sigma\Delta$ multi-bit

Um aumento na resolução do quantizador, significa uma redução no passo  $\Delta$ , desta forma, reduzindo o ruído de quantização. Para cada bit adicional no quantizador, haverá tipicamente um aumento de 6dB na DR do modulador.

Figura 2.13: Efeito da sobreamostragem para  $\Sigma\Delta M$  com ordem até 5.

#### 3 MODULADORES $\Sigma\Delta$ EM CT

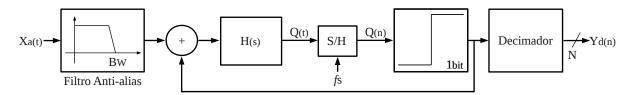

Tipicamente, moduladores  $\Sigma\Delta$  reportados na literatura são implementados em tempo discreto, i.e., baseados em circuitos chaveados (SC). Isto se deve ao fato de que circuitos SC podem ser projetados com alta linearidade. No entanto, a  $B_W$  de um modulador  $\Sigma\Delta$  em tempo discreto é limitada a poucos MHz devido as especificações necessárias dos componentes, como frequência de ganho unitário (UGF) e *slew rate* (SR) dos amplificadores empregados nos moduladores (RISBO; SØRENSEN, 1995). Na demanda de soluções com consumo de energia reduzido, moduladores  $\Sigma\Delta$  em tempo contínuo têm emergido devido às especificações mais relaxadas dos blocos, desta forma o sistema como um todo pode ser projetado de maneira mais simples (CHERRY; SNELGROVE; GAO, 2000) e (CHAO et al., 1990). A Figura 3.1 ilustra o diagrama de blocos de um modulador  $\Sigma\Delta$  em tempo contínuo para sinais do tipo passa-baixas.

Figura 3.1: Diagrama de blocos de um modulador  $\Sigma\Delta$  em tempo contínuo.

A diferença mais significativa entre modulares  $\Sigma\Delta$  em DT e CT é relacionada com a localização da operação de amostragem. Em CT, a operação é realizada imediatamente antes do quantizador e para DT a operação é realizada logo na entrada do modulador. Desta forma, a saída do modulador será um sinal discreto, enquanto a entrada será um sinal contínuo. Sendo assim, faz-se necessário o uso de um conversor digital-analógico (DAC). A reconstrução deste sinal é crítica para o desempenho do modulador e existem várias formas de onda que poderão ser utilizadas (BREEMS; HUIJSING, 2001). Dentre várias, as mais utilizadas são as retangulares e são basicamente divididas em três partes: *nonreturn-to-zero* (NRZ), *return-to-zero* (RZ) e *half-delay return-to-zero* (HRZ). A resposta ao impulso destas formas de onda pode ser expressa por

$$r_{DAC}(t) = \begin{cases} 1 & \text{se } \alpha \text{Ts} \leq t < \beta \text{Ts} \\ 0 & \text{do contrário.} \end{cases}$$

(3.1)

onde  $(\alpha, \beta)$  é (0, 1), (0, 1/2), e (1/2, 1) para NRZ, RZ, e HRZ, respectivamente.

#### 3.1 Vantagens de moduladores $\Sigma\Delta$ em CT e DT

A Tabela 3.1 resume as principais vantagens de moduladores  $\Sigma\Delta$  em tempo contínuo e discreto (GERFERS; ORTMANNS, 2010)

Tabela 3.1: Vantagens de moduladores  $\Sigma\Delta$  em CT e DT

| Tempo contínuo                               | Tempo discreto                          |

|----------------------------------------------|-----------------------------------------|

| Filtro anti-alias implícito                  | Baixa sensitividade a clock jitter      |

| Erros de S/H atenuados (noise shaping)       | Baixa sensitividade a excess loop delay |

| Maior fs possível (mais rápido)              | Insensitividade à forma de onda do DAC  |

| UGF dos OpAmps relaxados                     | Precisão da função de transferência     |

| Operação em altas temperaturas               | Ganho dos integradores precisos         |

| Menos sensível a glitch                      | Alta linearidade do integrador SC       |

| Menos ruído de chaveamento                   | Apenas carga capacitiva                 |

| Possível prototipar em breadboard            | Compatível com processos VLSI CMOS      |

| Menor tempo de simulação (nível de circuito) | Menor tempo de simulação (alto nível)   |

| SNR não é limitado pelo tamanho do capacitor | STF não tem pico fora da banda          |

#### 3.2 Escolhas de projeto

#### 3.2.1 Taxa de sobreamostragem

Para moduladores  $\Sigma\Delta$  com banda do sinal em megahertz, a frequência do clock é limitada pela tecnologia, além disso, deve-se levar em conta o quanto o modulador poderá dissipar de potência, pois aumentando a taxa de sobreamostragem, aumenta-se a frequência de amostragem  $f_s$  que, por consequência aumentará o requerimento de UGF dos amplificadores, assim, dissipando mais potência. Desta forma, estes fatores devem ser levados em conta na hora de escolher o parâmetro M.

#### 3.2.2 Ordem do filtro de laço e quantizadores *multi-bit*

Para moduladores com baixa taxa de sobreamostragem, a resolução poderá ser garantida aumentando-se a ordem do filtro de laço ou aumentando a resolução do quantizador (YAN; SANCHEZ-SINENCIO, 2004). De fato haverá melhora na performance do modulador, i.e., aumento da SNR se o filtro de laço for de ordem superior, no entanto, quanto maior a ordem,

o modulador tenderá à instabilidade mais precocemente, ou seja, terá a máxima amplitude do sinal de entrada reduzida, além de ser mais sensível a variações dos coeficientes (SCHREIER; TEMES, 2004).

Outro modo de atingir as especificações do modulador sem utilizar uma alta taxa de sobreamostragem é aumentando a resolução do quantizador. De fato há vários benefícios decorrentes disto, principalmente em relação à estabilidade. Além disso, o aumento da resolução relaxará as especificações de alguns blocos (e.g., *slew rate* dos amplificadores) e, de modo que a estabilidade será beneficiada, o uso de ordens superiores para o filtro de laço poderão ser utilizadas sem tanta restrição. No entanto, assim como o quantizador será *multi-bit*, o DAC também deverá ser projetado *multi-bit* e a sua linearidade definirá a linearidade do modulador, e técnicas para linearização serão necessárias para o projeto do DAC (ROSA; RÍO, 2013).

#### 3.2.3 Topologia de laço único ou cascata

Para aumentar a ordem do filtro de laço sem aumentar a resolução do quantizador e sem prejudicar a estabilidade, também pode-se utilizar topologias em cascata, com dois ou mais estágios contendo laço único, tipicamente de primeira, segunda ou terceira ordem. A ideia básica da topologia em cascata, tendo um modulador com dois estágios como exemplo, é alimentar o segundo estágio com o erro de quantização do primeiro estágio. As saídas digitais de ambos estágios serão combinadas através do cancelamento digital de modo que o erro de quantização do primeiro estágio seja removido e apenas o ruído de quantização do segundo estágio esteja presente na saída (YAN; SANCHEZ-SINENCIO, 2004).

Em topologias em cascata, o casamento perfeito entre a função de transferência NTF e o cancelamento digital faz-se necessário. Sendo assim, topologias em cascata são mais apropriadas para moduladores em tempo discreto implementados com capacitor chaveado. Enquanto que, para tempo contínuo, grandes variações na constante de tempo introduzem descasamento e portanto, degradações bastante significativas na performance do modulador. De outra forma, topologias de laço único são mais tolerantes às variações na constante de tempo, sendo assim, são mais apropriadas para moduladores em tempo contínuo.

#### 3.2.4 Topologia feedforward versus feedback

Há duas topologias que são geralmente utilizadas para moduladores  $\Sigma\Delta$  com laço único, são elas, cascata de integradores com alimentação em avanço (CIFF) e cascata de integrado-

res com realimentação (CIFB) (SCHREIER; TEMES, 2004). A topologia CIFB requer vários DACs, i.e., um DAC para cada realimentação. Na estrutura CIFF, apenas um DAC é necessário, desta forma, ocupa menos área, no entanto, esta topologia requer um somador antes do quantizador. Outra vantagem da topologia CIFF é o pequeno sinal de excursão de saída do primeiro integrador. Com um determinado intervalo de saída, o primeiro integrador permite um ganho no laço maior, e, assim, o requerimento de performance dos outros integradores ficarão mais relaxados (ROSA; RÍO, 2013).

Geralmente a STF de uma topologia CIFF tem um pico fora da banda do sinal. Isto implica que na frequência em que ocorre o pico, a amplitude do sinal de entrada é reduzida pelo ganho do pico. Como resultado, a SNR é reduzida. A topologia CIFB não apresenta este problema pois o seu pico fora da banda é praticamente insignificante (RANJBAR; OLIAEI; JACKSON, 2010).

Além das topologias básicas, pode-se ainda adicionar realimentação local para otimizar os zeros da NTF, de modo a mover o ganho DC dos integradores para um frequência ressonante. Assim, o ganho poderá ser espalhado dentro da banda do sinal, suprimindo o ruído contido dentro desta banda e consequentemente aumentando a performance do modulador. Para implementar a NTF com realimentação local geralmente sintetiza-se o filtro com aproximação de Chebyshev, enquanto que tradicionalmente utiliza-se Butterworth quando não é necessário otimizar os zeros da NTF (BREEMS; HUIJSING, 2001).

#### 3.3 Metodologia de projeto

O fluxograma de projeto do tipo *top-down* foi utilizado neste trabalho. Far-se-á uma breve descrição do procedimento, no entanto, o leitor poderá referir-se a (ROSA; RÍO, 2013) para uma leitura mais aprofundada.

Primeiramente as especificações do modulador deverão estar bem definidas, uma vez que não será possível modificá-las posteriormente sem alterar os blocos projetados. Nesta fase são definidos parâmetros como frequência de amostragem f de modo a obter a taxa de amostragem M, a ordem do filtro L e resolução do quantizador B.

Posteriormente faz-se o projeto das funções de transferência, i.e., da NTF e STF. Neste trabalho foi utilizada a metodologia de síntese direta do filtro reportada em (VIERA et al., 2014). A partir da implementação da NTF e STF, faz-se então uma análise detalhada sobre estabilidade que será apresentada no Capítulo 6.

A NTF e STF poderão, então, ser traduzidas para uma determinada topologia, onde os coeficientes serão obtidos e posteriormente escalonados de modo a garantir a não saturação dos integradores. Novamente, a estabilidade poderá ser verificada através das métricas de performance. Várias simulações são feitas de modo a incluir o comportamento não ideal do blocos que compõem o modulador (e.g., frequência de ganho unitário dos amplificadores), sendo que, a performance e estabilidade devem ser levadas em consideração.

O modulador é então, implementado utilizando descrição comportamental (e.g., VHDL-AMS) em um ambiente de projeto (e.g., Cadence). Após a validação dos modelos comportamentais, inicia-se o projeto dos circuitos. Para este trabalho foi utilizada a tecnologia CMOS 130nm com tensão de alimentação de 1.2V (UMC-130nm). Após o projeto dos circuitos é feita novamente uma verificação utilizando as métricas de performance para garantir que as especificações estão sendo atingidas. Finalmente faz-se o *layout* do circuito e, faz-se novamente uma verificação para garantir a performance. Pode-se observar que, a cada etapa é feita uma verificação de performance e estabilidade do modulador, de modo que seria muito mais difícil resolver qualquer eventual problema caso a etapa de verificação fosse feita apenas no final do projeto.

# 4 PROJETO DO MODULADOR NO NÍVEL DE ABSTRAÇÃO DO SISTEMA

O projeto no nível de abstração do sistema de três moduladores  $\Sigma\Delta$  em tempo contínuo será apresentado neste capítulo que servirá de base para a análise das não-idealidades, apresentadas no Capítulo 5 e de estabilidade apresentada no Capítulo 6.

## 4.1 Especificações

Os moduladores serão projetados para suprir os requisitos para o padrão GSM (JOSE et al., 2007). As especificações são sumarizadas na Tabela 4.1.

Tabela 4.1: Especificações de projeto.

| Padrão Wireless | Banda do sinal | SNR de pico | DR    |

|-----------------|----------------|-------------|-------|

| GSM             | 0,2 MHz        | 78 dB       | 80 dB |

#### 4.2 Parâmetros

Definir os parâmetros no nível de abstração do sistema é o primeiro passo quando do projeto do modulador. Como o objetivo deste trabalho é a comparação entre moduladores de segunda e terceira ordem (L=2,3) com quantizador single bit (B=1), resta apenas definir a taxa de sobreamostragem M. Utilizando a Figura 2.13 e levando em conta a norma infinita ( $\|H\|_{\infty}$ ), pode-se então definir o parâmetro M.  $\|H\|_{\infty}$  será bastante utilizado neste trabalho, desta forma, faz-se necessário defini-lo de modo que o leitor consiga compreender a sua importância durante a análise dos moduladores a serem projetados. Sendo assim,  $\|H\|_{\infty}$  pode ser definido como o valor da atenuação da banda de rejeição ( $stopband\ attenuation$ ) quando da síntese do filtro por uma aproximação de Chebyshev ou Butterworth. Em outras palavras, pode-se definir  $\|H\|_{\infty}$  como sendo o ganho fora da banda do sinal da NTF que é derivada a partir da função de transferência do filtro ( $L_F$ ) obtida pela síntese do filtro. Neste trabalho, o  $\|H\|_{\infty}$  de um dos moduladores de terceira ordem ( $\|H\|_{\infty}=1,16$ ) é escolhido de modo a obter o mesmo overload que o modulador de segunda ordem.

Os parâmetros resultantes são apresentados na Tabela 4.2.

| Ordem (L) | Sobreamostragem (M) | Bits do quantizador (B) | $\ H\ _{\infty}$ |

|-----------|---------------------|-------------------------|------------------|

| 2         | 128                 | 1                       | 1,5              |

| 3         | 80                  | 1                       | 1,5              |

| 3         | 120                 | 1                       | 1,16             |

Tabela 4.2: Parâmetros dos moduladores  $\Sigma\Delta$

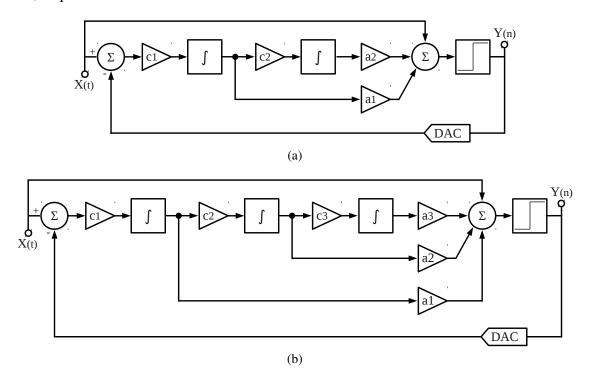

## 4.3 Topologia

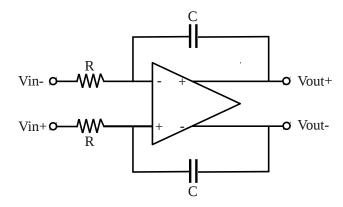

Considerando as vantagens das topologias CIFB e CIFF mencionadas na Seção 3.2.4, escolheu-se a topologia CIFF de modo que esta requer uma menor excursão do sinal de saída do primeiro integrador, facilitando o projeto dos amplificadores no nível de abstração do circuito para baixas tensões de alimentação (GERFERS; ORTMANNS, 2010). As Figuras 4.1a e 4.1b ilustram o diagrama de blocos da topologia CIFF para os moduladores de segunda e terceira ordem, respectivamente.

Figura 4.1: Diagrama de blocos do modulador. (a) Segunda ordem (b) Terceira ordem.

## 4.4 Projeto do laço

O laço do filtro foi diretamente sintetizado em tempo contínuo. As funções de transferência dos laços são definidas como um protótipo no domínio contínuo (VIERA et al., 2014):

$$L_F(s) = \frac{B(s) - A(s)}{A(s)} \tag{4.1}$$

onde B(s) e A(s) são as funções de transferência do filtro de ordem arbitrária.

Então, um filtro do tipo Butterworth ou Chebyshev é sintetizado utilizando tabelas normalizadas de projeto de filtros (WILLIAMS; TAYLOR, 2006) ou algum software como *Matlab* ® ou *Octave*. Desta forma encontram-se as funções de transferência dos laços dos filtros:

$$LF_{2,\|H\|_{\infty}=1,5} = \frac{0.66667(s+0,3246)}{s^2}$$

(4.2)

$$LF_{3,||H||_{\infty}=1,5} = \frac{0.67033(s^2 + 0,3642s + 0,06561)}{s^3}$$

(4.3)

$$LF_{3,\|H\|_{\infty}=1,16} = \frac{0.2761(s^2 + 0, 1429s + 0, 01019)}{s^3}$$

(4.4)

A NTF para um quantizador com ganho unitário poderá então ser descrita como o inverso da função de transferência dos laços (4.2), (4.3) e (4.4), i.e.,

$$NTF(s) = \frac{1}{1 + L_F(s)}$$

(4.5)

onde especificamente, para uma topologia CIFF, a NTF e STF podem ser descritas como (GERFERS; ORTMANNS, 2010):

$$NTF(s) = \frac{1}{1 + \sum_{i=1}^{N} a_{N-i+1} L_F^i(s)}$$

(4.6)

$$STF(s) = \frac{\sum_{i=1}^{N} a_{N-i+1} L_F^i(s)}{1 + \sum_{i=1}^{N} a_{N-i+1} L_F^i(s)}$$

(4.7)

Utilizando (4.6) e (4.7), pode-se então encontrar os coeficientes para a topologia CIFF. A Tabela 4.3 mostra os coeficientes resultantes para os três moduladores tendo em vista que esses já foram escalonados de modo a garantir que os integradores não saturem.

Tabela 4.3: Coeficientes dos moduladores  $\Sigma\Delta$  em CT.

| Ordem (L)                 | $\mathbf{a_1}$ | $\mathbf{a_2}$ | $\mathbf{a_3}$ | $c_1$ | $\mathbf{c_2}$ | $\mathbf{c_3}$ |

|---------------------------|----------------|----------------|----------------|-------|----------------|----------------|

| $2_{\ H\ _{\infty}=1,5}$  | 1,31           | 3,75           | -              | 0,51  | 0,11           | -              |

| $3_{\ H\ _{\infty}=1,5}$  | 2,82           | 4,56           | 6,61           | 0,24  | 0,23           | 0,12           |

| $3_{\ H\ _{\infty}=1,16}$ | 1,22           | 2,33           | 3,97           | 0,23  | 0,07           | 0,04           |

## 5 ANÁLISE, MODELAGEM E EFEITOS DAS NÃO-IDEALIDADES DE MODULADORES $\Sigma\Delta$ EM CT

Neste capítulo serão apresentadas as não-idealidades que afetam  $\Sigma \Delta M$  em tempo contínuo de modo a garantir que a performance do modulador seja garantida. Estas serão modeladas em Matlab/Simulink® e VHDL-AMS. A partir das não-idealidades, as especificações dos blocos são obtidas e utilizadas para o projeto no nível de abstração do circuito.

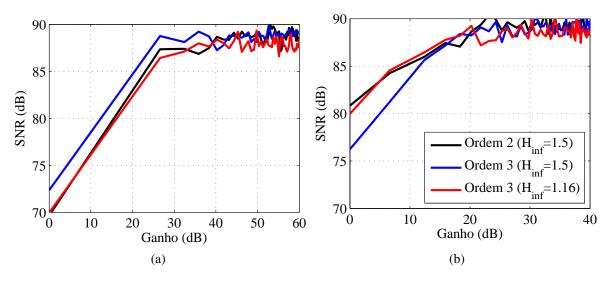

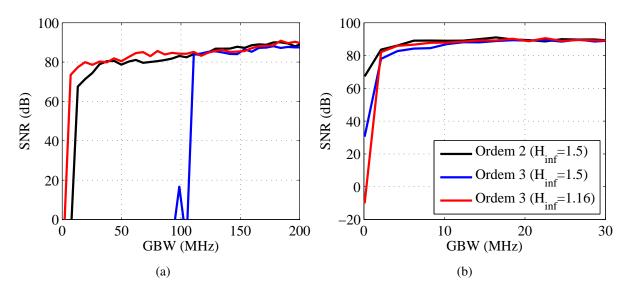

As simulações efetuadas neste capítulo levam em conta as especificações da Tabela 4.1. Note que a SNR das simulações será de aproximadamente 90 dB e não 80 dB como está nas especificações, isto ocorre pois provavelmente haverá perda na performance do modulador quando este for implementado eletricamente e, portanto, de modo a garantir que as especificações sejam cumpridas, neste trabalho os moduladores no nível de abstração do sistema serão projetados com  $\approx 10$  dB a mais que a especificação.

#### 5.1 Clock Jitter

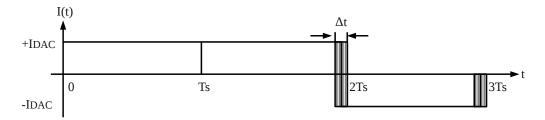

Clock jitter causa uma pequena variação randômica na quantidade de carga realimentada por ciclo de clock, ou seja, uma variação estatística da forma de onda do sinal de realimentação resulta em um erro de integração também estatístico, sendo assim, o noise floor irá aumentar e a resolução do modulador diminuirá.

No sistema existem duas fontes de clock jitter, uma na entrada do ADC e outra que é gerada através do erro de timing do DAC de realimentação no laço principal. O jitter presente no DAC de realimentação é mais crítico, desta forma, apenas este será considerado. O erro causado pelo jitter é o erro na área do sinal de pulso na realimentação para cada período de amostragem (CHERRY; SNELGROVE, 2000). A razão disto é que o pulso na realimentação é integrado ao menos uma vez no laço de filtro. Este valor integrado corresponde com a área do pulso, e assim, apenas a área é significante nos instantes da amostragem e não o formato do pulso. Em (GERFERS; ORTMANNS, 2010) é feita uma análise detalhada sobre o efeito do clock jitter na performance do  $\Sigma\Delta M$  em tempo contínuo e discreto.

A Figura 5.1 ilustra o efeito do *jitter* no sinal do laço de realimentação do modulador considerando um pulso do tipo NRZ. Pode-se observar na figura o defasamento (incerteza) do sinal na borda de transição deste. Esta incerteza de largura  $\Delta t$ , é, justamente o efeito do *jitter* sobre o sinal.

Figura 5.1: Efeito do *jitter* no sinal do DAC.

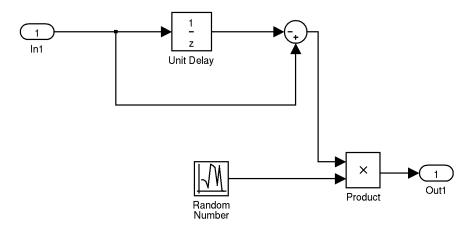

A Figura 5.2 ilustra o modelo do *jitter* que é introduzido no laço de realimentação do modulador. A variação do sinal é gerada através de uma fonte de ruído *Random Number*.

Figura 5.2: Modelagem do *jitter* em Matlab/Simulink®.

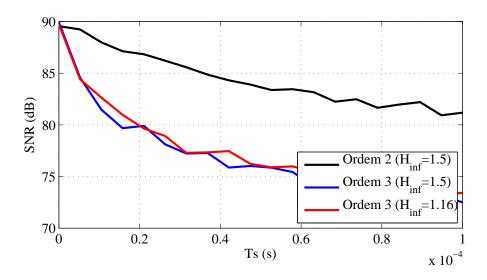

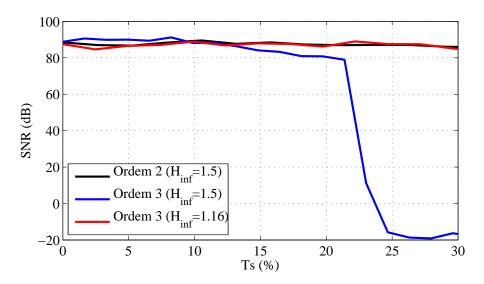

A Figura 5.3 ilustra o efeito do *clock jitter* na performance do modulador. Pode ser observado que os moduladores de terceira ordem sofrem mais perda de SNR com o *clock jitter* que o modulador de segunda ordem.

Figura 5.3: Efeito do jitter na performance do modulador.

## 5.2 Excess loop delay

O Excess loop delay (ELD) decorre do fato de o tempo de chaveamento do transistor não ser nulo, o que faz com que a borda de transição do pulso do DAC comece depois da borda de transição do clock, além disso, comparadores reais tem um certo tempo para gerar a saída correta do sinal que será realimentado. O atraso gerado pode ser determinado pelo projeto do quantizador no nível de abstração do circuito, juntamente com o tempo finito para o DAC responder, mais o atraso entre a borda de transição do clock do quantizador e uma saída válida do DAC. Desta forma, faz-se necessário que a tolerância que o modulador terá ao ELD seja determinada. Se o atraso suportado for menor que o atraso gerado, então deverá ser empregada alguma técnica para compensação ao ELD. Uma compensação clássica é adicionar um caminho de realimentação extra da saída do modulador à entrada do quantizador (ROSA; RÍO, 2013).

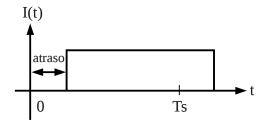

A Figura 5.4 ilustra o efeito do ELD no sinal do laço de realimentação considerando uma fração da forma de onda da Figura 5.1.

Figura 5.4: Efeito do ELD no sinal de realimentação do sistema.

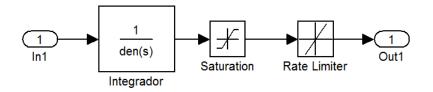

O ELD pode ser modelado com um bloco do tipo *Transport Delay* inserido na malha de realimentação do modulador, i.e., entre a saída do quantizador e a entrada do modulador. A Figura 5.5 ilustra o bloco utilizado para modelar o ELD a nível de sistema.

Figura 5.5: Modelagem do ELD em Matlab/Simulink®.

O principal problema causado pelo ELD refere-se à instabilidade do modulador. O ELD em um sistema com uma NTF mais agressiva fará com que o modulador fique instável mais facilmente. A Figura 5.6 ilustra a tolerância ao ELD para os três moduladores. Percebe-se nesta figura que para o modulador de terceira ordem com a NTF mais agressiva, o sistema é menos

tolerante ao ELD, enquanto a NTF com ganho moderado e o modulador de segunda ordem atingem a especificação mesmo com um ELD de ao menos 30% do período do relógio, na qual sobra margem suficiente para outras não-idealidades e não-linearidades inerentes ao circuito.

Figura 5.6: Efeito do ELD na performance do modulador.

## 5.3 Ganho finito dos amplificadores