# Conversor de Alto Ganho de Tensão Dual Boost Quadrático

Wagner de Azevedo Ayres\*, Éder Bridi\*, Hamiltom Confortin Sartori\* e José Renes Pinheiro\*

\*Grupo de Eletrônica de Potência e Controle - GEPOC

Centro de Tecnologia - CT

Universidade Federal de Santa Maria - UFSM

Santa Maria - RS, Brasil

E-mails: wagner.ayres@gmail.com, ederbridi@gmail.com, hamiltomsar@gmail.com, jrenes@gepoc.ufsm.br

Resumo—Conversores CC-CC são usados constantemente em muitas aplicações, dentre elas, as com fontes de energia renovavéis como painéis fotovoltaicos e células a combustíveis. Neste artigo é apresentada uma nova configuração para a topologia CC-CC do conversor boost quadrático. A topologia Dual Boost Quadrático é desenvolvida de modo a obter alto ganho de tensão, necessário as aplicações fotovoltaicas e se torna um excelente candidato para o estágio CC-CC de microinversores. Além disso, essa configuração diminui os esforços nos componentes do circuito, como é explicitado nos resultados, garantindo uma melhor performance para o conversor.

Index Terms—conversores CC-CC; boost quadrático; alto ganho; dual.

## I. INTRODUÇÃO

Energia solar fotovoltaica tem chamado a atenção nos últimos tempos como alternativa para diversificar a matriz energética à partir da geração distribuída, visando suprir a demanda crescente de eletricidade [1], [2]. Sistemas fotovoltaicos possuem certas características que merecem atenção: suprimento intermitente de energia devido as variações do meio ambiente; exigência de um alto ganho de tensão do conversor CC-CC, visto que os painéis fornecem normalmente baixas tensões em relação a tensão consumida pela carga; necessidade de regulação de tensão com variação de carga e baixa amplitude de ondulação de corrente de entrada [6]–[8].

O caso particular de sistemas fotovoltaicos que utilizam módulos CA ou microinversores, a questão do volume e eficiência do conversor também são parâmetros importantes para definição da topologia empregada, além de cumprir os requisitos anteriormente citados.

Se tratando de elevação de tensão, uma das topologias mais utilizadas é a topologia *boost*. Este conversor possui um número pequeno de componentes, é de simples construção, não-isolado e de baixo custo. Idealmente, o conversor *boost* alcança um elevado ganho de tensão que na prática é limitado pelas resistências intrínsecas de cada componente do circuito; o que interfere diretamente nas perdas e na eficiência do conversor. Somado a isso, há um estresse muito grande na chave do conversor pois a razão cíclica de trabalho se torna elevada para alcançar um ganho elevado [3], [9].

Existem outras técnicas aplicadas ao conversor *boost*, citando como exemplo o uso de capacitor e indutor chaveado, células multiplicadoras de tensão, indutores acoplados, uso de transformadores e etc. Dependendo da aplicação a inclusão de muitos componentes não torna a topologia do conversor muito atrativa. Aumenta também a dificuldade no projeto de

controladores com a inclusão de mais componentes acumuladores de energia [4].

Outra forma de elevar o ganho de tensão do conversor boost clássico é adicionar um novo estágio elevador. Conversor conhecido como boost cascata, possui também uma configuração simples, porém opera com duas chaves e dois diodos. O esforço nos componentes do primeiro estágio é menor comparado ao segundo estágio [5].

Eliminando um interruptor do conversor *boost* cascata obtém-se a topologia do conversor *boost* quadrático, o que implica no mesmo ciclo de trabalho para os interruptores dos dois estágios. Usualmente o *boost* quadrático é utilizado quando se deseja tensões elevadas na carga e um alto valor de ganho estático, assim, essas duas características fazem com que a chave tenha que suportar uma tensão elevada durante o bloqueio e que consiga conduzir uma corrente elevada. Esses fatores exigem um semicondutor mais robusto, o que pode encarecer o projeto final do conversor, além de aumentar a potência dissipada na chave. Assim, possui vantagens para aplicações de baixa potência [4].

A partir do exposto, é proposta a topologia dual *boost* quadrático. Esta topologia combina as qualidades do conversor *boost* quadrático convencional, mas oferece um ganho de tensão elevado utilizando um menor ciclo de trabalho dos interruptores. Ainda, diminui os esforços de corrente nas chaves, já que a corrente total do circuito é dividida nos dois estágios distintos.

# II. ANÁLISE DO CONVERSOR DUAL BOOST QUADRÁTICO

## A. Princípio de Funcionamento

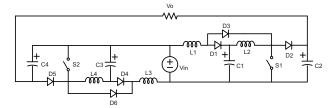

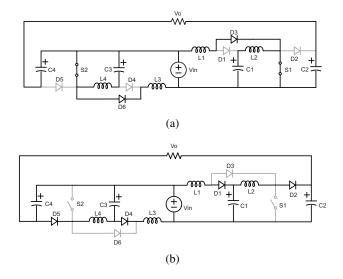

A Figura 1 apresenta o conversor dual *boost* quadrático. Esse conversor é composto por duas topologias *boost* quadráticas com ligação em modo diferencial com a fonte de alimentação. Em relação a análise desse conversor, as seguintes considerações são feitas: o conversor opera em regime permanente; os capacitores possuem capacitâncias altas, logo são livres de ondulações; os componentes possuem comportamento ideal, isto é, livre de perdas e parasitas.

A topologia apresentada possui duas etapas de operação. Na primeira etapa, os indutores são magnetizados e na segunda etapa os indutores são desmagnetizados. As principais formas de ondas deste conversor são apresentadas na Figura 3.

Etapa 1  $[t_0-t_1]$  (Figura 2(a)): Essa etapa inicia quando os interruptores  $S_1$  e  $S_2$  entram em condução. Os indutores  $L_1$

e  $L_3$  são magnetizados através da tensão da fonte de entrada  $v_{in}$ , enquanto que os indutores  $L_2$  e  $L_4$  são magnetizados através das tensões dos capacitores  $V_{C1}$  e  $V_{C3}$ , respectivamente. Os diodos  $D_3$  e  $D_6$  estão diretamente polarizados, enquanto os diodos  $D_1$ ,  $D_2$ ,  $D_4$ ,  $D_5$  estão bloqueados. A tensão de saída  $V_o$  é dada de forma diferencial com as tensões dos capacitores  $C_2$  e  $C_4$ , isto é,  $V_0 = V_{C4} + V_{C2} - V_{I1}$ . Esta etapa termina quando os interruptores são bloqueados.

Etapa 2  $[t_1-T_s]$  (Figura 2(b)): Essa etapa inicia quando os interruptores  $S_1$  e  $S_2$  são bloqueados. Os indutores  $L_1$  e  $L_3$  são desmagnetizados através da tensão de entrada  $V_{in}-V_{C1}$  e  $V_{in}-V_{C3}$ , respectivamente, enquanto que os indutores  $L_2$  e  $L_4$  são desmagnetizados através da tensão dos capacitores  $V_{C1}-V_{C2}$  e  $V_{C3}-V_{C4}$ , na devida ordem. Os diodos  $D_3$  e  $D_6$  estão reversamente polarizados, enquanto que os diodos  $D_1$ ,  $D_2$ ,  $D_4$ ,  $D_5$  entram em condução. A tensão de saída  $V_o$  é dada de forma diferencial com as tensões dos capacitores  $C_2$  e  $C_4$ , isto é,  $V_0 = V_{C4} + V_{C2} - V_{in}$ . Ao término desta etapa se conclui um período de chaveamento.

## B. Ganho Estático de Tensão

Conforme foi apresentado anteriormente, a tensão de saída do conversor Dual *Boost* Quadrático é dada por (1).

$$Vo = (Vc_1 + Vc_2) - Vin \tag{1}$$

Observa-se através da Figura 1, que a tensão dos capacitores  $C_2$  e  $C_4$  é igual a  $\frac{1}{(1-D)^2}$ . Essa tensão representa o valor de tensão para um conversor *boost* quadrático. Assim, a expressão (1) pode ser reescrita de acordo com (2)

Figura 1: Conversor Dual Boost Quadrático.

Figura 2: Etapas de operação do conversor proposto. (a) Etapa 1. (b) Etapa 2.

$$V_o = \left(\frac{1}{(1-D)^2}V_{in} + \frac{1}{(1-D)^2}V_{in}\right) - V_{in}$$

(2)

Simplificando (2), o ganho do conversor é definido por:

$$M = \frac{V_o}{V_{in}} = \frac{2}{(1-D)^2} - 1 \tag{3}$$

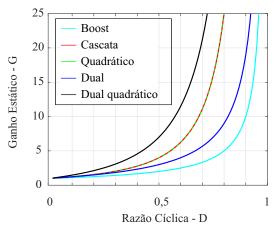

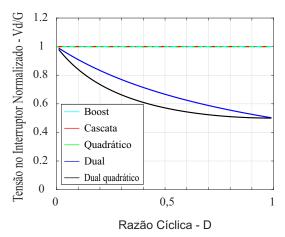

A Figura 4 mostra uma comparação de ganhos estáticos de outras topologias do tipo *boost*. Dentre as estruturas apresentadas, o conversor proposto apresenta o maior ganho de tensão em toda faixa da razão cíclica (*D*). Além disso, deve ser ressaltado que os conversores *boost* quadrático e cascata possuem o mesmo ganho de tensão e os gráficos então se sobrepõem.

# C. Análise Comparativa

Com o intuito de avaliar o desempenho do conversor apresentado em relação a outras topologias *boost* já bem difundidas na literatura, a Tabela I apresenta uma análise comparativa. Os conversores avaliados são: Conversor *Boost*; Conversor *Boost* Cascata; Conversor *Boost* Quadrático; Conversor *Boost* Diferencial e por fim, o Dual *Boost* Quadrático (dif.quad). Como pode ser visto, cada um dos conversores apresenta suas características de esforços de tensão.

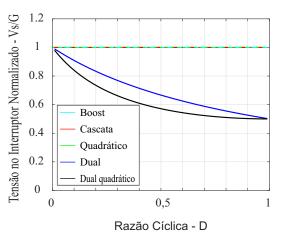

A Figura 5 ilustra o esforço de tensão nos interruptores dos conversores citados normalizado pelo ganho de tensão para diferentes valores de razão cíclica. Nesta Figura 5 fica evidente que o esforço de tensão nos interruptores do conversor proposto é menor para toda faixa da razão cíclica, isto é, para o mesmo ganho de tensão, significa que os esforços de tensão nos interruptores ( $V_{S1}$  e  $V_{S2}$ ) do conversor apresentado é sempre menor comparado as outras topologias. Consequentemente, no projeto do conversor, a tecnologia de interruptores CMOS utilizada possuirá menor valor de  $R_{DS(on)}$ , o que contribui para o bom rendimento da topologia.

Executando o mesmo tipo de análise para os diodos de saída dos conversores *boost*, tem-se que o esforço de tensão

Figura 3: Principais formas de onda do conversor proposto.

Tabela I: Comparação das topologias boost.

| Conversor                           | Ganho estático  M                  | Esforço de tensão nos interruptores $V_s$ | Esforço de tensão nos diodos de saída $V_D$ |

|-------------------------------------|------------------------------------|-------------------------------------------|---------------------------------------------|

| Boost                               | $\frac{1}{1-D}$                    | $\frac{1}{1-D}$                           | $\frac{1}{1-D}$                             |

| Boost Cascata e<br>Boost Quadrático | $\frac{1}{(1-D)^2}$                | $\frac{1}{\left(1-D\right)^2}$            | $\frac{1}{\left(1-D\right)^2}$              |

| Boost Diferencial                   | $\frac{2}{1-D}-1$                  | $\frac{2}{1-D}-1$                         | $\frac{2}{1-D}-1$                           |

| Boost Quadrático<br>Diferencial     | $\frac{2}{\left(1-D\right)^2} - 1$ | $\frac{2}{\left(1-D\right)^2}-1$          | $\frac{2}{\left(1-D\right)^2}-1$            |

nesses diodos é normalizado pelo ganho de tensão. Através da Figura 6, o esforço de tensão nos diodos de saída do conversor *boost* quadrático, é menor para toda faixa da razão cíclica. Assim, para o mesmo ganho de tensão, significa que o esforço de tensão nos diodos ( $V_{D2}$  e  $V_{D5}$ ) do conversor proposto é sempre menor que as outras topologias *boost*. Do mesmo modo, no momento do projeto do conversor, o diodo utilizado possuirá menor valor de  $V_F$ , o que também agrega na conservação do rendimento da topologia.

# D. Metodologia de Projeto

Os valores de indutância e capacitância utilizados no conversor em questão são encontrados através das equações dos componentes. As expressões a seguir relacionam, no caso dos indutores, tensão e a variação de corrente  $\Delta_i$ . Para o caso dos capacitores, a relação se dá através da corrente e taxa de variação de tensão  $\Delta_V$ .

$$L_1 = L_3 = \frac{VinD}{f_s \Delta i_{L1;3}} \tag{4}$$

$$L_2 = L_4 = \frac{VinD}{(1 - D)f_s \Delta i_{L2:4}}$$

(5)

$$C_1 = C_3 = \frac{I_{in}D(1-D)}{f_s\Delta V_{c_1:3}}$$

(6)

Figura 4: Comparativo dos ganhos estáticos de tensão

Tabela II: Parâmetros de Simulação

| Parâmetro | Valor       |

|-----------|-------------|

| $P_{in}$  | 315W        |

| $V_{in}$  | 36,6V       |

| $I_{in}$  | 8,61A       |

| $V_o$     | 400V        |

| $I_o$     | 0,79A       |

| R         | $508\Omega$ |

$$C_2 = C_4 = \frac{I_o D}{f_s \Delta V_{c_{2;4}}} \tag{7}$$

### III. RESULTADOS DE SIMULAÇÃO

Nesta seção são apresentados os resultados de simulação. A Tabela II relaciona os parâmetros utilizados para a simulação. Vale salientar que os parâmetros de tensão e corrente de entrada são referentes a um painel fotovoltaico de 315W. A tensão de saída especificada (400V) é referente a um barramento CC padrão para aplicações fotovoltaicas monofásicas, onde a tensão rms de saída aplicada a carga é de 220V. A Tabela III mostra os valores dos componentes do circuito conversor.

Figura 5: Esforço de tensão nos interruptores normalizada vs razão cíclica

Figura 6: Esforço de tensão nos diodos de saída normalizada vs razão cíclica

Tabela III: Parâmetros de Simulação

| Parâmetro         | Valor        |

|-------------------|--------------|

| $L_{1;3}$         | $495\mu H$   |

| $L_{2;4}$         | 5,63mH       |

| $C_{1;3}$         | $24,88\mu F$ |

| $C_{2;4}$         | $2,48\mu F$  |

| $\Delta I_{L1;3}$ | 0,74A        |

| $\Delta I_{L2;4}$ | 0,16A        |

| $\Delta V_{C1;3}$ | 1,4V         |

| $\Delta V_{C2;4}$ | 3,22V        |

| $f_s$             | 60kHz        |

| D                 | 0,6          |

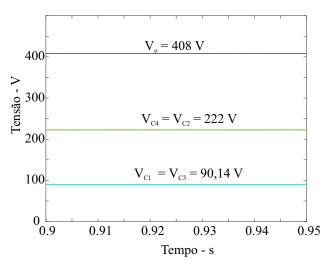

A Figura 7 mostra a tensão de saída do conversor apresentado. O valor encontrado é 11 vezes maior que o especificado na entrada do conversor, o que justifica o alto ganho de tensão alcançado com essa topologia. A Figura 7 também evidencia as tensões nos capacitores do conversor.

Figura 7: Tensão de Saída Diferencial; Tensão nos capacito-

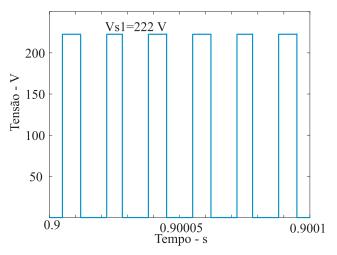

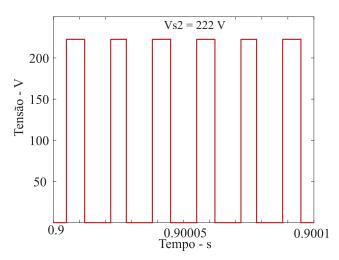

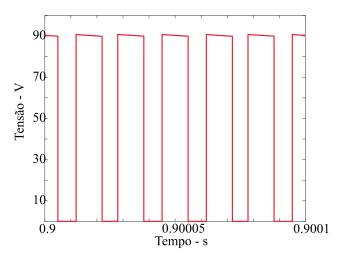

As Figuras 8 e 9 apresentam as tensões sobre as chaves do conversor. Nota-se que os valores de tensão são a metade

do valor de tensão de saída, o que é um benefício para o projeto pois pode-se utilizar um semicondutor de tensão menor, reduzindo o custo final de projeto.

Figura 8: Tensão na Chave  $S_1$ .

Figura 9: Tensão na Chave  $S_2$ .

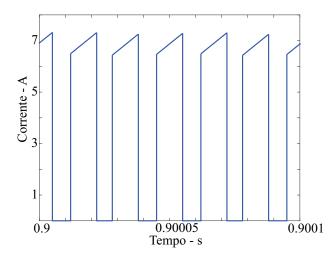

A Figura 10 apresenta as correntes nos interruptores S1 e S2. Percebe-se que a corrente nominal do conversor foi dividida nos dois estágios o que reflete em benefício para a topologia, visto que as perdas de condução serão menores.

Seguindo esta análise, é apresentado na Figura 11 o esforço de tensão do diodo D1. Percebe-se que o valor de saída é quatro vezes menor que o valor final de tensão.

Figura 10: Corrente nos Interruptores  $S_1$  e  $S_2$

Figura 11: Tensão no Diodo  $D_1$ .

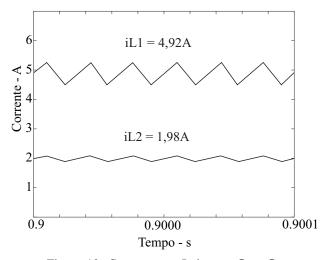

A corrente drenada da fonte Vin tem valor nominal de 8,61A. Como pode ser visto através da Figura 12, o valor de corrente para o indutor de entrada é praticamente a metade do valor total, o que faz com que as perdas se tornem menores.

Figura 12: Corrente nos Indutores  $L_1$  e  $L_2$

#### IV. CONCLUSÕES

Este artigo apresenta a topologia Dual *Boost* Quadrático. A partir do exposto, percebe-se que a topologia apresenta vantagens e vem a ser um excelente candidato para estágio CC-CC de microinversores fotovoltaicos. Topologia comparada com as demais estruturas *boost* obtém um ganho elevado de tensão com a menor razão cíclica. A corrente de entrada é dividida nos dois estágios, diminuindo as perdas de condução. Os esforços de tensão nas chaves são menores pois cada estágio quadrático amplifica uma parcela da tensão final. As perdas de condução são menores para toda a faixa de razão cíclica e é uma estrutura simples e de baixo custo, haja visto a redução dos esforços nos componentes do circuito.

#### V. AGRADECIMENTOS

Os autores gostariam de expressar sua gratidão a CA-PES/PROEX e ao projeto INCT-GD e aos órgãos financiadores (CNPq processo 465640/2014-1, CAPES processo no. 23038.000776/2017-54 e FAPERGS 17/2551-0000517-1). Os autores também agradecem aos colegas António Spencer, Tiago Faistel, Ronaldo Guisso, Everson Mattos pelas contribuições na execução do trabalho.

## REFERÊNCIAS

- S. Balci, N. Altin, H. Komurcugil and I. Sefa, "Performance analysis of interleaved quadratic boost converter with coupled inductor for fuel cell applications,"IECON 2016 - 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, 2016, pp. 3541-3546.

- [2] F. Blaabjerg, Zhe Chen and S. B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," in IEEE Transactions on Power Electronics, vol. 19, no. 5, pp. 1184-1194, Sept. 2004. doi: 10.1109/TPEL.2004.833453

- [3] S. Choi, V. G. Agelidis, J. Yang, D. Coutellier and P. Marabeas, "Analysis, design and experimental results of a floating-output interleaved-input boost-derived DC-DC high-gain transformer-less converter," in IET Power Electronics, vol. 4, no. 1, pp. 168-180, January 2011. doi: 10.1049/iet-pel.2009.0339

- [4] M. Forouzesh, Y. P. Siwakoti, S. A. Gorji, F. Blaabjerg and B. Lehman, "Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications,"in IEEE Transactions on Power Electronics, vol. 32, no. 12, pp. 9143-9178, Dec. 2017. doi: 10.1109/TPEL.2017.2652318

- [5] A. M. S. S. Andrade, L. Schuch and M. Martins, "Analysis and Design of High-Efficiency Hybrid High Step-Up DC-DC Converter for Distributed PV Generation Systems,"in IEEE Transactions on Industrial Electronics. doi: 10.1109/TIE.2018.2840496

- [6] A. M. S. S. Andrade and M. L. d. S. Martins, "Quadratic-Boost With Stacked Zeta Converter for High Voltage Gain Applications," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 5, no. 4, pp. 1787-1796, Dec. 2017.

- [7] A. M. S. S. Andrade, H. L. Hey, L. Schuch and M. L. da Silva Martins, "Comparative Evaluation of Single Switch High-Voltage Step-Up Topologies Based on Boost and Zeta PWM Cells,"in IEEE Transactions on Industrial Electronics, vol. 65, no. 3, pp. 2322-2334, March 2018. doi: 10.1109/TIE.2017.2745467

- [8] A. M. S. S. Andrade, E. Mattos, L. Schuch, H. L. Hey and M. L. da Silva Martins, "Synthesis and Comparative Analysis of Very High Step-Up DC-DC Converters Adopting Coupled-Inductor and Voltage Multiplier Cells,"in IEEE Transactions on Power Electronics, vol. 33, no. 7, pp. 5880-5897, July 2018.

- [9] R. W. Érickson D. Maksimovic Fundamentals of Power Electronics New York NY USA:Springer 2001.