## UNIVERSIDADE FEDERAL DE SANTA MARIA CENTRO DE TECNOLOGIA CURSO DE GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Davi Sehnem Castro

PROJETO DE COMPARADORES STRONGARM COM CALIBRAÇÃO DE OFFSET

#### Davi Sehnem Castro

# PROJETO DE COMPARADORES *STRONGARM*COM CALIBRAÇÃO DE *OFFSET*

Trabalho de Conclusão de Curso apresentado ao Curso de Graduação em Engenharia Elétrica, Área de Concentração em Microeletrônica, da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para obtenção do grau de **Bacharel em Engenharia Elétrica**.

Orientador: Prof. Maurício Banaszeski Da Silva

#### **Davi Sehnem Castro**

# PROJETO DE COMPARADORES STRONGARM COM CALIBRAÇÃO DE OFFSET

Trabalho de Conclusão de Curso apresentado ao Curso de Graduação em Engenharia Elétrica, Área de Concentração em Microeletrônica, da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para obtenção do grau de **Bacharel em Engenharia Elétrica**.

| Aprovado em 20 de dezembro de 2023:                                 |

|---------------------------------------------------------------------|

| Maurício Banaszeski Da Silva, Dr. (UFSM)<br>(Presidente/Orientador) |

| André Luiz Aita, Dr. (UFSM)                                         |

| Hamilton Duarte Klimach, Dr. (UFRGS)                                |

#### **RESUMO**

# PROJETO DE COMPARADORES STRONGARM COM CALIBRAÇÃO DE OFFSET

AUTOR: Davi Sehnem Castro Orientador: Maurício Banaszeski Da Silva

Comparadores são circuitos que, dado duas entradas de sinal, retornam como resultado um valor referente a qual destes sinais possui maior magnitude. Este comportamento faz com que o comparador seja uma peça fundamental no projeto de conversores analógicos digitais (ADCs), já que pode-se entendê-lo como um circuito que leva entradas analógicas para uma saída digital. Dado o avanço das tecnologias de fabricação de circuitos integrados, bem como a demanda crescente de dispositivos móveis e de loT, é cada vez mais necessário reduzir o consumo e a área demandada pelos componentes, sem comprometer suas características de velocidade e precisão. Entretanto, estas características de operação são normalmente antagônicas, fazendo com que escolhas de projeto feitas com o intuito de melhorar uma certa característica, possa ter consequências indesejadas a uma outra. Para o comparador, a redução da área está diretamente relacionada com a redução da potência consumida, ao mesmo tempo que aumenta a taxa de erros de comparação. Portanto, faz-se necessário conhecer as interdependências entre cada um dos parâmetros de operação do comparador de forma a garantir o projeto ótimo do circuito para a aplicação desejada. A partir desta situação, este trabalho tem por objetivo relacionar os parâmetros de operação de um comparador da topologia StrongARM em função de uma variável comum e, a partir disso, propor uma metodologia de projeto capaz de atender as especificações da aplicação desejada, ao combinar o dimensionamento do comparador com o projeto de um circuito auxiliar para a compensação de offset. Como resultado, foi possível projetar um comparador com calibração com uma área estimada 95 vezes menor, e com dissipação de potência 55 vezes menor, para um requisito de precisão três maior que o comparador sem calibração projetado.

Palavras-chave: Comparador. StrongARM. Offset. Calibração.

#### **ABSTRACT**

# DESIGN OF STRONGARM COMPARATOR WITH OFFSET CALIBRATION

AUTHOR: Davi Sehnem Castro ADVISOR: Maurício Banaszeski Da Silva

Comparators are circuits that, given two signal inputs, return as a result a value referring to which of these signals has greater magnitude. This behavior makes the comparator a key component in the design of analog-to-digital converters (ADCs), as it can be understood as a circuit that takes analog inputs to a digital output. With the advancement of integrated circuit manufacturing technologies, as well as the increasing demand for mobile and IoT devices, it is increasingly necessary to reduce power consumption and the area required by components, without compromising their speed and accuracy characteristics. However, these operational characteristics are typically antagonistic, causing design choices made to improve one characteristic to have unintended consequences on another. For the comparator, reducing the area is directly related to reducing power consumption while increasing the error rate in comparison. Therefore, it is necessary to understand the interdependencies between each of the comparator's operating parameters in order to ensure the optimal circuit design for the desired application. From this perspective, this work aims to relate the operating parameters of a StrongARM topology comparator as a function of a common variable and, based on this, propose a design methodology capable of meeting the specifications of the desired application by combining the sizing of the comparator with the design of an auxiliary circuit for offset compensation. As a result, it was possible to design a calibrated comparator with an estimated area 95 times smaller, and 55 times lower power dissipation, meeting a precision requirement three times higher than the original uncalibrated comparator designed.

**Keywords:** Comparator. StrongARM. Offset. Calibration

### **LISTA DE FIGURAS**

| Figura 1 – Comparador <i>StrongArm</i>                                                               | 11 |

|------------------------------------------------------------------------------------------------------|----|

| Figura 2 – Ciclo de Operação Característico                                                          | 13 |

| Figura 3 - Circuito Equivalente de Modo Comum (a) e Pequenos Sinais (b) Durante o                    |    |

| Sampling                                                                                             | 14 |

| Figura 4 – Circuito Equivalente de Modo Comum Durante a Propagação                                   | 15 |

| Figura 5 – Meio Circuito Equivalente de Modo Comum Durante a Propagação                              | 16 |

| Figura 6 – Circuito Isolado Durante a Propagação                                                     | 17 |

| Figura 7 – Circuito Isolado da Etapa de Regeneração                                                  | 18 |

| Figura 8 – Meio Circuito Equivalente de Pequenos Sinais Durante a Regeneração                        | 18 |

| Figura 9 – Representação do <i>Mismatch</i> no Comparador                                            | 26 |

| Figura 10 – Probabilidade de a Comparação Resultar em '1' ou '0' Devido a um Des-                    |    |

| balanço $V_{in_1} - V_{in_2}$                                                                        | 30 |

| Figura 11 – Capacitâncias para a Análise do kickback noise                                           | 31 |

| Figura 12 – Transistor Normal - $\sigma(\Delta V_{th})$ Simulado e $\sigma(\Delta V_{th})$ Calculado | 34 |

| Figura 13 – Transistor lvt - $\sigma(\Delta V_{th})$ Simulado e $\sigma(\Delta V_{th})$ Calculado    | 35 |

| Figura 14 – Ganho da Etapa de $Sampling \ A_{v_{\rm smp}}$ no Tempo para Diferentes Larguras de      |    |

| Canal $W_0$                                                                                          | 38 |

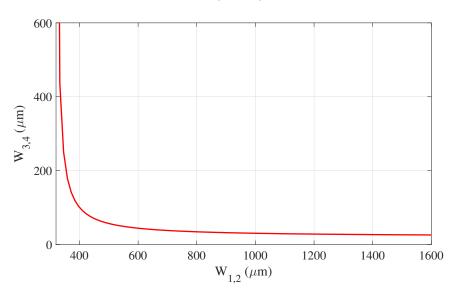

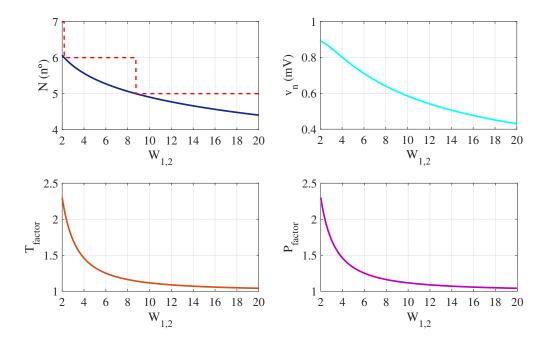

| Figura 15 – Relação entre $W_{1,2}$ e $W_{3,4}$ para atingir $V_{\rm os}=1.5mV$                      | 40 |

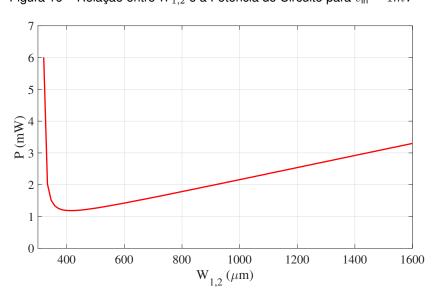

| Figura 16 – Relação entre $W_{1,2}$ e a Potência do Circuito para $v_{\sf in}=1mV$                   | 40 |

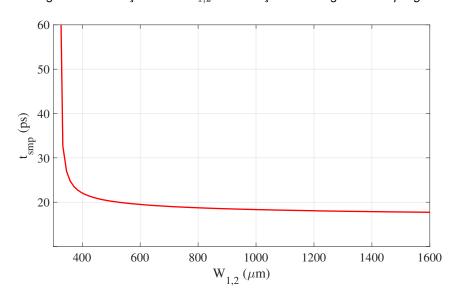

| Figura 17 – Relação entre $W_{1,2}$ e a Duração do Estágio de $\emph{Sampling}$                      | 41 |

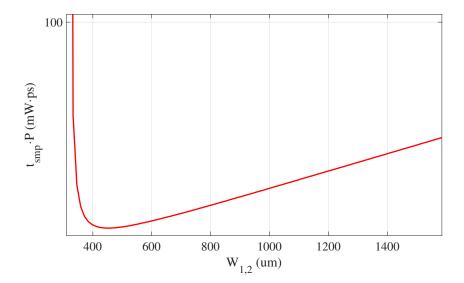

| Figura 18 – Relação entre $W_{1,2}$ e o Produto entre a Potência e a Duração do Estágio              |    |

| de Sampling                                                                                          | 42 |

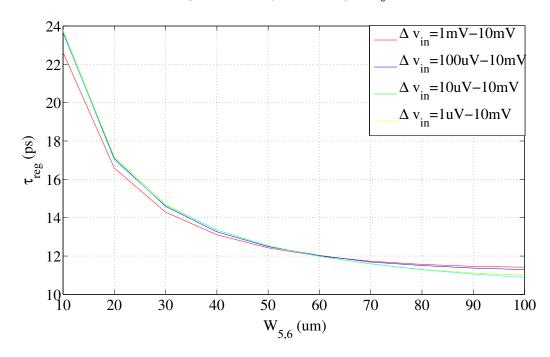

| Figura 19 – Relação entre $W_{5,6}$ e $	au_{\mathrm{reg}}$                                           | 43 |

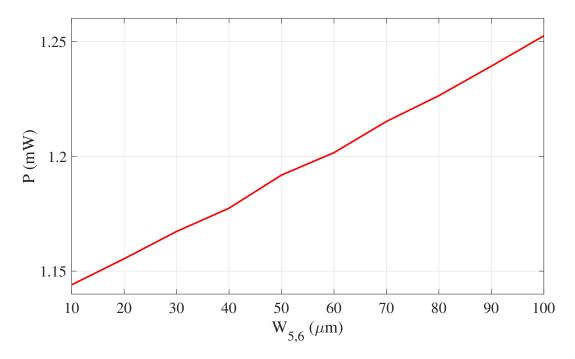

| Figura 20 – Relação entre $W_{5,6}$ e a Potência Dissipada para $v_{in}=10mV$                        | 44 |

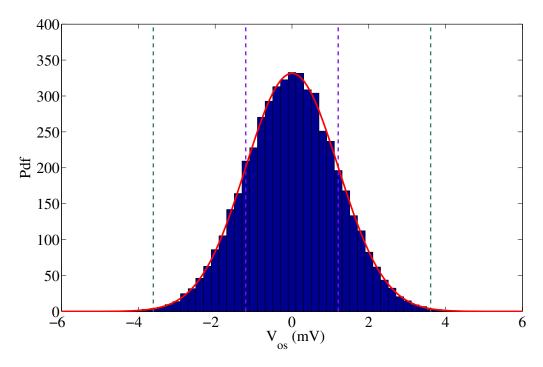

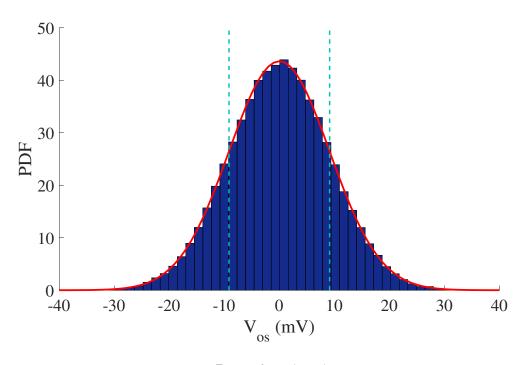

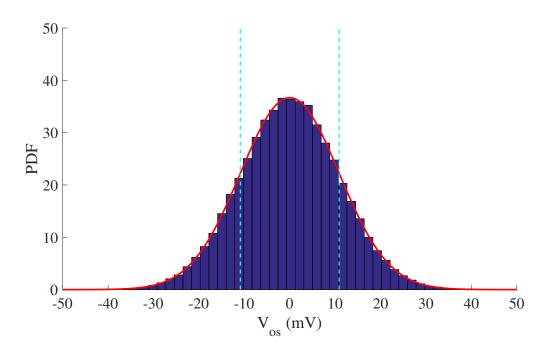

| Figura 21 – PDF do <i>Offset</i> do Comparador                                                       | 46 |

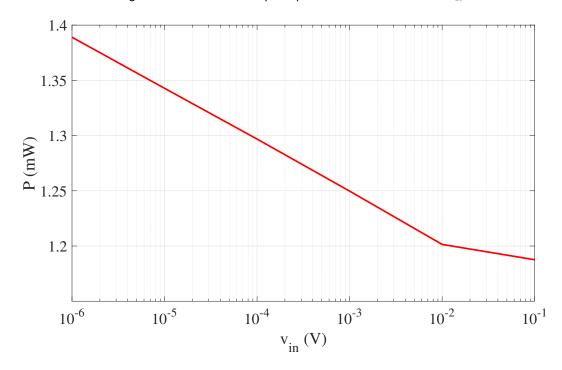

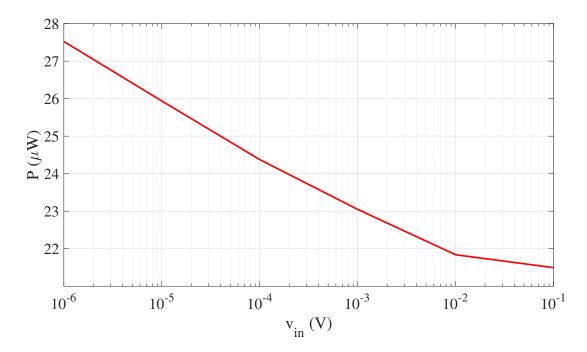

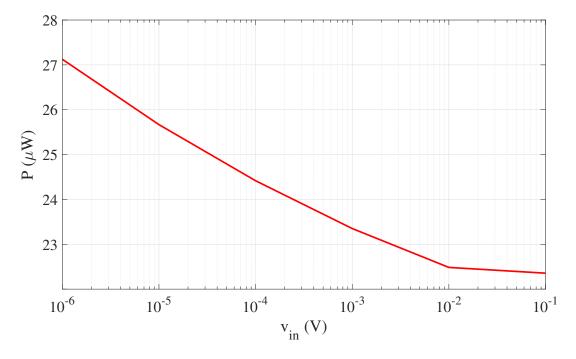

| Figura 22 – Potência Dissipada para Diferentes Valores de $v_{in}$                                   | 47 |

| Figura 23 – PSD do Transistor                                                                        | 48 |

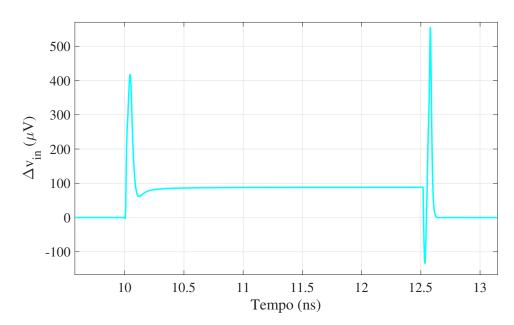

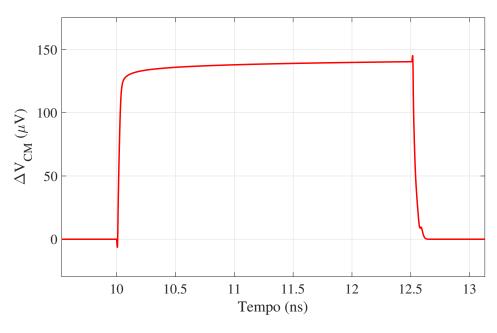

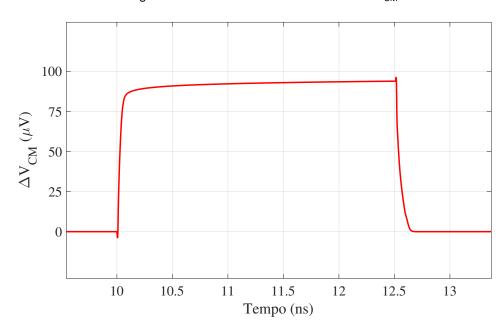

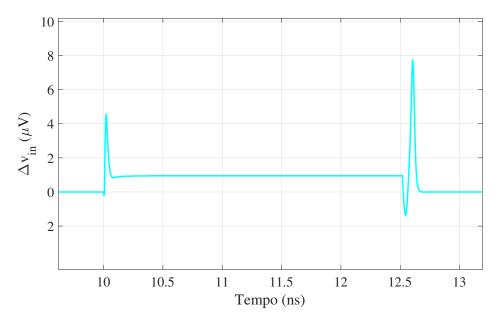

| Figura 24 – Efeito do Kickback Noise Sobre a Tensão dos Capacitores de Entrada                       | 49 |

| Figura 25 – Efeito do Kickback Noise Sobre a Tensão Diferencial de Entrada                           | 50 |

| Figura 26 – Comparador com Calibração                                                                | 51 |

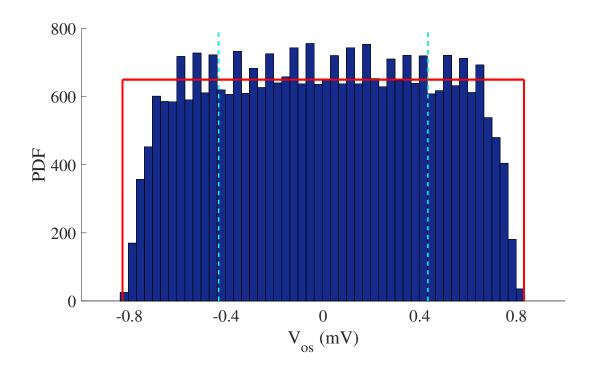

| Figura 27 – Distribuição Normal Pré Calibração e Distribuição Uniforme Pós Calibra-                  |    |

| ção                                                                                                  | 52 |

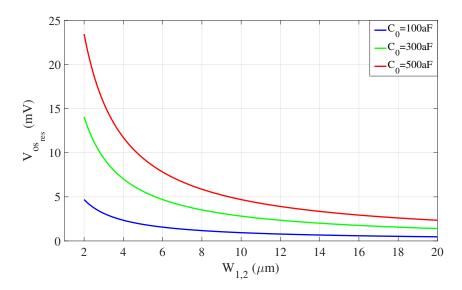

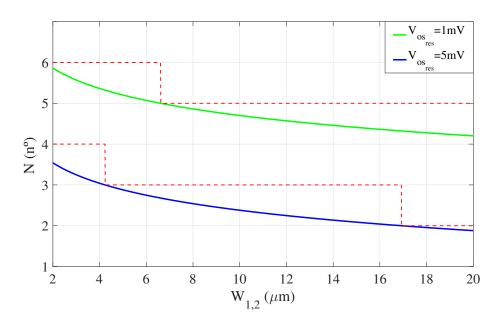

| Figura 28 – Resolução de Calibração $V_{os_{res}}$ em Função de $W_{1,2}$ para Diferentes Valores    |    |

| de $C_0$                                                                                             | 56 |

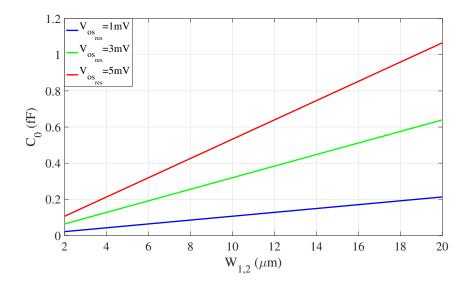

| Figura 29 – Capacitância Unitária Máxima $C_0$ em Função de $W_{1,2}$ para Diferentes Va-            |    |

| lores de $V_{\circ\circ}$                                                                            | 56 |

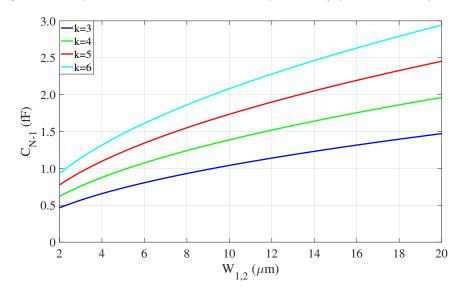

| Figura 30 – Capacitância $C_{N-1}$ Mínima em Função de $W_{1,2}$ para Diferentes $\emph{yeilds}\ k$ .            | 57 |

|------------------------------------------------------------------------------------------------------------------|----|

| Figura 31 — Capacitância ${\cal C}_{N-1}$ Mínima em Função de $W_{1,2}$ para Diferentes Valores de               |    |

| k                                                                                                                | 58 |

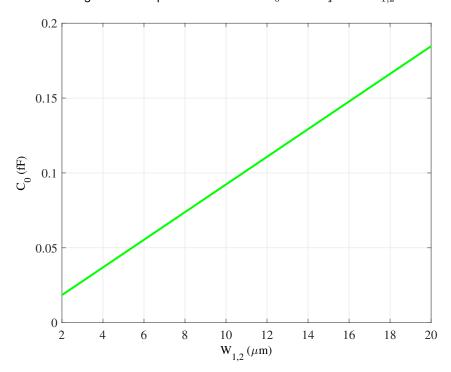

| Figura 32 – Capacitância Máxima $C_0$ em Função de $W_{1,2}$                                                     | 59 |

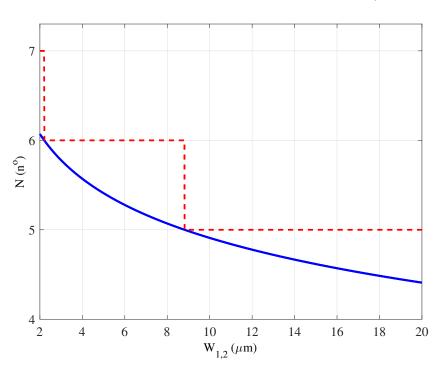

| Figura 33 – Capacitância Mínima $C_{N-1}$ em Função de $W_{1,2}$                                                 | 60 |

| Figura 34 – Número de Capacitores $N$ em Função de $W_{1,2}$                                                     | 60 |

| Figura 35 – PDF do <i>Offset</i> Pré Calibração                                                                  | 61 |

| Figura 36 – PDF do <i>Offset</i> Pós Calibração                                                                  | 62 |

| Figura 37 – Potência Dissipada para Diferentes Valores de $v_{in}$                                               | 63 |

| Figura 38 – Efeito do <i>Kickback Noise</i> Sobre $V_{CM}$                                                       | 64 |

| Figura 39 – Efeito do <i>Kickback Noise</i> Sobre $v_{in}$                                                       | 65 |

| Figura 40 – MOSCap Utilizado como Capacitor                                                                      | 66 |

| Figura 41 – Variação da Capacitância do MOSCap                                                                   | 67 |

| Figura 42 – Variação das Capacitâncias $C^{\mathrm{eff}}$ e $C^{\mathrm{off}}$ do MOSCap em função de $W$ ou $L$ | 68 |

| Figura 43 – Relação entre $\alpha$ e $W_{1,2}$ para $k=4$ e $V_{\mathrm{Os_{res}}}=0.866~mV$                     | 73 |

| Figura 44 – Características do Circuito em Função de $W_{1,2}$ para $k=4$                                        | 74 |

| Figura 45 – PDF do <i>Offset</i> Pré Calibração                                                                  | 75 |

| Figura 46 – PDF do <i>Offset</i> Pós Calibração                                                                  | 76 |

| Figura 47 – Potência Dissipada para Diferentes Valores de $v_{\rm in}$                                           | 77 |

| Figura 48 – Efeito do <i>Kickback Noise</i> Sobre $V_{\text{CM}}$                                                | 78 |

| Figura 49 – Efeito do <i>Kickback Noise</i> Sobre $v_{\text{in}}$                                                | 79 |

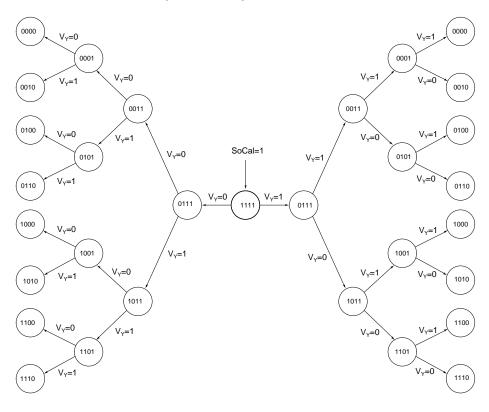

| Figura 50 – Diagrama de Estados                                                                                  | 80 |

| Figura 51 – Máquina de Estados                                                                                   | 81 |

# SUMÁRIO

| 1     | INTRODUÇÃO                                              | 9  |

|-------|---------------------------------------------------------|----|

| 2     | COMPARADOR STRONGARM                                    |    |

| 2.1   | SOBRE O COMPARADOR E PRINCÍPIOS GERAIS DE FUNCIONAMENTO | 11 |

| 2.2   | PRINCÍPIOS ESPECÍFICOS DE FUNCIONAMENTO                 | 13 |

| 2.2.1 | Estágio de Sampling ou Amplificação                     | 13 |

| 2.2.2 | Estágio de Propagação                                   | 15 |

| 2.2.3 | Estágio de Regeneração                                  | 17 |

| 3     | CARACTERÍSTICAS DE OPERAÇÃO                             | 20 |

| 3.1   | POTÊNCIA                                                | 20 |

| 3.2   | VELOCIDADE                                              | 21 |

| 3.3   | META ESTABILIDADE                                       | 22 |

| 3.4   | OFFSET                                                  | 24 |

| 3.5   | RUÍDO                                                   | 29 |

| 3.6   | KICKBACK NOISE                                          | 31 |

| 4     | EXTRAÇÃO DOS PARÂMETROS DA TECNOLOGIA                   | 33 |

| 4.1   | PARÂMETROS DE <i>MISMATCH</i>                           | 33 |

| 4.2   | CAPACITÂNCIAS                                           | 34 |

| 5     | PROJETO DE COMPARADOR SEM CALIBRAÇÃO DE <i>OFFSET</i>   | 37 |

| 5.1   | DEFINIÇÃO DO PAR DIFERENCIAL $M_1-M_2$                  | 37 |

| 5.2   | DEFINIÇÃO DO TRANSISTOR DE CAUDA $M_0$                  | 37 |

| 5.3   | DEFINIÇÃO DO PAR CRUZADO $M_3-M_4$                      | 39 |

| 5.4   | DEFINIÇÃO DO PAR CRUZADO $M_5-M_6$                      | 42 |

| 5.5   | DEFINIÇÃO DOS TRANSISTORES DE PRÉ-CARGA $M_7-M_{10}$    | 44 |

| 5.6   | ANÁLISE DE FUNCIONAMENTO                                | 45 |

|       | Verificação do offset                                   |    |

| 5.6.2 | Verificação de Potência                                 | 46 |

|       | Verificação de Ruído                                    |    |

| 5.6.4 | Verificação de Kickback Noise                           | 47 |

| 5.6.5 | Resumo de Projeto                                       |    |

| 6     | PROJETO DE COMPARADOR COM CALIBRAÇÃO DE <i>OFFSET</i>   |    |

| 6.1   | PRINCÍPIO DE FUNCIONAMENTO                              | 51 |

| 6.2   | TEORIA DA CALIBRAÇÃO                                    |    |

| 6.3   | ANÁLISE DE FUNCIONAMENTO                                | 61 |

|       | Verificação do Offset                                   |    |

| 6.3.2 | Verificação de Potência                                 | 62 |

| 6.3.3 | Verificação de Ruído                                    | 63 |

| 6.3.4 | Verificação de Kickback Noise     | 64        |

|-------|-----------------------------------|-----------|

| 6.3.5 | Resumo de Projeto                 | 64        |

| 6.4   | CALIBRAÇÃO UTILIZANDO MOSCAPS     | 66        |

| 6.4.1 | Projeto dos Capacitores           | 66        |

| 6.4.2 | Equações de Projeto               | 68        |

| 6.4.3 | Projeto do Circuito de Calibração | <b>72</b> |

| 6.5   | ANÁLISE DE FUNCIONAMENTO          | 75        |

| 6.5.1 | Verificação de Offset             | 75        |

| 6.5.2 | Verificação de Potência           | 76        |

| 6.5.3 | Verificação de Ruído              | <b>77</b> |

| 6.5.4 | Verificação de Kickback Noise     | <b>77</b> |

| 6.5.5 | Resumo de Projeto                 | 78        |

| 6.6   | PROJETO DO CIRCUITO DE CONTROLE   | 79        |

| 7     | CONSIDERAÇÕES FINAIS              | 82        |

|       | REFERÊNCIAS BIBLIOGRÁFICAS        | 83        |

### 1 INTRODUÇÃO

Comparadores são circuitos amplamente utilizados em circuitos eletrônicos, cuja função é comparar dois sinais de entrada, que podem ser valores de tensão ou corrente, e retornar como saída um valor que indica qual destes é maior (SANGEETHA et al., 2019). O modo de operação de comparadores pode ser dividido em dois grupos, sendo eles comparadores estáticos e comparadores dinâmicos.

Comparadores estáticos podem ser projetados a partir de um amplificador operacional operando em malha aberta, não tendo sua operação condicionada a algum tipo de sinal habilitador ou de relógio. Como consequência, estes circuitos se caracterizam por estarem sempre consumindo potência, devido ao constante processo de comparação (SAHU; TIWARI, 2018).

Os comparadores dinâmicos, por outro lado, operam em malha fechada, através de uma realimentação positiva na forma de um *latch* regenerativo. O *latch*, provê a regeneração dos sinais devido a existência de polos no semieixo positivo do plano complexo, configurando-o como um sistema instável. Devido a esta característica, as topologias de comparadores dinâmicos necessitam ter sua operação condicionada a algum tipo de sinal habilitador, marcando a início e final da comparação, momento em que deve ser realizado o *reset* do sistema. Em comparação com os comparadores estáticos, os comparadores dinâmicos são mais rápidos e apresentam menor consumo de potência, já que esta só é demandada durante a comparação (SANGEETHA et al., 2019).

Considerando estas diferenças, os comparadores dinâmicos são os escolhidos para integrar circuitos de alta performance. Dada a característica dos comparadores de levar sinais de entrada analógicas para saídas digitais, uma aplicação característica é no projeto de conversores analógicos digitais (ADCs), como o conversor por aproximações sucessivas (SAR) e o conversor *flash* (SONAR; VAITHIYANATHAN; MISHRA, 2020). Uma topologia de comparadores comumente utilizada para este tipos de circuitos é o comparador *StrongARM*, caracterizado por apresentar consumo de potência estática praticamente nula, saída de ponta a ponta e baixo *offset* de entrada (RAZAVI, 2015).

Para a aplicação em ADCs modernos, garantir a velocidade de comparação é importante para maximizar a frequência de conversão dos bits e garantir uma baixa taxa de erros por metaestabilidade. Com relação a precisão do comparador, é necessário garantir que este tenha a capacidade de identificar corretamente a relação entre os sinais de entrada, independente de suas magnitudes, de forma a não gerar erros na palavra binária convertida. Já o consumo de potência deve ser minimizado principalmente devido a demanda por aplicações em dispositivos móveis ou *loT*, que requerem a operação por longos períodos sem recarga de bateria (SONAR; VAITHIYANATHAN; MISHRA, 2020).

Entretanto, estas características de operação são, muitas vezes, antagônicas. Ou

seja, uma mudança de projeto no circuito visando a redução do consumo de potência, pode acarretar em uma redução na precisão de comparação, ou uma alteração nas características de velocidade comparador. Portanto, é necessário entender como cada um destes parâmetros se relacionam para realizar o projeto ótimo do comparador, através das especificações de área dos transistores utilizados, de forma a garantir que ele atenda as especificações da aplicação desejada.

Contudo, as especificações de área dos transistores não são, considerando aplicações de alta performance, normalmente suficientes para atender os critérios estabelecidos para projeto. Dessa forma, além do próprio comparador, é necessário a utilização de circuitos auxiliares que compensem as limitações de performance originais do comparador. Um dos circuitos auxiliares normalmente empregados é o calibrador, ou compensador, de *offset*. Este circuito permite eliminar em grande parte o *offset* de entrada do comparador, melhorando sua precisão, e permitindo que o projeto do comparador priorize outros aspectos, como potência e velocidade, ignorando em grande parte as consequências sobre a precisão original de comparação (XU; ABIDI, 2019).

Deste contexto, este trabalho tem por objetivo demonstrar as interdependências dos parâmetros de operação do comparador *StrongARM* e, a partir destas, propor uma metodologia de projeto que melhor relacione estes parâmetros, de forma a garantir a operação ótima do comparador para a aplicação especificada. Ainda, propõem-se uma metodologia de projeto para um circuito auxiliar de calibração de *offset*, que funciona de forma integrada a metodologia de projeto do próprio comparador, de forma a minimizar os impactos deste circuito sobre o processo de comparação.

#### 2 COMPARADOR STRONGARM

#### 2.1 SOBRE O COMPARADOR E PRINCÍPIOS GERAIS DE FUNCIONAMENTO

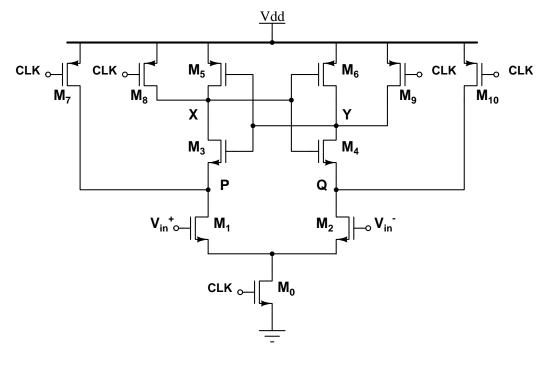

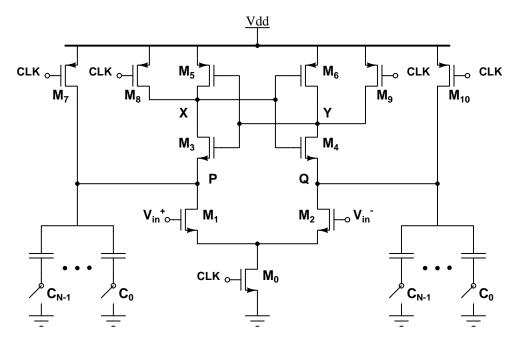

O comparador *StrongARM* é assim conhecido por ter sido implementado pela empresa de mesmo nome, StrongARM microprocessadores, mas teve seu *design* concebido por Toshiba Kobayashi et al. (KOBAYASHI et al., 1992), e seu esquemático é mostrado na Figura 1. Este circuito ganhou popularidade já que apresenta como características o consumo nulo de potência estática, ter saída de ponta a ponta da tensão de alimentação e possuir *offset* de entrada baixo (RAZAVI, 2015).

Figura 1 – Comparador *StrongArm*

Fonte: Adaptado de (RAZAVI, 2015)

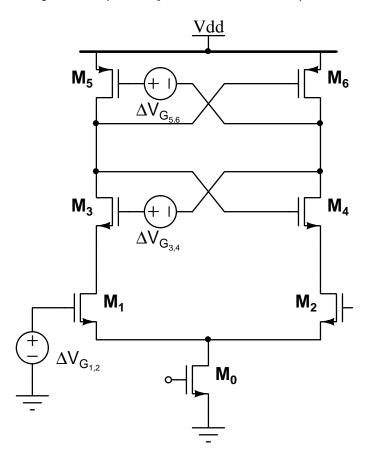

Analisando o esquemático do circuito, pode-se identificar três subcircuitos que integram o comparador. O primeiro, composto pelos transistores NMOS  $M_0$ ,  $M_1$  e  $M_2$ , forma um amplificador diferencial. O segundo é formado pelos transistores  $M_3-M_6$ , que compõe um Latch regenerativo. Por fim, tem-se um circuito de pré-carga, formado pelos transistores PMOS  $M_7-M_{10}$ . De acordo com estes subcircuitos, pode-se explicar o funcionamento do comparador em quatro fases, sendo elas Reset, Sampling ou Amplificação, Propagação e Regeneração (RAZAVI, 2015).

Na primeira fase, denominada de *Reset*, o clock está em nível lógico baixo, e o circuito se encontra em um estado perfeitamente conhecido, em que todas as variáveis

do sistema, definidas como as tensões nas capacitâncias dos drenos de  $M_1-M_4$ , estão carregadas para  $V_{\rm dd}$ , pela ação do circuito de pré carga (ABIDI; XU, 2014). Esta fase existe para eliminar qualquer resquício das comparações anteriores, possibilitando que as únicas fontes de desequilíbrio do sistema venham da tensão diferencial de entrada. Como mencionado anteriormente, o *reset* é feito através do circuito de pré carga, composto pelos transistores  $M_7-M_{10}$ . Como característica de projeto, estes transistores devem ser capazes de conduzir corrente suficiente para levar os nodos do circuito de volta a  $V_{\rm dd}$ , em até meio período de *clock*.

Na mudança de clock para nível lógico alto, os transistores  $M_7-M_{10}$  saem de condução, enquanto que o transistor de cauda  $M_0$  começa a conduzir, formando um caminho entre os nós P e Q e gnd, levando ao surgimento de uma corrente I. Nesta etapa, chamada de amplificação ou sampling, tem-se a geração de um ganho entre o sinal diferencial de entrada e a tensão diferencial entre P e Q, através da integração de uma corrente nas capacitâncias parasitas destes nós (XU; ABIDI, 2019). Esta etapa dura até que os transistores  $M_3$  e  $M_4$  passem a conduzir, ou seja, até a tensão entre porta  $V_{X,Y}$  e fonte  $V_{P,Q}$  dos mesmos seja superior a tensão de limiar  $V_{\text{th}_n}$ . Dado que todos os nodos foram inicializados em  $V_{\text{dd}}$ , é preciso que as tensões em P e Q sejam descarregadas em  $V_{\text{th}_n}$ . O estágio de sampling é importante porque a amplificação do sinal diferencial de entrada reduz o impacto dos demais transistores no offset do circuito.

Com o final do estágio de sampling, inicia-se a terceira etapa, denominada de propagação, caracterizada pela entrada em condução dos transistores  $M_3$  e  $M_4$ . Estes transistores estão conectados de forma cruzada, ou seja, a porta de um, está conectada do dreno do outro, e vice-versa. Esta configuração forma um feedback positivo no circuito, que acaba por potencializar o desbalanço entre os nodos causado pela entrada diferencial de tensão no primeiro estágio, mas sem levar a regeneração completa do sinal. Estes transistores são importantes principalmente pois, ao final da comparação, eles são capazes de interromper a circulação de corrente no circuito, auxiliados pelos transistores  $M_5$  e  $M_6$ , garantindo que o circuito não consuma potência estática (RAZAVI, 2015). Assim como na etapa anterior, a propagação se dá por finalizada quando os transistores  $M_5$  e  $M_6$  passam a conduzir, devido a um descarregamento de  $|V_{th_0}|$  nos nodos X e Y.

Finalizada a etapa de propagação, os transistores  $M_5$  e  $M_6$  entram em condução, dando início a etapa final do circuito, chamada de regeneração. Assim como na propagação, o *feedback* positivo do circuito aumenta o desbalanço de tensão entre os nós, porém desta vez levando a regeneração completa. Dessa forma, ao final desta etapa, o circuito levará os desbalanços criados anteriormente para  $V_{\rm dd}$  e gnd, tornando os nodos X e Y em saídas digitais (ABIDI; XU, 2014). Entretanto, não é necessário levar as saídas X e Y até estes valores para que a comparação seja considerada válida, é suficiente que a diferença  $V_{XY}$  entre estes nodos seja de  $V_{\rm dd}/2$ . Caso esta condição não seja atendida até a descida do *clock*, diz-se que o circuito se encontra em uma situação de metaestabilidade, e a inde-

finição na saída do comparador pode se propagar para os circuitos seguintes, acarretando em problemas de funcionamento (RAZAVI, 2020).

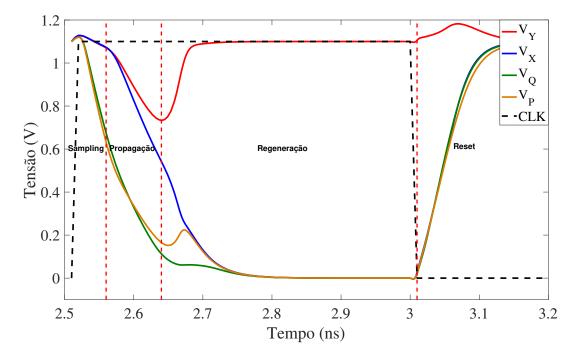

Por fim, na borda de descida do *clock*, o transistor  $M_0$  sai de condução, enquanto os transistores  $M_7-M_{10}$  são polarizados, retornando para a primeira etapa, resetando os nodos do comparador novamente para  $V_{\rm dd}$ . O comportamento gráfico característico das tensões nos nodos do circuito em um ciclo de operação é mostrado na Figura 2 (WHITEHEAD, 2019).

Figura 2 - Ciclo de Operação Característico

Fonte: Adaptado de (WHITEHEAD, 2019)

#### 2.2 PRINCÍPIOS ESPECÍFICOS DE FUNCIONAMENTO

#### 2.2.1 Estágio de Sampling ou Amplificação

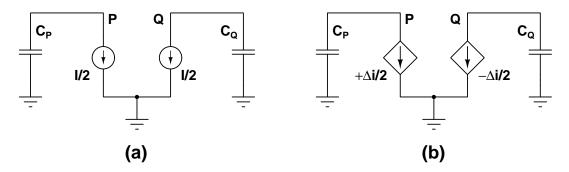

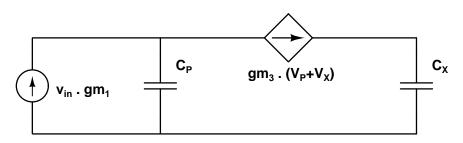

Como dito anteriormente, este estágio é caracterizado pelo ganho proporcionado entre  $v_{\rm in}$  e  $V_{PQ}$ . Podemos identificar o comportamento do ganho do circuito nesta etapa através de uma análise do circuito equivalente mostrado na Figura 3, onde  $C_P=C_Q$  se refere a capacitância equivalente vistas nos drenos de  $M_1$  e  $M_2$ , I é a corrente de modo comum, e  $\Delta i$  é a corrente diferencial induzida no circuito (WHITEHEAD, 2019).

Vemos que, no circuito equivalente de modo comum, ambos os capacitores se descarregam na mesma velocidade, já que as capacitâncias e correntes são iguais. Dessa

Figura 3 - Circuito Equivalente de Modo Comum (a) e Pequenos Sinais (b) Durante o Sampling

Fonte: Adaptado de (XU; ABIDI, 2019)

forma, temos que a diferença de tensão entre os nodos acaba por ser nula. Contudo, no equivalente de pequenos sinais, percebe-se que a entrada diferencial resulta no aparecimento de uma corrente diferencial, que desbalança o circuito (ABIDI; XU, 2014). Com isso, tem-se que a tensão entre os nós P e Q é dada por

$$V_{PQ} = \frac{1}{C_{PQ}} \int_0^t \frac{\Delta i}{2} dt - \frac{1}{C_{PQ}} \int_0^t -\frac{\Delta i}{2} dt = \frac{1}{C_{PQ}} \int_0^t \Delta i dt , \qquad (2.1)$$

resultando em

$$V_{PQ} = \frac{\Delta i \cdot t}{C_{P,Q}} \,, \tag{2.2}$$

para uma corrente diferencial  $\Delta i$  constante.

Sabendo ainda que  $\Delta i = g_{m_{1,2}}v_{\text{in}}$  (LI; XU; LIZUKA, 2022), temos que o ganho dinâmico em função do tempo de operação do circuito é obtido através de

$$\frac{V_{PQ}(t)}{v_{\text{in}}} = \frac{g_{m_{1,2}} \cdot t}{C_{P,Q}}.$$

(2.3)

Entretanto, só estamos interessados no ganho ao final da etapa de *Sampling*, ou seja, no instante em que os transistores  $M_3$  e  $M_4$  passam a conduzir, definido como  $t=t_{\rm smp}$ . Da seção anterior, sabemos que a isso ocorre quando a tensão de modo comum nos nós P e Q é igual a  $V_{P,Q}=V_{\rm dd}-V_{\rm th_n}$ .

Para verificar esta situação, volta-se ao circuito equivalente de modo comum apresentado na Figura 3 e resolve-se a equação da tensão nos capacitores para  $t=t_{\rm smp}$ , resultando em

$$V_{P,Q}(t_{\rm smp}) = V_{\rm dd} - V_{\rm th_n} = V_{\rm dd} - \frac{1}{C_{P,Q}} \int_0^{t_{\rm smp}} \frac{I}{2} dt$$

(2.4)

Isolando  $t_{smp}$  em (2.4), encontra-se

$$t_{\mathsf{smp}} = \frac{C_{P,Q} \cdot V_{\mathsf{th}_{\mathsf{n}}}}{I/2}.\tag{2.5}$$

Conhecida a duração do estágio, pode-se substituir o resultado da expressão (2.5) em (2.3), obtendo-se o ganho efetivo do estágio de *sampling* (RAZAVI, 2015), dado por

$$A_{v_{\mathsf{smp}}} = \frac{g_{m_{1,2}} \cdot V_{\mathsf{th}_{\mathsf{n}}}}{I/2} = \frac{g_{m_{1,2}}}{I_{d_{1,2}}} \cdot V_{th_n} \ . \tag{2.6}$$

#### 2.2.2 Estágio de Propagação

Com a entrada em condução do par cruzado formado por  $M_3$  e  $M_4$ , tem-se o início do estágio de propagação. Para entender o comportamento deste estágio, pode-se analisar o circuito equivalente mostrado na Figura 4.

Figura 4 – Circuito Equivalente de Modo Comum Durante a Propagação

Fonte: Adaptado de (RAZAVI, 2015)

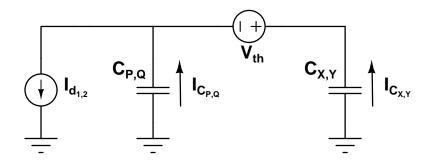

Em um primeiro momento, tomando o comportamento de modo comum do circuito, repete-se a análise feita para o estágio de sampling para determinar a duração da propagação. Em modo comum, pode-se considerar que as portas dos transistores  $M_{3,4}$  estão conectadas aos drenos, como se fossem conectados a diodo (XU; ABIDI, 2019). Dessa forma, a diferença de tensão entre  $C_{X,Y}$  e  $C_{P,Q}$  é a queda tensão entre os terminais do 'diodo', equivalente a  $V_{\rm th}$ . O circuito equivalente do sistema resultante é mostrado na Figura 5. Deste resultado, diz-se que a corrente de modo comum resultante é a soma das contribuições de correntes de cada nó, dado por

$$\frac{I}{2} = I_{\mathsf{d}_{1,2}} = I_{C_{P,Q}} + I_{C_{X,Y}} , \qquad (2.7)$$

Figura 5 – Meio Circuito Equivalente de Modo Comum Durante a Propagação

Fonte: Autor (2023)

em que estas componentes são proporcionais as capacitâncias equivalentes nos nós, ou seja

$$I_{C_{P,Q}} = \frac{I_{\mathsf{d}_{1,2}} \cdot C_{P,Q}}{C_{P,Q} + C_{X,Y}}, \qquad I_{C_{X,Y}} = \frac{I_{\mathsf{d}_{1,2}} \cdot C_{X,Y}}{C_{P,Q} + C_{X,Y}}. \tag{2.8}$$

Ou seja, a diferença de tensão entre as capacitâncias permanece igual a  $V_{\rm th}$  durante a propagação, fazendo com que a tensão sobre as capacitâncias caiam juntas no decorrer do estágio. Dessa forma, pode-se equacionar a a tensão  $V_{X,Y}$  considerando que a corrente de modo comum descarrega uma capacitância equivalente a soma de  $C_{P,Q}$  e  $C_{X,Y}$ , de acordo com

$$V_{X,Y} = V_{dd} - \frac{1}{C_{X,Y} + C_{P,Q}} \int_0^t \frac{I}{2} dt .$$

(2.9)

Mais uma vez, temos que o estágio se dá por finalizado quando os transistores  $M_5$  e  $M_6$  entram em condução, ou seja, quando  $V_{X,Y} = V_{\rm dd} - |V_{\rm th_p}|$ , tem-se que  $t = t_{\rm prop}$  (XU; ABIDI, 2019). Substituindo esta situação em (2.9), resulta em

$$V_{X,Y} = V_{dd} - |V_{th_p}| = V_{dd} - \frac{1}{C_{XY} + C_{PQ}} \int_0^{t_{prop}} \frac{I}{2} dt$$

, (2.10)

e isolando  $t_{prop}$ , obtêm-se o tempo de propagação como

$$t_{\text{prop}} = \frac{(C_{X,Y} + C_{P,Q})|V_{\text{th}_p}|}{I/2}$$

(2.11)

Devido a ligação cruzada entre os transistores, não é imediatamente óbvio o equivalente de pequenos sinais de modo diferencial desta etapa. Entretanto, sabendo que os transistores podem ser modelados como fontes de corrente de valor  $i_{M_i}=g_{m_i}(V_{\rm G}-V_{\rm S})$  e que, por simetria, a tensão diferencial em X deve ser igual em módulo, porém com sentido contrário a de Y, temos que:

$$i_{M_3} = g_{m_3}(V_Y - V_P) = g_{m_3}(-V_X - V_P) = -g_{m_3}(V_X + V_P)$$

(2.12)

Dessa forma, verifica-se que os transistores  $M_3$  e  $M_4$  são modelados como fontes

de corrente dependentes da soma das tensões na capacitâncias equivalentes no dreno e fonte. Sabendo disso, tem-se o modelo de pequenos sinais desta etapa mostrado na Figura 6 (ABIDI; XU, 2014).

Figura 6 - Circuito Isolado Durante a Propagação

Fonte: Adaptado de (XU; ABIDI, 2019)

Deste modelo, pode-se estabelecer duas situações de operação, relacionadas a qual das capacitâncias equivalentes é maior. Se  $C_P > C_X$ , tem-se que o polo deste circuito é positivo, levando a regeneração. Caso contrário, o circuito se comporta como um amplificador estável, introduzindo um *feedback* positivo limitado, impedindo a regeneração completa (XU; ABIDI, 2019).

Assumindo que o par  $M_1$  e  $M_2$  se mantém em saturação durante este estágio, o que normalmente acontece, pode-se afirmar que a principal contribuição para a redistribuição de carga entre os capacitores e para a tensão final sobre  $C_X$  se dá pela corrente vinda deste par. Dessa forma, segundo (ABIDI; XU, 2014), diz-se que o ganho neste estágio dado por

$$A_{v_{\text{prop}}} = \left(\frac{C_X + 2C_P}{C_X - C_P}\right) \cdot \left(\frac{|V_{\text{th}_p}|g_{m_1}}{I/2}\right), \quad C_{X,Y} > C_{P,Q}$$

(2.13)

#### 2.2.3 Estágio de Regeneração

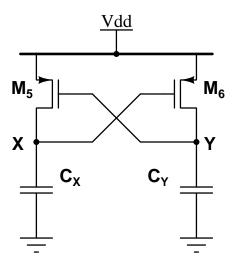

Com o término da etapa de propagação, inicia-se o processo de regeneração do circuito, através da entrada em condução do par cruzado  $M_5$  e  $M_6$ . Para compreender o processo de regeneração, toma-se como base o circuito isolado mostrado na Figura 7 (RAZAVI, 2020).

Primeiro, assumindo que a condição inicial de tensão dos capacitores é igual a  $V_{\rm dd}-|V_{\rm th_p}|$ , aplicamos sobre  $C_X$  uma variação de tensão igual a  $-\Delta V_X$ . Isso leva a um aumento na tensão entre porta e fonte do transistor  $M_6$ , levando a um aumento de  $\Delta I_Y$  na corrente sobre o capacitor  $C_Y$ , que por sua vez o carrega em  $\Delta V_Y$ . Entretanto, esta variação de tensão também aparece na porta de  $M_5$ , alterando a diferença de potencial com relação a fonte neste mesmo valor, modificando a corrente resultante em  $-\Delta I_X$ , o que, por fim, descarrega ainda mais o capacitor  $C_X$ . Com isso, percebe-se que uma variação na

tensão sobre o nodo é sempre intensificada pelo circuito, confirmando a operação como um sistema regenerativo.

Figura 7 – Circuito Isolado da Etapa de Regeneração

Fonte: Adaptado de (RAZAVI, 2020)

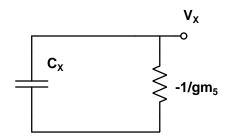

Pode-se ainda utilizar esta análise para determinar a impedância equivalente deste circuito, e por consequência, como estes transistores são modelados no equivalente de pequenos sinais. Já foi estabelecido que aplicar  $-\Delta V_X$  resulta no aparecimento de uma corrente  $-\Delta I_X$ . Entretanto, sabemos que  $\Delta I_X = -g_m \Delta V_X$ , e portanto tem-se que  $\Delta V_X/\Delta I_X = -\frac{1}{g_m}$ . Ou seja, os transistores  $M_5$  e  $M_6$  atuam como resistências negativas no modelo de pequenos sinais, resultando no circuito equivalente da Figura 8. Segundo (RAZAVI, 2020), a resposta deste circuito possui característica análoga a da carga/descarga de um capacitor, dada por:  $v_{XY}(t) = v_{XY_0} \cdot e^{-\frac{t}{\tau_{\rm reg}}}$ .

Figura 8 - Meio Circuito Equivalente de Pequenos Sinais Durante a Regeneração

Fonte: Adaptado de (XU; ABIDI, 2019)

Em que a tensão inicial  $v_{XY_0}$  é dada como a tensão diferencial no limiar da regeneração, ou seja, em  $t_{\rm smp}+t_{\rm prop}$ , valor que corresponde ao produto entre o ganho acumulado do circuito neste instante, dado por

$$A_v = A_{v_{\text{prop}}} \cdot A_{v_{\text{smp}}} , \qquad (2.14)$$

e a tensão diferencial de entrada  $v_{\rm in}$ , resultando em

$$v_{XY_0} = A_v v_{\text{in}}$$

(2.15)

A constante de tempo  $\tau_{\rm reg}$  nesse estágio é definida como o produto da impedância  $-\frac{1}{g_{m_5}}$  e a capacitância equivalente  $C_X$  no nó (ABIDI; XU, 2014). Nota-se que por ser um valor negativo,  $e^{-\frac{t}{\tau_{\rm reg}}}$  possui expoente positivo, e portanto a tensão cresce exponencialmente com o tempo, até os limites de  $V_{\rm dd}$  ou gnd. Dessa forma, defini-se a tensão diferencial na saída do comparador como:

$$v_{XY}(t) = A_v v_{\mathsf{in}} \cdot e^{\frac{t}{\tau_{\mathsf{reg}}}} = A_v v_{\mathsf{in}} \cdot e^{t\frac{g_{m_{5,6}}}{C_{XY}}}. \tag{2.16}$$

Assim como nos estágios anteriores, é de interesse determinar a duração da etapa de regeneração, a fim de estabelecer a duração total da comparação. O critério para dar a etapa como finalizada é que a tensão diferencial na saída seja igual a  $V_{\rm dd}/2$ , momento em que já é possível assumir as saídas como valores digitais (WHITEHEAD, 2019). Resolvendo (2.16) para esta condição, encontra-se que a duração do estágio de regeneração é:

$$t_{\text{reg}} = \tau_{\text{reg}} \cdot \ln \left( \frac{V_{\text{dd}}/2}{A_v v_{\text{in}}} \right) = \frac{C_{X,Y}}{g_{m_{5,6}}} \cdot \ln \left( \frac{V_{\text{dd}}/2}{A_v v_{\text{in}}} \right) \ . \tag{2.17}$$

Ainda, pela condição de metaestabilidade mencionada anteriormente, é preciso respeitar a seguinte desigualdade

$$t_{\rm smp} + t_{\rm prop} + t_{\rm reg} < \frac{D}{f_{\rm CLK}}$$

(2.18)

em que D representa o *duty cicle* do *clock*. Para o caso específico de um *clock* simétrico, têm-se

$$t_{\rm smp} + t_{\rm prop} + t_{\rm reg} < \frac{1}{2f_{\rm CLK}} \,. \tag{2.19}$$

### 3 CARACTERÍSTICAS DE OPERAÇÃO

Para o projeto de um comparador, podem ser definidos diversos critérios e características de projeto, como a frequência, ganho, *offset*, etc. Essas definições, entretanto, não podem ser feitas de forma isolada, já que uma escolha direcionada a definição da velocidade de comparação, pode afetar, por exemplo, a rejeição de *offset* do circuito. Dessa forma, é preciso compreender como cada parâmetro influencia em outro, para o correto projeto do circuito.

#### 3.1 POTÊNCIA

A potência consumida pelo circuito está associada ao carregamento das capacitâncias parasitas nos nós do circuito em um período de comparação. Sabe-se, das seções anteriores, que durante um ciclo de comparação as capacitâncias parasitas dos nodos P e Q são levadas de  $V_{\rm dd}$  até gnd, enquanto que somente uma das capacitâncias nos nós X e Y são descarregadas desta maneira (RAZAVI, 2015). Desta forma, durante a fase de P0 circuito carrega estas três capacitâncias. Dada uma tensão de alimentação P0 uma frequência de operação P1 tem-se que a potência dissipada pelo circuito é dada por

$$P_{diss} = f_{CLK} \cdot (C_P + C_Q + C_{X,Y}) V_{dd}^2 . {(3.1)}$$

Desta equação, percebe-se que a potência é dependente de três fatores, sendo eles a frequência de operação, a tensão de alimentação e a capacitância equivalente. Dessa forma, é possível alterar tais parâmetros de forma limitar a potência dissipada no circuito em um determinado valor. Dentre as opções, a mais impactante é a tensão de alimentação do circuito, já que ela aparece como uma potência de dois. Para reduzir esta tensão, é necessário utilizar tecnologias mais modernas de transistores, com menores comprimentos de canal. Nota-se, entretanto, que uma possível redução em  $V_{\rm dd}$  também limita a tensão de modo comum  $V_{\rm CM}$ , geralmente de valor igual a metade de  $V_{\rm dd}$ , utilizada para polarizar os transistores do par diferencial. Uma redução em  $V_{\rm CM}$  acarreta em uma redução da corrente de modo comum do circuito, já que esta variação aparece diretamente na tensão  $V_{GS}$  dos transistores  $M_{1,2}$  responsáveis por definir esta corrente. Com consequência, o par diferencial é empurrado para a inversão fraca, o que impacta tanto na velocidade quanto no ganho do circuito, que serão discutidos posteriormente. Ainda, com a redução de  $V_{\rm dd}$ , ocorre também uma diminuição nas tensões entre dreno e fonte dos transistores, e, dado que o ganho do circuito se dá enquanto estes estão em saturação, é possível que estes entrem na região de triodo antes que o circuito tenha integrado ganho suficiente. Acima de tudo, como mencionado,  $V_{\rm dd}$  máximo é um parâmetro de tecnologia, e seu valor é uma especificação do projeto.

Em relação as capacitâncias, simplificadamente, sabe-se que elas são funções diretas do comprimento de canal L e largura de canal W (CAKA et al., 2007). Se tratando do comprimento de canal L, sabe-se que o aumento deste parâmetro causa a redução da corrente no circuito na mesma proporção, aumentando o tempo de duração de cada estágio tanto pelo lado da capacitância quanto da corrente, e levando a um aumento no ganho do circuito. Entretanto, o impacto sobre a velocidade é mais significativo, e portanto prefere-se mantê-lo como o mínimo permitido pela tecnologia, ou levemente acima, caso deseje-se evitar efeitos de canal curto. A largura de canal W, por outro lado, pode ser modificada de acordo com a necessidade de operação do circuito, já que o aumento da capacitância acompanha o aumento na corrente dos transistores. Nota-se que este é o parâmetro mais importante para o projeto com transistores, influenciando não só na potência, mas como em todas o demais critérios de projeto, que serão explicados posteriormente.

Por fim, tem-se a frequência de comparação  $f_{\rm CLK}$ , que impacta linearmente a potência dissipada. A consequência de se modificar este parâmetro é fácil de ser constatada, sendo ela a mudança do número de comparações realizadas em determinado período. Dessa forma, ela não é uma alternativa válida para o controle da potência do circuito. Em suma, verifica-se que a única solução plausível para a limitação da potência dissipada pelo circuito em uma determinada tecnologia, é tornar a largura de canal W dos componentes menor possível, caso  $V_{\rm dd}$  seja determinado por requisitos do sistema, de forma a minimizar as capacitâncias do comparador.

#### 3.2 VELOCIDADE

O tempo total de comparação é definido como a soma do tempo de duração dos estágios de *sampling*, propagação e regeneração, expresso por

$$t_{\text{comp}} = t_{\text{smp}} + t_{\text{prop}} + t_{\text{req}} . \tag{3.2}$$

Das equações (2.5) e (2.11), sabemos que os tempos de *sampling* e propagação sofrem influencia direta da capacitância equivalente nos respectivos nós, e são inversamente impactadas pela corrente de modo comum do circuito. Com relação as capacitâncias parasitas, tem-se que elas possuem parcelas referentes a todos os transistores conectados ao nó em questão, ou seja, um aumento de duas vezes em  $W_{1,2}$  não resulta em um aumento de duas vezes em  $C_{P,Q}$ , mas sim na contribuição de  $W_{1,2}$  para esta capacitância. Dessa forma, os impactos dos pares de transistores são condicionalmente diferentes entre si, de acordo com qual transistor domina a capacitância total do nó. Ainda, tem-se que somente

o par de transistores  $M_{3,4}$  contribui tanto para  $C_{P,Q}$  quanto para  $C_{X,Y}$ , fazendo com que a minimização de  $W_{3,4}$  seja prioritária para o aumento da velocidade de comparação.

Observando pelo lado da corrente de modo comum, sabe-se que ela é definida principalmente pelos transistores do para diferencial  $M_1$  e  $M_2$ . Desta forma, aumentar estes componentes tende a reduzir a duração da comparação. Entretanto, como mencionado anteriormente, a contribuição do par para a capacitância aumentará na mesma proporção, fazendo com que não se possa aumentar a largura de canal indefinidamente, mas somente até que o impacto da capacitância do par diferencial comece a ser dominante nos nodos do circuito. Chegado este ponto, não fará sentido continuar a aumentar este parâmetro, sem antes modificar o par  $M_3$  e  $M_4$ . Ainda, é possível influenciar a corrente de modo comum através do transistor de cauda  $M_0$ . Este transistor é caracterizado por operar na região de triodo profundo, e portanto apresenta comportamento de uma resistência variável em função de W. Dessa forma, quanto maior a largura de canal, menor a resistência, e por consequência menor é a tensão  $V_{\rm DS}$  sobre o componente. Considerando que esta é a tensão  $V_{\rm S}$  de  $M_{1,2}$ , tem-se também um aumento em  $V_{\rm GS}$  para estes transistores, o que aumenta a corrente de modo comum do circuito, reduzindo a duração dos estágios de sampling e propagação.

Com relação ao tempo de regeneração, a equação (2.17) indica três maneiras de reduzir este valor, sendo elas a constante de tempo  $\tau_{\rm reg}$ , o ganho acumulado ao fim da propagação  $A_v$  e a tensão diferencial de entrada  $v_{\rm in}$ . A tensão  $v_{\rm in}$  é um parâmetro de entrada, e portanto não pode-se utiliza-lo para modificar  $t_{\rm reg}$ , sendo apenas considerado para determinar um tempo máximo do estágio. O ganho na propagação é impactado pela corrente de modo comum e pelas capacitâncias do circuito, seguindo a explicação anterior. Porém, a maior parcela deste ganho é referente a etapa de sampling, dada pela equação (2.6), e portanto reduzir a corrente de modo comum é a melhor maneira de impactar o ganho do circuito, apesar de que isso aumentaria a duração das etapas anteriores, e dessa forma pode-se dizer que o o ganho do circuito e a velocidade de comparação são, no geral, inversamente proporcionais. A constante de tempo, assim como nos casos anteriores, é dependente da capacitância no nodo, e portanto segue as análises anteriores. Nota-se, entretanto, que esta seria a maneira mais efetiva de reduzir o tempo de regeneração, já que a constante de tempo impacta  $t_{\rm reg}$  de forma linear, enquanto que os demais o fazem de forma logarítmica.

#### 3.3 META ESTABILIDADE

A condição de meta estabilidade está associada a incapacidade do comparador de regenerar os sinais de saída a tempo do final do período de comparação, dado pela descida do *clock*. Caso a regeneração não ocorra a tempo, a indefinição destes sinais pode

acarretar na propagação de erros para circuitos que dependem das saídas do comparador. Pela equação (2.19), sabe-se que para evitar a condição de metaestabilidade o tempo total de comparação deve ser inferior a meio período de *clock*. Ainda, pelas equações (2.5), (2.11) e (2.17), sabe-se que  $t_{\rm smp}$  e  $t_{\rm prop}$  são fixos, enquanto que  $t_{\rm reg}$  é dependente da tensão de entrada  $v_{\rm in}$ . Dessa forma, pode-se expressar uma relação entre frequência de *clock* e tensão de entrada de forma a determinar as condições de metaestabilidade do comparador.

A partir a equação (2.17), pode-se determinar o efeito que reduzir  $v_{in}$  por um determinado fator k tem sobre  $t_{reg}$  (RAZAVI, 2020), obtendo

$$t_{\mathsf{reg}} + \Delta t_{\mathsf{reg}} = au_{\mathsf{reg}} \cdot \mathsf{ln}\left(rac{V_{\mathsf{dd}}/2}{A_v \cdot v_{\mathsf{ino}}/k}

ight) \ .$$

(3.3)

Isolando  $\Delta t_{\rm reg}$ , têm-se que

$$\Delta t_{\text{reg}} = \tau_{\text{reg}} \cdot \ln(k) \ . \tag{3.4}$$

A partir deste resultado, e conhecido o tempo de comparação para uma determinada tensão de entrada  $v_{\rm in_0}$ , pode-se reescrever a desigualdade da expressão (2.19) como

$$t_{\text{comp}}(v_{\text{in}_0}) + \tau_{\text{reg}} \cdot \ln(k) < \frac{1}{2f_{\text{CLK}}} , \qquad (3.5)$$

em que  $k=\frac{v_{\rm in_0}}{v_{\rm in}}$ . A partir desta relação, pode-se determinar a frequência máxima de *clock* para a menor tensão  $v_{\rm in_{min}}$  que deseja-se comparar sem erros de metaestabilidade.

Assumindo, por exemplo, que o tempo de comparação para  $v_{\rm in_0}=10mV$  seja  $t_{\rm comp}=150ps$  e que a constante de tempo projetada seja  $\tau_{\rm reg}=20ps$ , segue que

$$150ps + 20ps \cdot \ln\left(\frac{10mV}{v_{\text{inmin}}}\right) < \frac{1}{2f_{\text{GLK}}}. \tag{3.6}$$

Considerando que a menor tensão que deseja-se regenerar sem erros de metaestabilidade seja  $v_{\rm in_{min}}=1\mu V$ , substitui-se este valor em (3.6) e determina-se a maior frequência de clock como  $f_{\rm CLK}=1.5GHz$ . Alternativamente, considerando que a especificação de projeto dada é  $f_{\rm CLK}$ , pode-se determinar a mínima tensão de entrada que não provoca erros de metaestabilidade ao isolar  $v_{\rm in}$  em (3.5), chegando em

$$\ln(v_{\mathsf{in}_{\mathsf{min}}}) > \frac{t_{\mathsf{comp}}(v_{\mathsf{in}_0}) + \tau_{\mathsf{reg}} \cdot \ln(v_{\mathsf{in}_0}) - \frac{1}{2f_{\mathsf{CLK}}}}{\tau_{\mathsf{reg}}} \;, \tag{3.7}$$

que para os mesmos parâmetros do exemplo anterior e para  $f_{\rm CLK}=2GHz$  resulta em  $v_{\rm in_{min}}\gtrsim 67\mu V$ .

Sabendo que os possíveis valores na entrada do comparador formam uma distribuição uniforme entre  $+V_{\rm dd}$  e  $-V_{\rm dd}$ , pode-se determinar a taxa de erros por metaestabilidade

através da probabilidade de a entrada do comparador estar entre  $+v_{\rm in_{min}}$  e  $-v_{\rm in_{min}}$ , dada de acordo com a função de probabilidade para uma distribuição uniforme

$$P(v_{\text{in}_{\min}}) = \frac{(+v_{\text{in}_{\min}}) - (-v_{\text{in}_{\min}})}{(+V_{\text{dd}}) - (-V_{\text{dd}})} = \frac{v_{\text{in}_{\min}}}{V_{\text{dd}}}.$$

(3.8)

Considerando a operação em uma dada frequência, defini-se a taxa de erros por metaestabilidade como

$$\epsilon_{\mathsf{M}} = P(v_{\mathsf{in}_{\mathsf{min}}}) \cdot f_{\mathsf{CLK}} \,.$$

(3.9)

Substituindo na expressão (3.9) o exemplo em que  $f_{\rm CLK}=2GHz$  e  $v_{\rm in_{min}}=67\mu V$ , e utilizando  $V_{\rm dd}=1.1V$ , encontra-se que a taxa de erro é  $\epsilon_{\rm M}\approx 120\cdot 10^3/s$ . Considerando que este resultado é aquém do esperado, pode-se redefinir o valor de  $f_{\rm CLK}$  utilizado a partir da definição da taxa de erros desejada. Substituindo (3.7) em (3.9) e rearranjando a equação, obtêm-se

$$\ln(f_{\text{CLK}}) - \frac{1}{2\tau_{\text{reg}}f_{\text{CLK}}} = \ln(\epsilon_M \cdot V_{\text{dd}}) - \frac{t_{\text{comp}}(v_{\text{in}_0}) + \tau_{\text{reg}} \cdot \ln(v_{\text{in}_0})}{\tau_{\text{reg}}} \,. \tag{3.10}$$

Assumindo que é necessário garantir uma taxa de erros máxima de  $\epsilon_M = 3.3 \times 10^{-9}/s$ , equivalente a um erro a cada dez anos, e considerando os mesmos parâmetros dos demais exemplos, encontra-se a partir de (3.10) que  $f_{\text{CLK}} \lesssim 590 \ MHz$ .

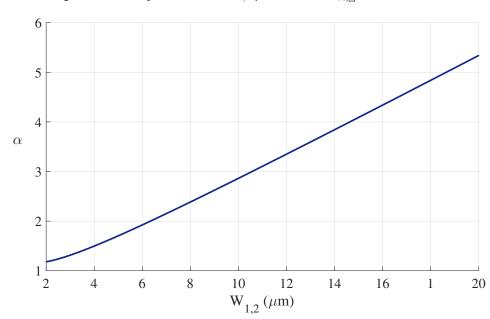

Durante o projeto do comparador, a minimização dos erros por metaestabilidade está ligada principalmente a definição do parâmetro  $\tau_{\rm reg}$ , já que ele define a proporção do aumento do tempo de regeneração, como mostrado pela equação (3.4). A equação (2.17) mostra que  $\tau_{\rm reg}$  aumenta com  $C_{X,Y}$  e reduz com  $g_{m_{5,6}}$ , na mesma proporção. A capacitância  $C_{X,Y}$  pode ser reduzida pela diminuição de  $W_{3,4}$  e  $W_{5,6}$ . Contudo, reduzir  $W_{5,6}$  também causa uma diminuição em  $g_{m_{5,6}}$  por um fator igual a raiz desta mudança. Dessa forma, para impactar  $\tau_{\rm reg}$  através de  $W_{5,6}$  é preciso que  $M_{5,6}$  não dominem a capacitância do nó (RAZAVI, 2020).

#### 3.4 OFFSET

Como discutido anteriormente, o comparador define uma saída binária de acordo com a comparação das magnitudes do sinal de entrada. Em um circuito ideal, o comparador seria capaz de identificar corretamente uma diferença infinitesimal entre estes sinais, entretanto, um circuito real apresenta não idealidades que podem afetar sua operação. Estas não idealidades são originadas de variabilidades do processo de fabricação, e podem ser classificadas entre globais ou locais.

Variações globais afetam igualmente todos os componentes de um determinado

chip, resultando em uma variação de performance em relação a média dos chips fabricados. As variações locais afetam individualmente os componentes do circuito, alterando as características entre cada transistor do chip fabricado, causando um descasamento, ou mismatch, entre estes dispositivos (BOSCH; STEYAERT; SANSEN, 2004). Para o comparador, o mismatch se mostra especialmente prejudicial, já que a simetria dos pares de transistores é fundamental para o correto funcionamento do circuito. Dessa forma, é preciso considerar os efeitos do mismatch entre os componentes durante o projeto do comparador, limitando sua influência sobre o resultado a comparação.

Pode-se descrever o efeito do *mismatch* entre dois transistores analisando um par diferencial operando com uma mesma tensão  $V_{\rm GS}$ . Sabe-se que a corrente que circula em cada transistor do par, assumindo operação em saturação, é expressa por

$$I_d = \frac{\beta}{2} (V_{\text{GS}} - V_{\text{th}})^2$$

(3.11)

Considerando uma variação sobre os parâmetros dos transistores decorrente do *mismatch*, pode-se determinar qual a variação  $\Delta I_d$  resultante de pequenas variações nos parâmetros  $V_{\text{th}}$  e  $\beta$  no circuito tomando a função diferencial total de (3.11) (ZIRGER, 2007), dada por

$$\Delta I_d = \frac{\partial I_d}{\partial \beta} \Delta \beta + \frac{\partial I_d}{\partial V_{GS}} \Delta V_{GS} + \frac{\partial I_d}{\partial V_{th}} \Delta V_{th} . \tag{3.12}$$

Dado que a tensão  $V_{\rm GS}$  é igual para ambos os transistores, tem-se que  $\Delta V_{\rm GS}=0$ , e portanto expande-se a equação como

$$\Delta I_d = \frac{\Delta \beta}{2} (V_{\text{GS}} - V_{\text{th}})^2 - \beta (V_{\text{GS}} - V_{\text{th}}) \Delta V_{\text{th}} . \tag{3.13}$$

Dividindo este resultado por (3.11), obtêm-se a variação da corrente em relação a média como

$$\frac{\Delta I_d}{I_d} = \frac{\Delta \beta}{\beta} - \frac{2\Delta V_{\mathsf{th}}}{V_{\mathsf{GS}} - V_{\mathsf{th}}} \,, \tag{3.14}$$

que pode ser reescrita em função do nível de inversão como

$$\frac{\Delta I_d}{I_d} = \frac{\Delta \beta}{\beta} - \Delta V_{\text{th}} \cdot \frac{g_m}{I_d} \,. \tag{3.15}$$

Por fim, deve-se generalizar o resultado levando em consideração a distribuição estatística dos parâmetros (PELGROM; DUINMAIJER; WELBERS, 1989), resultando em

$$\frac{\sigma(\Delta I_d)}{I_d} = \sqrt{\left(\frac{\sigma(\Delta\beta)}{\beta}\right)^2 + \left(\sigma(\Delta V_{\text{th}}) \cdot \frac{g_m}{I_d}\right)^2} \ . \tag{3.16}$$

Como explicado na Seção 2, a diferença entre as tensões nas entradas do comparador resulta no aparecimento de uma corrente diferencial no circuito, que leva a regeneração das tensões na saída do circuito. Considerando que o *mismatch* também causa o aparecimento de uma corrente diferencial, pode-se modelar esta variação de corrente como uma mudança efetiva nas tensões vistas nas portas dos transistores, para componentes perfeitamente casados. Para isso, multiplica-se (3.16) por  $I_d/g_m$ , obtendo-se

$$\sigma(\Delta V_{\rm GS}) = \sqrt{(\sigma(\Delta V_{\rm th}))^2 + \left(\frac{\sigma(\Delta \beta)}{\beta} \cdot \frac{I_d}{g_m}\right)^2} \ . \tag{3.17}$$

A Figura 9 exemplifica esse modelo de representação no comparador. Ainda, a influência

Figura 9 - Representação do Mismatch no Comparador

Fonte: Autor (2023)

de cada uma destas variações de tensão pode ser resumida a uma variação equivalente na entrada do par diferencial  $\sigma(V_{\rm os})$ , denominada de *offset*. Esta relação é direta para os transistores  $M_{1,2}$ , enquanto que para os pares  $M_{3,4}$  e  $M_{5,6}$ , deve-se referir as variações de tensão a entrada do comparador através do ganho no início de condução de cada um destes pares. Para os transistores  $M_{3,4}$  utiliza-se o ganho da etapa de *sampling*  $A_{v_{\rm smp}}$ , enquanto que para  $M_{5,6}$  utiliza-se o ganho acumulado ao final da propagação  $A_v$ . A raiz da soma da variância de cada uma destas contribuições resulta no *offset* equivalente visto

pelo comparador, e é dado por

$$\sigma(V_{\text{os}}) = \sqrt{\left(\sigma(\Delta V_{\text{GS}_{1,2}})\right)^2 + \left(\frac{\sigma(\Delta V_{\text{GS}_{3,4}})}{A_{v_{\text{smp}}}}\right)^2 + \left(\frac{\sigma(\Delta V_{\text{GS}_{5,6}})}{A_v}\right)^2}$$

(3.18)

Os parâmetros  $\sigma(\Delta V_{\text{th}})$  e  $\sigma(\Delta\beta)/\beta$  que compõe a expressão (3.17) são caracterizados por uma distribuição gaussiana centrada em zero, e (PELGROM; DUINMAIJER; WELBERS, 1989) mostra que elas podem ser modeladas como a soma de duas contribuições diferentes, uma relacionada a área do componente, e outra relacionada a distância entre os componentes no *waffer* de fabricação. Considerando que os transistores estão lado a lado na fabricação do comparador, pode-se descartar esta componente, chegando na expressão (3.19), que mostra o desvio padrão para um parâmetro  $\alpha$  de fabricação.

$$\sigma(\alpha) = \frac{A_{\alpha}}{\sqrt{WL}} \,. \tag{3.19}$$

O parâmetro  $A_{\alpha}$  é chamado de constante de proporcionalidade de área, e pode ser obtida através de simulações, que serão discutidas posteriormente, ou através de *look up tables* da tecnologia, normalmente disponibilizada por fabricantes. Dessa forma é possível determinar as contribuições de cada par de transistores para o *offset* do comparador com base no conhecimento deste da constante de proporcionalidade de área de cada parâmetro, e da área dos transistores utilizados. Utilizando este conceito, escreve-se a contribuição de cada par para o *offset* como

$$\begin{split} &\sigma(\Delta V_{\text{GS}_{M_{1,2}}}) = \sqrt{\left(\frac{A_{\text{vth}_{M_{1,2}}}^2}{W_{M_{1,2}}L}\right) + \left(\frac{A_{\beta_{M_{1,2}}}^2}{W_{M_{1,2}}L}\right) \left(\frac{I_d}{g_m}\right)^2} \\ &\sigma(\Delta V_{\text{GS}_{M_{3,4}}}) = \sqrt{\left(\frac{A_{\text{vth}_{M_{3,4}}}^2}{W_{M_{3,4}}L}\right) + \left(\frac{A_{\beta_{M_{3,4}}}^2}{W_{M_{3,4}}L}\right) \left(\frac{I_d}{g_m}\right)^2} \\ &\sigma(\Delta V_{\text{GS}_{M_{5,6}}}) = \sqrt{\left(\frac{A_{\text{vth}_{M_{3,4}}}^2}{W_{M_{5,6}}L}\right) + \left(\frac{A_{\beta_{M_{5,6}}}^2}{W_{M_{5,6}}L}\right) \left(\frac{I_d}{g_m}\right)^2} \;. \end{split} \tag{3.20}$$

O modelo apresentado por (PELGROM; DUINMAIJER; WELBERS, 1989) para a determinação do *offset* do comparador é limitado, já que considera uma quantidade reduzida de parâmetros, através de uma extrapolação baseada na operação em saturação dos componentes. Entretanto, estes resultados oferecem uma aproximação boa o suficiente para o problema apresentado. Um modelo mais completo é proposto em (DRENNAN; MCANDREW, 1999), enquanto que (BOSCH; STEYAERT; SANSEN, 2004) apresenta um compilado de modelos de *mismatch*.

Das expressões obtidas, pode-se destacar alguns parâmetros que podem ser pro-

jetados com o fim de limitar o *offset* do circuito. O primeiro, e mais facilmente identificável, é a área dos transistores utilizados. O comprimento de canal L é normalmente definido como o valor mínimo permitido pela tecnologia, e portanto tem-se que a principal escolha de projeto é a largura de canal W. Entretanto, das seções anteriores, sabe-se que um aumento de W impacta diretamente as capacitâncias do circuito, o que leva tanto a um aumento do consumo de potência, quanto a uma possível redução na velocidade do circuito, colocando estes critérios de projeto em conflito.

Contudo, pelas equações (3.19) e (3.20), nota-se que, para um mesmo valor de W, as contribuições de cada par de transistores são diferentes entre si, pela relação do ganho do circuito no momento da entrada em condução do par em questão. Dessa forma, as dimensões dos transistores  $M_1$  e  $M_2$ , que compõe o par diferencial, acabam por ser mais impactantes o *offset* do circuito. Com isso, é possível balancear o *offset* primariamente através de um aumento da área destes transistores, limitando o impacto sobre a potência e velocidade do circuito, já que os transistores  $M_3-M_6$  podem permanecer pequenos, em comparação.

Por fim, observa-se também que a componente  $\sigma(\Delta\beta)$  de  $\sigma(\Delta V_{\rm os})$  é influenciada por um ganho igual ao inverso do nível de inversão  $g_m/I_d$  do circuito. Dessa forma, podese reduzir o impacto desta componente ao operar com uma relação de  $g_m/I_d$  elevada, ou seja, em inversão fraca ou moderada. A operação em inversão fraca é obtida quando  $V_{\rm GS} < V_{\rm th}$ , enquanto que a inversão moderada é caracterizada por  $V_{\rm GS} \approx V_{\rm th}$ . Estas condições podem ser atingidas pela determinação da tensão de modo comum do circuito  $V_{\rm CM}$ , cujos demais impactos foram previamente discutidos. Valores típicos de  $g_m/I_d$  quando em inversão moderada estão em torno de  $10-20V^{-1}$ , e cerca de  $30V^{-1}$  para inversão fraca, o que torna a componente relacionada a  $\beta$  desprezível.

Para o projeto de um comparador, é preciso garantir que  $\sigma(V_{\text{os}})$  seja inferior a um determinado valor aceitável de *offset*  $\epsilon$ , ou seja,  $\sigma(V_{\text{os}}) < \epsilon$ . Este valor é escolhido com base na aplicação desejada, e deve levar em conta a taxa de erro de comparação aceitável. Entretanto, como este é um parâmetro estatístico, com distribuição normal, ele não garante que todos os circuitos fabricados com base no projeto atendam o critério estabelecido. Quando é feito um projeto em que  $\sigma(V_{\text{os}}) < \epsilon$ , garante-se que cerca de 68.26% dos circuitos fabricados apresentarão *offset* inferior a  $\epsilon$ . Dessa forma, para garantir a robustez do projeto para a maior parte das situações, deve-se realizar o projeto considerando requisitos mais rígidos. Por exemplo, para  $3\sigma(V_{\text{os}}) < \epsilon$ , garante-se robustez para 99.73% das situações.

#### 3.5 RUÍDO

Assim como o *offset*, o ruído pode ser entendido como uma variação na tensão de entrada do comparador, alterando a polarização dos transistores e podendo levar a um erro de comparação. Da mesma forma, o ruído também assume valores dentro de uma distribuição gaussiana com média zero. Entretanto, diferente do *offset*, o ruído não se torna um valor determinístico uma vez que o circuito é construído, se mantendo sempre um valor aleatório, dentro de sua distribuição estatística, para cada comparação realizada.

No comparador, o ruído de entrada do circuito aparece como uma diferença entre as tensões nos nós P e Q durante o sampling, e nos nós X e Y durante a propagação, através da integração de uma corrente diferencial  $i_{\rm n}(t)$  nas capacitâncias respectivas (WHITEHEAD, 2019). Assumindo que  $C_{P,Q} > 2C_{X,Y}$ , pode-se reduzir o impacto do ruído somente ao estágio de sampling, dado por

$$v_{\mathsf{n}_{P,Q}} = \frac{1}{C_{P,Q}} \int_0^{t_{\mathsf{smp}}} i_{\mathsf{n}}(t) dt$$

(3.21)

Contudo, o resultado de interesse não é  $v_{\mathbf{n}_{P,Q}}$ , mas sim a variância  $\overline{v_{\mathbf{n}_{P,Q}}^2}$ , dado por

$$\overline{v_{n_{P,Q}}^2} = \frac{2}{C_{P,Q}^2} E\left[ \left( \int_0^{t_{smp}} i_{n}(t) dt \right)^2 \right] , \qquad (3.22)$$

em que o fator de 2 aparece devido a soma das variâncias de  $M_1$  e  $M_2$ . Considerando que a potência não é uma operação linear, não é possível alterar a ordem das operações de média e integração. Por isso, deve-se substituir a operação da integral ao quadrado por uma integral dupla, resultando em

$$\overline{v_{\mathsf{n}_{P,Q}}^2} = \frac{2}{C_{P,Q}^2} E\left[ \int_0^{t_{\mathsf{smp}}} \int_0^{t_{\mathsf{smp}}} i_{\mathsf{n}}(t) \cdot i_{\mathsf{n}}(t') dt dt' \right] . \tag{3.23}$$

A partir desta manipulação, pode-se inverter a ordem das operações, e resolver primeiro  $E[i_{\rm n}(t)\cdot i_{\rm n}(t')]$ , que é a autocorrelação do ruído de  $M_{1,2}$ , que para o ruído térmico, é dado por  $2kT\gamma g_m\delta(t)$  (NUZZO et al., 2008), onde k é a constante de Boltzmann, T é a temperatura absoluta em Kelvin e  $\gamma$  é um parâmetro da tecnologia. Substituindo este resultado em (3.23), e resolvendo a integral dupla, tem-se que o resultado é

$$\overline{v_{{\rm n}_{P,Q}}^2} = \frac{4kT\gamma g_m t_{\rm smp}}{C_{P,Q}^2} \ .$$

(3.24)

Para referir este resultado a entrada do comparador, basta dividi-lo pelo quadrado do ganho

do estágio de sampling, cujo resultado é

$$\overline{v_{\rm n_{in}}^2} = \frac{4kT\gamma g_m t_{\rm smp}}{A_v^2 C_{P,Q}^2} = \frac{4kT\gamma}{V_{\rm th} C_{P,Q}} \cdot \frac{I_d}{g_m}, \qquad C_{P,Q} > 2C_{X,Y} \ . \tag{3.25}$$

Caso a suposição de que  $C_{P,Q} > 2C_{X,Y}$  não for verdadeira, deve-se considerar o impacto do ruído para além do tempo de *sampling*. Em (XU; ABIDI, 2019), são deduzidas expressões para as demais relações entre  $C_{P,Q}$  e  $C_{X,Y}$ , mostradas nas equações (3.26) e (3.27).

$$\overline{v_{\mathsf{n}_{\mathsf{in}}}^2} = \frac{4kT\gamma}{V_{\mathsf{th}}(2C_{P,Q} + C_{X,Y})} \cdot \frac{I_d}{g_m}, \qquad 2C_{P,Q} < C_{X,Y}$$

(3.26)

$$\overline{v_{\mathsf{n}_{\mathsf{in}}}^2} = \frac{8kT\gamma}{V_{\mathsf{th}}(3C_{P,Q} + C_{X,Y})} \cdot \frac{I_d}{g_m}, \qquad C_{P,Q} \approx C_{X,Y}$$

(3.27)

Com relação ao ruído *flicker*, sabe-se que sua variância cai proporcionalmente com a frequência (GüLER; PUSANE; DüNDAR, 2014), e considerando que o tempo de integração da corrente diferencial durante o *sampling* e propagação é da casa dos pico segundos, sua contribuição para o ruído do comparador pode ser ignorada.

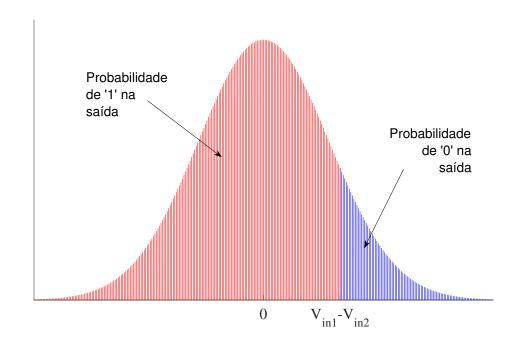

Ainda, pode-se determinar o ruído referido a tensão de entrada experimentalmente, a partir de uma simulação transiente com ruído. Primeiro, deve-se desbalancear levemente a tensão de entrada do circuito com um valor constante  $|V_{\rm in_1}-V_{\rm in_2}|>0$ , de forma a alterar a probabilidade de a saída assumir valores de zero ou um (RAZAVI, 2020), como exemplificado na Figura 10.

Figura 10 — Probabilidade de a Comparação Resultar em '1' ou '0' Devido a um Desbalanço  $V_{\mathrm{in}_1}-V_{\mathrm{in}_2}$

Fonte: Adaptado de (RAZAVI, 2015)

O circuito deve ser simulado por um grande números de ciclos de clock, onde cada resultado da comparação deve ser amostra-do. Com os resultados da amostragem, podese determinar a probabilidade P de a saída assumir valores iguais um, em respeito a tensão de entrada utilizada na simulação. Dado que o ruído assume distribuição normal, determinar-se seu desvio padrão  $\sigma(v_{\rm n})$  utilizando a função de erro inversa (GILES, 2012), como mostrado pela equação (3.28).

$$\sigma(v_{\mathsf{n}}) = \left| \frac{V_{\mathsf{in}_1} - V_{\mathsf{in}_2}}{\sqrt{2} \cdot \mathsf{inverf}\{2P - 1\}} \right| . \tag{3.28}$$

#### 3.6 KICKBACK NOISE

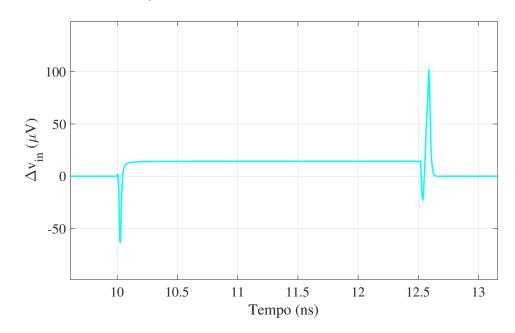

O *kickback noise* é caracterizado por uma variação da tensão de entrada em decorrência de uma mudança na tensão dos nós do circuito, acoplados através das capacitâncias parasitas dos transistores. A Figura 11 mostra as principais capacitâncias que causam este efeito, em que  $C_{\rm in}$  denota a capacitância de saída do circuito anterior (RAZAVI, 2015).

$C_{GD_1}$  P Q  $C_{GD_2}$   $V_{in}$   $C_{in}$   $C_{GS_1}$   $C_{GS_2}$   $C_{GS_2}$   $C_{GS_2}$

Figura 11 - Capacitâncias para a Análise do kickback noise

Fonte: Adaptado de (RAZAVI, 2015)

Notam-se duas influências simultâneas nas tensões de entrada, uma decorrente da mudança de *clock* no *gate* de  $M_0$  através da associação das capacitâncias  $C_{\mathrm{GD}_0}$  e  $C_{\mathrm{GS}_1}$ , e a outra da mudança de tensão no dreno de  $M_1-M_2$ , através da capacitância  $C_{\mathrm{GD}_1}$ . O efeito total sobre a tensão na entrada é dado pela soma destas parcelas, mostrado na

equação (3.29), em que  $C_{\mathsf{CLK}} = C_{\mathsf{GD}_0} || C_{\mathsf{GS}_1}$ .

$$\Delta v_{\rm in_+} = \Delta V_{\rm CLK} \frac{C_{\rm CLK}}{C_{\rm CLK} + C_{\rm in}} + \Delta V_{P,Q} \frac{C_{\rm GD_1}}{C_{\rm GD_1} + C_{\rm in}} \ . \tag{3.29} \label{eq:deltavin_point}$$

Considerando que, normalmente,  $C_{\rm in} >> C_{\rm CLK}, C_{\rm GD_1}$ , pode-se dizer que o efeito do *kickback noise* cresce linearmente com o aumento da largura de canal W dos transistores, dado a relação com as capacitâncias parasitas. Ainda, quanto maior a capacitância utilizada para o sinal de entrada, menos impactante é o efeito do *kickback noise*.

Outra característica é que as duas parcelas da equação (3.29) são sempre opostas em sinal, já que a subida do *clock* leva ao descarregamento dos nós P e Q, enquanto que a descida do *clock* leva a carga dos nós de volta a  $V_{\rm dd}$ . Ainda, dado que  $C_{\rm CLK} > C_{\rm GD_1}$ , devido a associação em série, o efeito da variação de tensão em P e Q domina o efeito sobre a entrada.

### 4 EXTRAÇÃO DOS PARÂMETROS DA TECNOLOGIA

Os parâmetros de tecnologia são normalmente disponibilizados em arquivos PDK (*Process Design Kit*) da tecnologia utilizada. Entretanto, caso nesta seção são mostradas maneiras de encontrar estes parâmetros de forma experimental.

#### 4.1 PARÂMETROS DE MISMATCH

Para o início do projeto do comparador, é necessário identificar os parâmetros  $A_{v_{\text{th}}}$  e  $A_{\beta}$  que relacionam o *mismatch* do transistor com a sua área, chamados de constantes de proporcionalidade de área. Estes parâmetros permitem definir a área WL mínima dos transistores de modo a limitar  $\sigma(\Delta V_{\text{GS}})$  a um valor máximo  $\epsilon$ , definido pela seguinte desigualdade

$$\sigma(\Delta V_{\rm GS}) = \sqrt{\left(\frac{A_{V_{\rm th}}^2}{WL}\right) + \left(\frac{A_{\beta}^2}{WL}\right) \left(\frac{I_d}{g_m}\right)^2} < \epsilon \ . \tag{4.1}$$

De acordo com as discussões sobre *offset* anteriores, sabemos que operar na inversão fraca ou moderada limita a influência de  $\sigma(\Delta\beta)/\beta$ . Assumindo que o comparador opera nesta, podemos desconsiderar esta parcela, o que resume o *offset* do circuito a sua parcela relacionada a  $\sigma(\Delta V_{\text{th}})$ , ou seja

$$\sigma(\Delta V_{\rm GS}) = \sigma(\Delta V_{\rm th}) = \frac{A_{V_{\rm th}}}{\sqrt{WL}}$$

(4.2)

Manipulando o resultado de (4.2), podemos escrever  $A_{V_{th}}$  como

$$A_{V_{\text{th}}} = \sigma(\Delta V_{\text{th}}) \sqrt{WL} \ . \tag{4.3}$$

Dessa forma, extraindo os resultados de  $\sigma(\Delta V_{\text{th}})$  para diferentes valores de W, pode-se definir o valor da constante de proporcionalidade. Isso pode ser feito através de uma simulação DC, em que se realiza uma simulação Monte Carlo para cada W, em um único transistor polarizado com uma tensão  $V_{\text{GS}}$  de interesse, cujo resultado deve ser multiplicado por  $\sqrt{2}$  de forma a considerar a relação entre dois transistores.

Para este projeto, utilizou-se uma tensão  $V_{\rm GS}=0.55V$ , valor equivalente a tensão de modo comum utilizada no comparador. A largura W foi variada entre  $5\mu m$  e  $120\mu m$  com passo de  $5\mu m$ , com dez mil iterações da simulação monte carlo cada.

Ainda, a extração de parâmetros foi realizada para dois tipos diferentes de construções de transistores, sendo elas a padrão e a *low-Vth*, ou *low voltage threshold*. A primeira é a utilizada para a maior parte dos transistores do circuito, enquanto que a se-

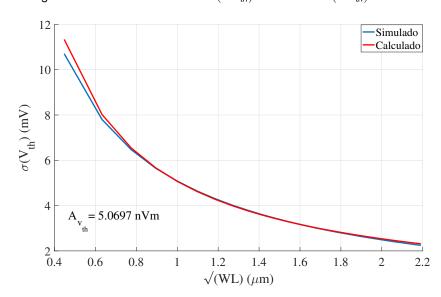

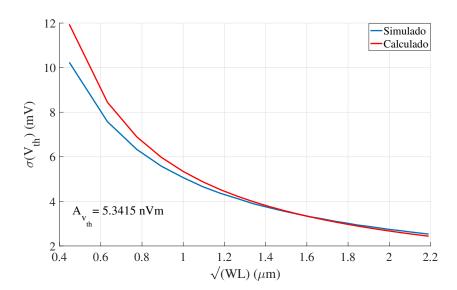

gunda será utilizada para os transistores do par diferencial. O motivo é que a tensão de limiar padrão da tecnologia é aproximadamente 0.6V, valor superior a tensão de modo comum utilizada, o que degradaria a velocidade do circuito, enquanto que a lvt possui tensão de limiar de aproximadamente 0.5V. Com o resultado das simulações, encontra-se  $A_{V_{\rm th}} = A_{V_{\rm th}_{M_{3,4}}} \approx 5.0697 \cdot 10^{-9} Vm$ ,  $A_{V_{\rm th}}^{\rm lvt} = A_{V_{\rm th}_{M_{1,2}}} \approx 5.3415 \cdot 10^{-9} Vm$ .

Na Figura 12 e Figura 13 são mostradas a comparação das curvas obtidas através de simulação com as construídas a partir do parâmetro extraído. Das curvas obtidas, notase que o modelo calculado é mais preciso para valores grandes de  $\sqrt{WL}$ , e se afasta dos resultados simulados quanto menor for este parâmetro. De qualquer forma, os resultados são próximos o suficiente para o início do projeto do comparador.

Figura 12 – Transistor Normal -  $\sigma(\Delta V_{\rm th})$  Simulado e  $\sigma(\Delta V_{\rm th})$  Calculado

Fonte: Autor (2023)

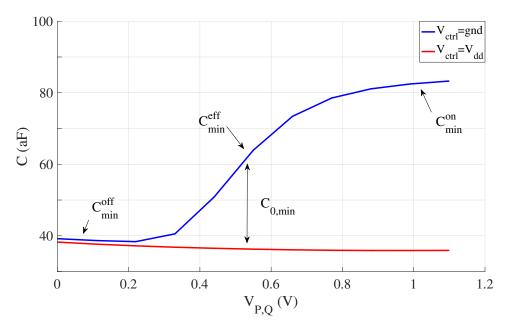

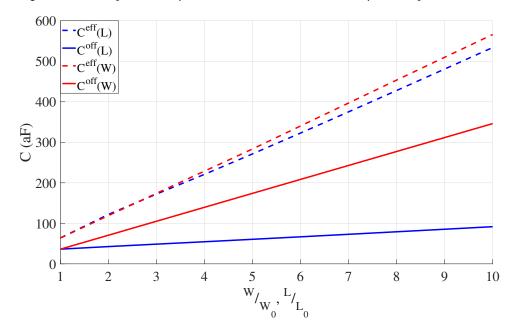

### 4.2 CAPACITÂNCIAS

As capacitâncias equivalentes dos nós do comparador são parâmetros comuns a grande parte das expressões que regem o comportamento do circuito. Para obter uma estimativa destes valores, pode-se extrair as capacitâncias parasitas de um transistor base, polarizado de forma a reproduzir a região de operação de interesse. Para os transistores NMOS, as regiões de operação de interesse são definidas como a metade da fase de sampling e metade da fase de propagação. Para os transistores PMOS, o ponto de operação definido é a metade da propagação. A Tabela (1) mostra os valores obtidos para um transistor de  $1\mu m$ .

A partir destas informações, é possível determinar as capacitâncias equivalentes

Figura 13 – Transistor Ivt -  $\sigma(\Delta V_{\rm th})$  Simulado e  $\sigma(\Delta V_{\rm th})$  Calculado

Tabela 1 - Relação das Capacitâncias para Ponto de Operação Correspondente

|                               | NMOS                                 | NMOS                                                   | PMOS                                 |

|-------------------------------|--------------------------------------|--------------------------------------------------------|--------------------------------------|

| Ponto de                      | $V_{ m D} = V_{ m dd} - V_{ m th}/2$ | $V_{ m D}=V_{ m dd}$                                   | $V_{ m D} = V_{ m dd} - V_{ m th}/2$ |

| Operação                      | $V_{S} = gnd$                        | $V_{\mathrm{S}} = V_{\mathrm{dd}} - V_{\mathrm{th}}/2$ | $V_{ m S} = V_{ m dd}$               |

| Operação                      | $V_{G} = V_{CM}$                     | $V_{G} = V_{dd}$                                       | $V_{ m G} = V_{ m dd} - V_{ m th}/2$ |

| $C'_{ox}$                     | $12.9525mF/m^2$                      | $4.6160mF/m^2$                                         | $4.7030mF/m^2$                       |

| $C_{SB}/W$                    | _                                    | $0.35 fF/\mu m$                                        | _                                    |

| $C_{DB}/W$                    | $0.35 fF/\mu m$                      | $0.32 fF/\mu m$                                        | $0.29 fF/\mu m$                      |

| $C_{GD}/W$                    | $0.11 fF/\mu m$                      | $0.12 fF/\mu m$                                        | $0.12 fF/\mu m$                      |

| $C_{\rm GS}/W$ $0.34fF/\mu m$ |                                      | $0.12 fF/\mu m$                                        | $0.13fF/\mu m$                       |

Fonte: Autor (2023)

nos nós somando as parcelas respectivas de cada transistor. O cálculo de  $\mathcal{C}_{P,Q}$  é dado por

$$C_{P,Q} = W_{1,2} \cdot (C_{DB}/W + C_{GD}/W)$$

$$+W_{3,4} \cdot (C_{SB}/W + C_{GS}/W)$$

$$+W_{7,10} \cdot (C_{DB}/W + C_{GS}/W) ,$$

$$(4.4)$$

que substituindo pelos valores da Tabela (1) resulta em

$$C_{P,Q} = W_{1,2} \cdot (0.46fF/\mu m) + W_{3,4} \cdot (0.47fF/\mu m) + W_{7,10} \cdot (0.42fF/\mu m).$$

(4.5)

Já o valor de  $C_{X,Y}$  é obtido através de

$$C_{X,Y} = W_{3,4} \cdot (C_{DB}/W + C_{GS}/W + C_{GD}/W)$$

$$+W_{5,6} \cdot (C_{DB}/W + C_{GS}/W + C_{GD}/W)$$

$$+W_{8,9} \cdot (C_{DB}/W + C_{GS}/W) ,$$

$$(4.6)$$

que a substituindo pelos valores correspondentes da Tabela (1) resulta em

$$C_{X,Y} = W_{3,4} \cdot (0.56fF/\mu m) + W_{5,6} \cdot (0.56fF/\mu m) + W_{8,9} \cdot (0.42fF/\mu m).$$

(4.7)

# 5 PROJETO DE COMPARADOR SEM CALIBRAÇÃO DE *OFFSET*

Neste capítulo será desenvolvido o projeto de um comparador que não utiliza circuito auxiliar para a calibração de *offset*, dependendo apenas das relações de área dos transistores. É estabelecido como requisito para o projeto que o comparador apresente  $\sigma(V_{\rm os}) < 1.5~mV$ .

# 5.1 DEFINIÇÃO DO PAR DIFERENCIAL $M_1-M_2$

Para o projeto do comparador sem compensação, inicialmente considera-se o critério de projeto de  $\sigma(V_{\rm os}) < 1.5 mV$  e determina-se, através dos parâmetros extraídos, o tamanho mínimo dos transistores para cumprir com esta condição. Substituindo (3.20) em (3.18) e desconsiderando-se a influência de  $A_{\beta}$ , devido a consideração de operação em inversão fraca, tem-se que o *offset* é dado por

$$\sigma(V_{\text{os}}) = \sqrt{\frac{(A_{\text{vth}_{M_{1,2}}})^2}{W_{M_{1,2}}L} + \frac{1}{A_{v_{\text{smp}}}^2} \frac{(A_{\text{vth}_{M_{3,4}}})^2}{W_{M_{3,4}}L} + \frac{1}{A_v^2} \frac{(A_{\text{vth}_{M_{5,6}}})^2}{W_{M_{5,6}}L}} .$$

(5.1)

Sabendo ainda que a maior parte do *offset* do circuito é referente ao par diferencial, já que a contribuição dos demais pares são divididas pelo ganho do estágio referente, podese aproximar o *offset* do circuito apenas pelas contribuições de  $M_1$  e  $M_2$ , resultando na expressão

$$\sigma(V_{\rm os}) pprox \sqrt{\frac{(A_{{\rm vth}_{M_{1,2}}})^2}{W_{M_{1,2}}L}} \; ,$$

(5.2)

que resolvida para  $\sigma(V_{\rm os})=1.5mV$ , resulta em  $W_{M_{1,2}}\approx 320\mu m$ .

Com esta escolha de largura de canal para o par diferencial, garante-se que o *offset* do circuito estará em torno do requisito de projeto. Posteriormente, em outras etapas de projeto, deverá ser feito um ajuste fino na escolha deste parâmetro, de forma a considerar o impacto dos demais transistores, bem como otimizar a velocidade e ganho do circuito.

# 5.2 DEFINIÇÃO DO TRANSISTOR DE CAUDA $M_{ m 0}$

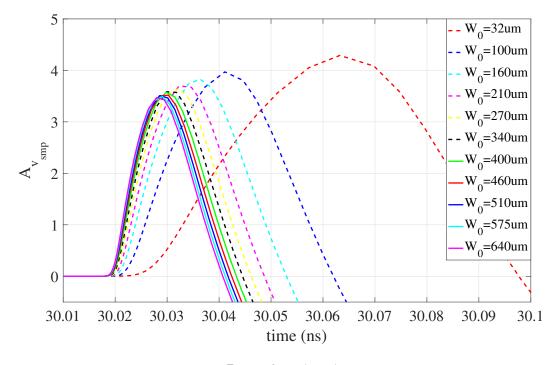

Definido as larguras de canal de  $M_1-M_2$ , prossegue-se para a definição do transistor de cauda  $M_0$  do circuito. Como explorado na seção referente a velocidade do circuito, este transistor impacta de forma direta a corrente de modo comum do circuito, e portanto influencia o ganho e velocidade de comparação. Dessa forma, um bom objetivo para a de-

finição da largura W deste componente é a maximização da relação ganho/velocidade do circuito, ou seja, encontrar o valor em que continuar a reduzir  $W_0$  não ofereça um aumento significativo no ganho do circuito em relação a sua velocidade de comparação.