#### UNIVERSIDADE FEDERAL DE SANTA MARIA CENTRO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Veridiane Lopes Rosa

ANÁLISE DE TOPOLOGIAS PARA LÂMPADA BULBO LED UTILIZANDO DISPOSITIVOS SEMICONDUTORES DE NITRETO DE GÁLIO OPERANDO EM 1MHZ

#### Veridiane Lopes Rosa

# ANÁLISE DE TOPOLOGIAS PARA LÂMPADA BULBO LED UTILIZANDO DISPOSITIVOS SEMICONDUTORES DE NITRETO DE GÁLIO OPERANDO EM 1MHZ

Dissertação apresentada ao Curso de Mestrado do Programa de Pós-Graduação em Engenharia Elétrica, Área de Concentração em Sistemas de Iluminação da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para a obtenção do título de **Mestre em Engenharia Elétrica**

Orientador: Prof. Dr. Ricardo Nederson do Prado

Rosa, Veridiane

ANÁLISE DE TOPOLOGIAS PARA LÂMPADA BULBO LED

UTILIZANDO DISPOSITIVOS SEMICONDUTORES DE NITRETO DE

GÁLIO OPERANDO EM 1MHZ / Veridiane Rosa. - 2018.

119 p.; 30 cm

Orientador: Ricardo Nederson do Prado Dissertação (mestrado) - Universidade Federal de Santa Maria, Centro de Tecnologia, Programa de Pós-Graduação em Engenharia Elétrica, RS, 2018

1. Nitreto de Gálio 2. Perdas 3. Conversor Ressonante 4. Bulbo LED I. Nederson do Prado, Ricardo II. Título.

Sistema de geração automática de ficha catalográfica da UFSM. Dados fornecidos pelo autor(a). Sob supervisão da Direção da Divisão de Processos Técnicos da Biblioteca Central. Bibliotecária responsável Paula Schoenfeldt Patta CRB 10/1728.

#### ©2018

Todos os direitos autorais reservados a Veridiane Lopes Rosa. A reprodução de partes ou do todo deste trabalho só poderá ser feita mediante a citação da fonte.

Endereço: Travessa José Aita, n. 34, Bairro Menino Jesus, Santa Maria, RS. CEP:97050-400 Fone (0xx)55 3026 4376; E-mail: veridiane.rosa@gmail.com

#### Veridiane Lopes Rosa

#### ANÁLISE DE TOPOLOGIAS PARA LÂMPADA BULBO LED UTILIZANDO DIPOSITIVOS SEMICONDUTORES DE NITRETO DE GÁLIO OPERANDO EM 1MHZ

Dissertação apresentada ao Curso de Mestrado do Programa de Pós-Graduação em Engenharia Elétrica, Área de Concentração em Sistemas de Iluminação da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para a obtenção do título de **Mestre em Engenharia Elétrica**

Aprovado em 31 de agosto de 2018

Ricardo Nederson do Prado, Dr.(UFSM)

Presidente/Orientador

Marcelo Rafael Cosetin, Dr.(UFSM)

Jumar Luis Russi, Dr. (UNIPAMPA)

Santa Maria, RS 2018

# DEDICATÓRIA Aos meus pais Clóvis e Vera, que sempre apoiaram nas minhas decisões e me guiaram na minha jornada até aqui.

#### **AGRADECIMENTOS**

Agradeço aos meus pais por todo o apoio, motivação, educação e carinho dados. Não conseguiria ser o que sou hoje sem o amor e apoio de vocês.

Aos meus irmãos, Clóvisson e Victória, por sempre estarem dispostos a me ajudar mesmo não entendo o meu objeto de pesquisa.

Ao meu orientador, professor Ricardo Nederson do Prado, pela orientação e incentivo durante toda a graduação e mestrado.

Ao Dr. Marcelo Rafael Cosetin por toda a ajuda no desenvolvimento desta dissertação, por sanar minhas dúvidas e por compartilhar seu conhecimento comigo.

Ao Me. Renan Rodrigo Duarte por ter me ajudado a compreender um pouco mais a tecnologia sobre nitreto de gálio e por sanar minhas dúvidas.

Aos membros do grupo GEDRE pelo ótimo ambiente de trabalho, por todos conhecimentos compartilhados, coleguismo e amizade. Um agradecimento especial aos colegas Dion Lenon e Thais Bolzan por serem os amigos que foram durante toda essa jornada. Um agradecimento também a Igor Bertoncello e Matheus Righi que contribuíam na realização deste trabalho.

#### **RESUMO**

## ANÁLISE DE TOPOLOGIAS PARA LÂMPADA BULBO LED UTILIZANDO DISPOSITIVOS SEMICONDUTORES DE NITRETO DE GÁLIO OPERANDO EM 1MHZ

AUTORA: Veridiane Lopes Rosa ORIENTADOR: Ricardo Nederson Do Prado

O presente trabalho apresenta o estudo das perdas e da eficiência para três topologias de conversores. Tendo como objetivo avaliar a percentagem de perdas relativas ao semicondutor à base de Nitreto de Gálio (GaN). As topologias empregadas neste trabalho são Buck síncrono, Buck quase-ressonante e conversor ressonante LLC. Para cada uma das topologias são avaliadas as perdas por cálculo, por simulação e de modo experimental, de forma a realizar um comparativo entre os métodos. Com o uso dos métodos de cálculo e de simulação foi possível prever-se o comportamento real dos conversores, assim como avaliar as perdas em cada um dos componentes. Com este trabalho conclui-se que o GaN possui suas limitações em aplicações de baixa potência e em aplicações em comutação forçada. Em aplicações ressonantes as perdas relativas aos semicondutores GaN, são reduzidas significativamente.

Palavras Chave: Perdas, GaN, Conversores Ressonantes.

#### **ABSTRACT**

## ANALYSIS OF TOPOLOGIES FOR BULB LED LAMPS USING GALLIUM NITRIDE SEMICONDUCTORS OPERATING IN 1MHZ

AUTHOR: Veridiane Lopes Rosa ADVISOR: Ricardo Nederson Do Prado

This paper presents the losses and efficiency evaluation to three different topologies. This paper goals are evaluating the losses percental related to the semiconductors devices, Gallium Nitride (GaN). This paper presents the converters: synchronous Buck, quasi-resonant Buck converter and LLC resonant converter. The topologies have their losses evaluated by calculation, simulation and experimental, therefore it is possible to compare the methods. Utilizing the calculation and simulation method is possible to predict the real converter behaviour, as result is possible to evaluate each device losses. In conclusion the Gallium Nitrite have some limitations to low load applications and hard switching operation. In the resonant applications the semiconductor devices, GaN, have their losses decreased.

Keywords: Losses, GaN, Resonant Converters

#### LISTA DE FIGURAS

| Figura 1.1 - Evolução de potência e frequência de acordo com os dispositivos semicondu                                                                            |        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Figura 2.1 - Estrutura do tipo <i>wurtzite</i> do GaN                                                                                                             |        |

| Figura 2.2 - Estrutura do transistor de potência GaN HEMT                                                                                                         |        |

| Figura 2.3 - Componentes intrínsecos da resistência de condução do GaN                                                                                            |        |

| Figura 2.4 - Resistência de condução de acordo com a temperatura: (a) <i>R</i> <sub>DSon</sub> em relação a t                                                     |        |

| entre porta e fonte ( $V_{GS}$ ) e (b) $R_{DSon}$ normalizada                                                                                                     |        |

| Figura 2.5 - Tensão de threshold: (a) Característica de entrada em condução; (b) Normal                                                                           |        |

| em função da temperatura                                                                                                                                          |        |

| Figura 2.6 - Comportamento na condução reversa                                                                                                                    |        |

| Figura 2.7 - Transistor GaN Tipo depleção                                                                                                                         |        |

| Figura 2.8 - Símbolo usual do interruptor GaN do tipo depleção (dGaN)                                                                                             |        |

| Figura 2.9 - Estrutura eGaN – Tipo Intensificação                                                                                                                 |        |

| Figura 2.10 - Símbolo usual do interruptor GaN do tipo intensificação, eGaN                                                                                       |        |

| Figura 2.11 - Simbologia do GaN do tipo Cascode                                                                                                                   | 34     |

| Figura 2.12 - Participação do MOSFET de silício na resistência de condução do interr                                                                              | uptoi  |

| cascode                                                                                                                                                           | 34     |

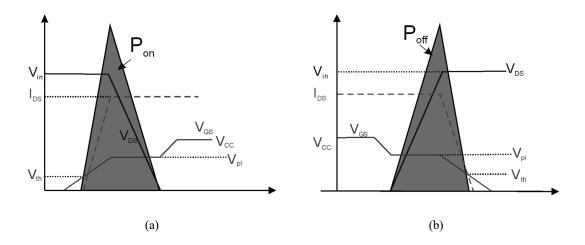

| Figura 3.1 - Curvas idealizadas para cálculo de perda em comutação (a) Turn-on (b) Tun-                                                                           | off 37 |

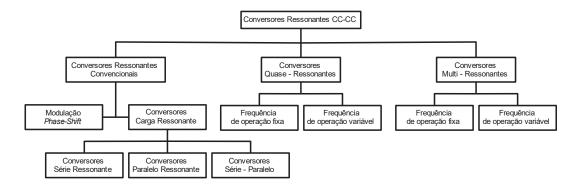

| Figura 3.2 - Classificação dos conversores ressonantes                                                                                                            |        |

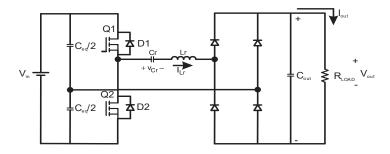

| Figura 3.3 - Exemplo de topologia série ressonante.                                                                                                               | 39     |

| Figura 3.4 - Conversor Paralelo Ressonante Error! Bookmark not def                                                                                                |        |

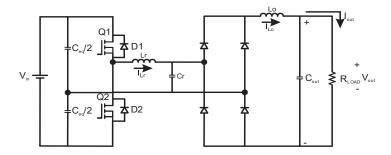

| Figura 3.5 - Tipos do Conversor Ressonante Série-Paralelo: (a) LCC e (b) LLC                                                                                      |        |

| Figura 3.6 - Interruptor Ressonante de comutação com corrente zero (Zero Current Switc                                                                            | _      |

| Figura 3.7 - Interruptor Ressonante de comutação com tensão zero (Zero Voltage Switch)                                                                            |        |

| Figura 3.8 - Topologias buck quase-ressonante do tipo ZCS                                                                                                         |        |

| Figura 3.9 - Topologias <i>boost</i> quase-ressonante do tipo ZCS                                                                                                 |        |

| Figura 3.10 - Formas de onda: (a) buck ZCS; (b) boost ZCS                                                                                                         |        |

| Figura 3.11 - Topologias <i>buck</i> quase-ressonante do tipo ZVS                                                                                                 |        |

| Figura 3.12 - Topologias boost quase-ressonante do tipo ZVS                                                                                                       |        |

| Figura 3.13 - Formas de onda: (a) buck ZVS; (b) boost ZVS                                                                                                         |        |

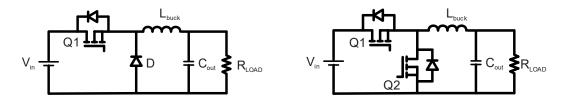

| Figura 4.1-Comparativo entre <i>buck</i> tradicional e síncrono                                                                                                   |        |

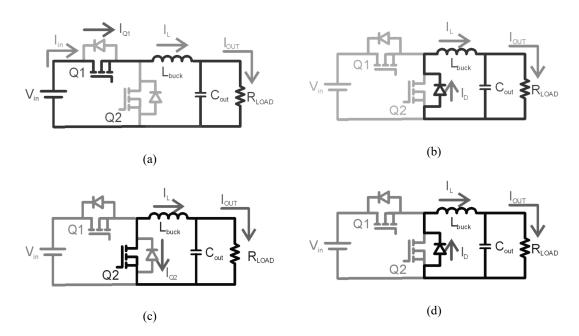

| Figura 4.2-Etapas de operação <i>buck</i> síncrono                                                                                                                |        |

| Figura 4.3 - Principais formas de onda <i>buck</i> síncrono                                                                                                       |        |

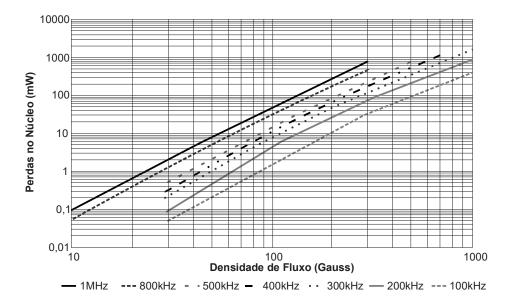

| Figura 4.4 - Gráfico das perdas no indutor                                                                                                                        |        |

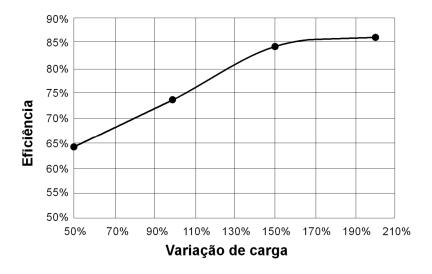

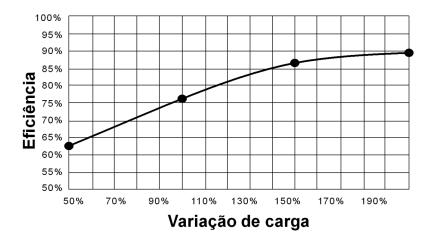

| Figura 4.5 - Eficiências calculadas a partir da variação de carga                                                                                                 |        |

| Figura 4.6 - Distribuição de perdas por análise de cálculo conversor buck síncrono                                                                                |        |

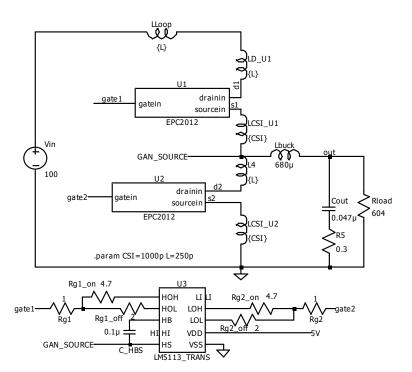

| Figura 4.7 - Esquemático para simulação <i>buck</i> síncrono no LTSpice ©                                                                                         |        |

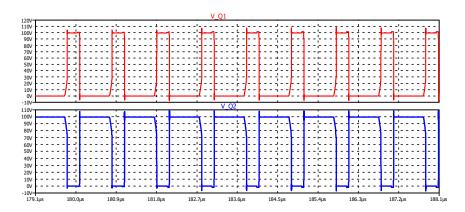

| Figura 4.8 - Tensão <i>VDS</i> sobre interruptores <i>buck</i> síncrono                                                                                           |        |

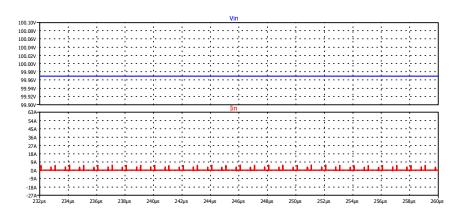

| Figura 4.9-Tensão e corrente de entrada do <i>buck</i> síncrono, simulação LTSPICE©                                                                               |        |

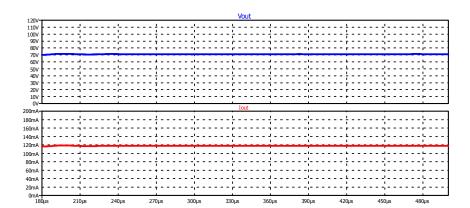

| Figura 4.10 - Tensão e corrente de saída do <i>buck</i> síncrono, simulação LTSPICE©                                                                              |        |

| Figura 4.11 - Variação de eficiência de acordo com a variação de carga via simulação                                                                              |        |

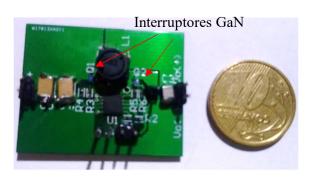

| Figura 4.12 - Placa de circuito impresso desenvolvida para conversor <i>buck</i> síncrono                                                                         |        |

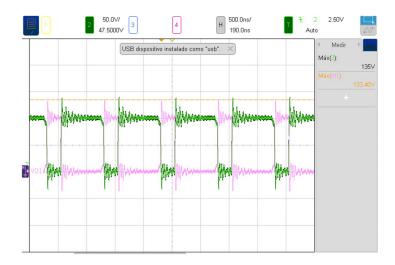

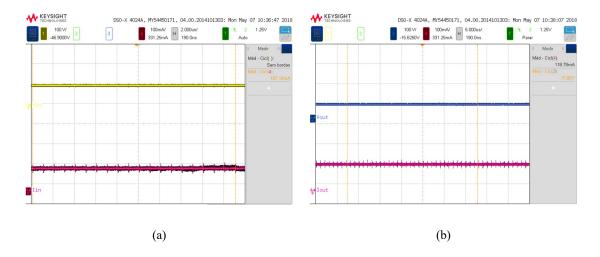

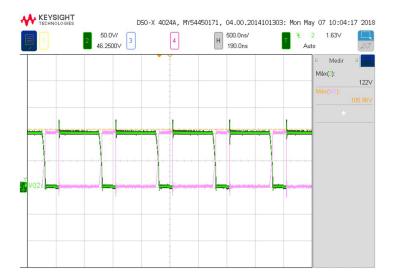

| Figura 4.13 - Resultados experimentais para 50% de carga, tensão e corrente: (a) Entrada                                                                          |        |

| Saída. Canal 1 - Tensão de entrada (50 V/div); Canal 3 - Tensão de saída (50 V/div); Canal Correntes de entrada e saída (50 mA/div). Escala horizontal 500 ns/div |        |

| COLLEGIES DE CHITADA E SAIDA LOU HIA/OLVI. ESCAIA HOTIZONIALOUU HS/OLV                                                                                            | D.     |

| Figura 4.14 - Tensão sobre interruptores para carga de 50%. Canal 2 - Tensão sobre interruptor Q2 (50 V/div); Matemático - Tensão de sobre do interruptor Q1 (50 V/div). Escala horizontal 500 ns/div                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

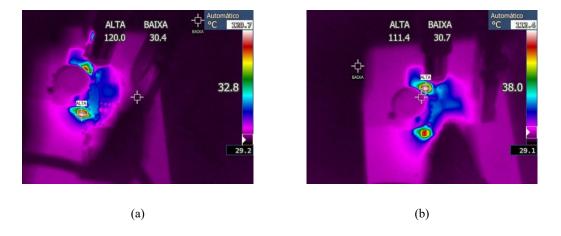

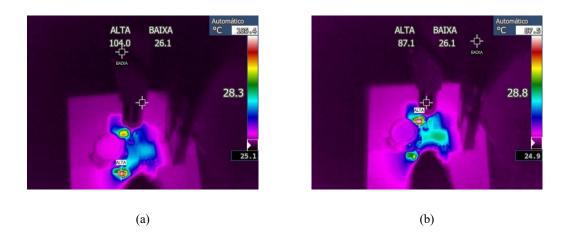

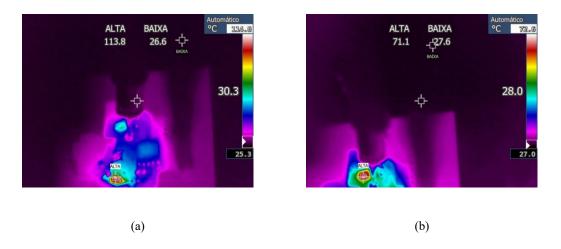

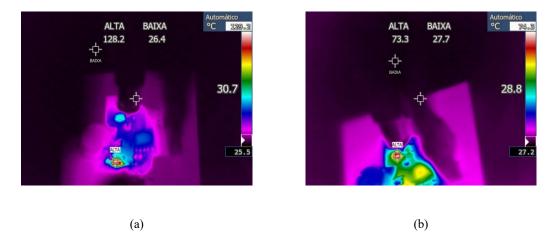

| Figura 4.15 - Temperatura para carga de 50%:(a) Interruptor superior; (b) Interruptor Inferior                                                                                                                                                                                                                                                                                                                                                                                                 |

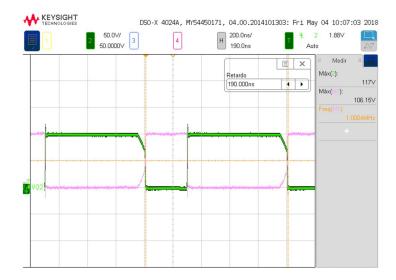

| Figura 4.16 - Resultados experimentais 100% de carga, tensão e corrente: (a) Entrada e (b) Saída Canal 1 - Tensão de entrada (50 V/div); Canal 3 – Tensão de saída (100 V/div); Canal 4 - Correntes de entrada e saída (100 mA/div). Escala horizontal: (a) 2 μs /div; (b) 5 μs/div. 67 Figura 4.17 - Tensão sobre interruptores para carga de 100%. Canal 2 - Tensão sobre interruptor Q2 (50 V/div); Matemático - Tensão de sobre do interruptor Q1 (50 V/div). Escala horizontal 200 ns/div |

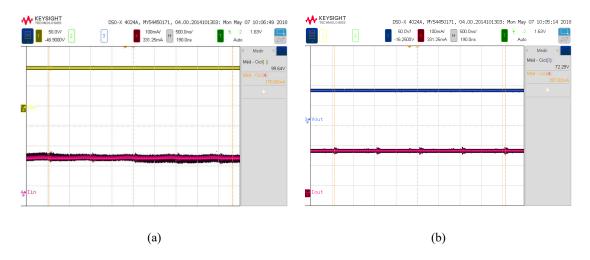

| Figura 4.19 - Resultados experimentais para 150% de carga, tensão e corrente: (a) Entrada e (b) Saída. Canal 1 - Tensão de entrada (50 V/div); Canal 3 – Tensão de saída (50 V/div); Canal 4 - Correntes de entrada e saída (100 mA/div). Escala horizontal: (a) 500 ns/div; (b) 500 ns/div.                                                                                                                                                                                                   |

| Figura 4.20 - Tensão sobre interruptores para carga de 150%. Canal 2 - Tensão sobre interruptor Q2 (50 V/div); Matemático - Tensão de sobre do interruptor Q1 (50 V/div). Escala horizontal 500 ns/div                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figura 4.22 - Resultados experimentais para 200% de carga, tensão e corrente: (a) Entrada e (b) Saída. Canal 1 - Tensão de entrada (50 V/div); Canal 3 - Tensão de saída (50 V/div); Canal 4 - Correntes de entrada e saída (100 mA/div). Escala horizontal 10 μs/div                                                                                                                                                                                                                          |

| Figura 4.23 - Tensão sobre interruptores para carga 200%. Canal 2 - Tensão sobre interruptor Q2 (50 V/div); Matemático - Tensão de sobre do interruptor Q1 (50 V/div). Escala horizontal 500 ns/div                                                                                                                                                                                                                                                                                            |

| Figura 4.24 - Temperatura para carga de 200%:(a) Interruptor superior; (b) Interruptor Inferior                                                                                                                                                                                                                                                                                                                                                                                                |

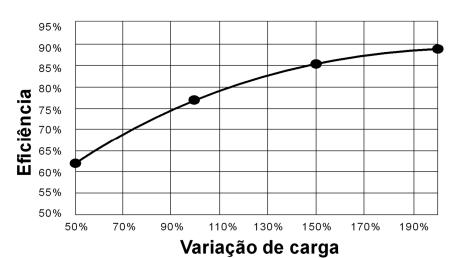

| Figura 4.25 - Variação de eficiência de acordo com a variação de carga através de resultados experimentais                                                                                                                                                                                                                                                                                                                                                                                     |

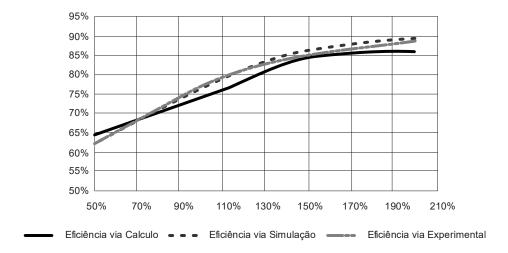

| Figura 4.26 - Comparativo de eficiência via LTspice© e via resultados experimentais                                                                                                                                                                                                                                                                                                                                                                                                            |

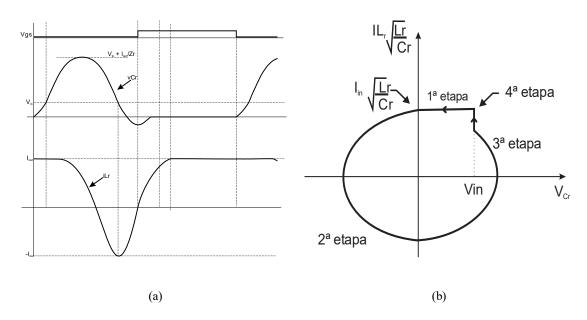

| Figura 5.2 - Etapa 1 e 2 da operação de um buck quase-ressonante                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figura 5.3 - Etapa 3 e 4 de operação de um buck quase-ressonante                                                                                                                                                                                                                                                                                                                                                                                                                               |

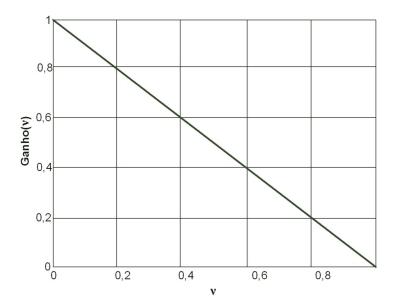

| Figura 5.4 - Comportamento conversor buck quase ressonante: (a) Formas de onda; (b) Plano de fase                                                                                                                                                                                                                                                                                                                                                                                              |

| Figura 5.5 - Ábaco ganho <i>buck</i> quase ressonante de acordo com a relação de frequência de comutação e ressonante                                                                                                                                                                                                                                                                                                                                                                          |

| Figura 5.6 - Ábaco do ganho de tensão admitindo limitação da capacitância intrínseca 82                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figura 5.7 - Distribuição de perdas por análise de cálculo conversor buck síncrono ZVS 84                                                                                                                                                                                                                                                                                                                                                                                                      |

| Figura 5.8 - Esquemático do conversor <i>buck</i> quase ressonante no LTspice©                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figura 5.9 - Tensão e corrente de entrada conversor <i>buck</i> síncrono quase ressonante                                                                                                                                                                                                                                                                                                                                                                                                      |

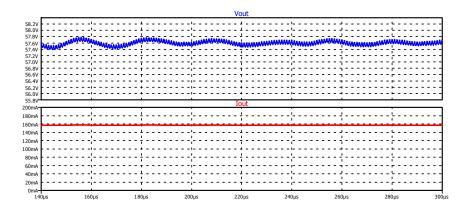

| Figura 5.10 - Tensão e corrente de saída do <i>buck</i> síncrono quase ressonante, simulação LTSPICE©                                                                                                                                                                                                                                                                                                                                                                                          |

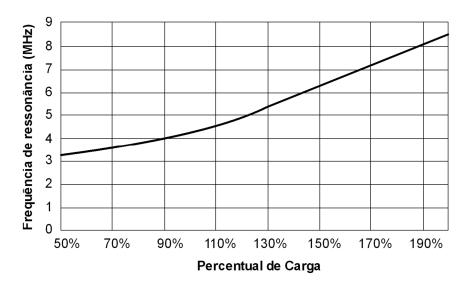

| Figura 5.11 - Variação de frequência de ressonância de acordo com a carga de saída 88                                                                                                                                                                                                                                                                                                                                                                                                          |

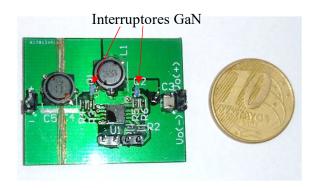

| Figura 5.12 - Placa de circuito impresso desenvolvida para conversor buck síncrono quase                                                                                                                                                                                                                                                                                                                                                                                                       |

| ressonante 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

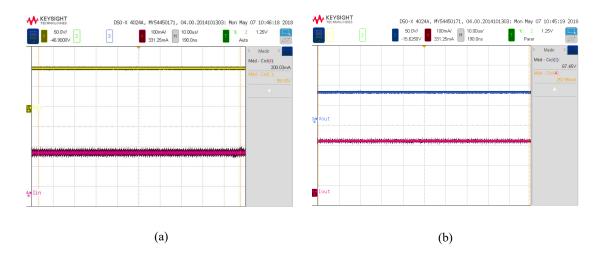

| Figura 5.13 - Resultados experimentais carga nominal buck quase ressonante, tensão e corrente: |

|------------------------------------------------------------------------------------------------|

| (a)Entrada e (b)Saída. Canal 1 - Tensão de entrada (50 V/div); Canal 3 - Tensão de saída (100  |

| V/div). Escala horizontal 500 ns/div90                                                         |

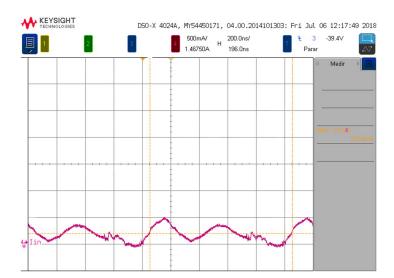

| Figura 5.14 - Corrente Ressonante buck quase-ressonante. Canal 4 (500 mA/div). Escala          |

| horizontal 200 ns/div91                                                                        |

| Figura 5.15 - Tensão sobre interruptores buck quase ressonante. Canal 2 - Tensão sobre         |

| interruptor Q2 (50 V/div); Canal 3 - Tensão de sobre do interruptor Q1 (50 V/div). Escala      |

| horizontal 200 ns/div91                                                                        |

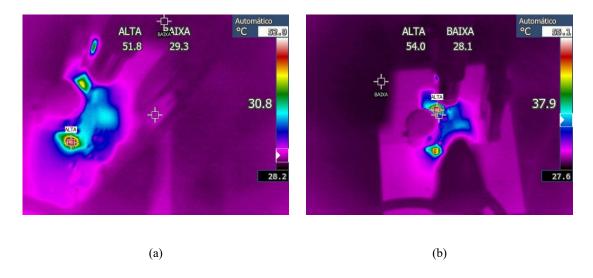

| Figura 5.16 - Temperatura interruptores buck quase ressonante:(a) Interruptor superior; (b)    |

| Interruptor Inferior 92                                                                        |

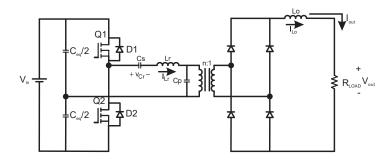

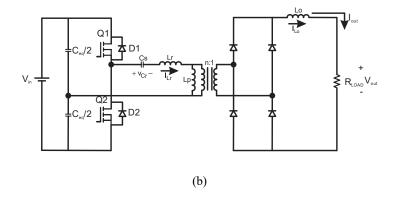

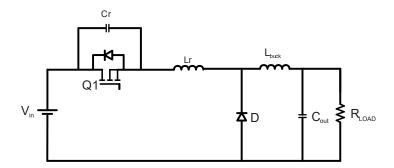

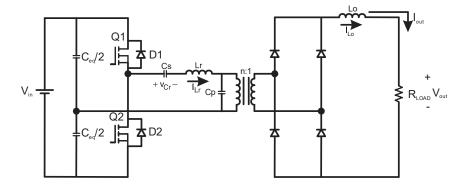

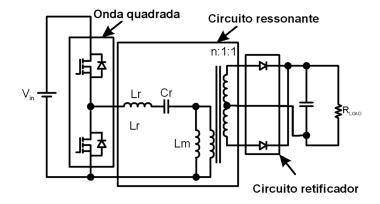

| Figura 6.1 - Conversor LLC93                                                                   |

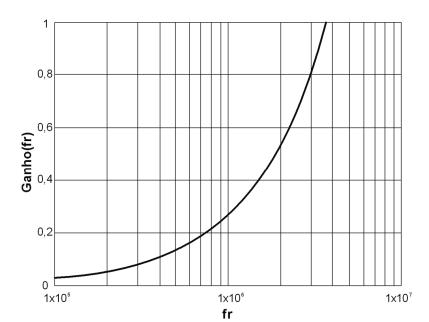

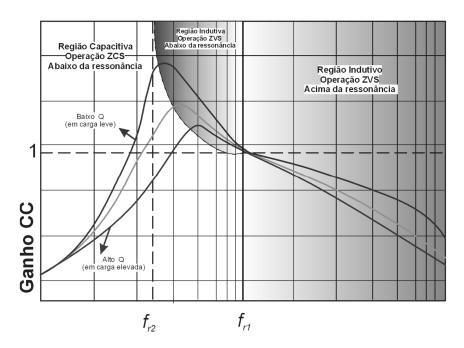

| Figura 6.2 - Ganho conversor LCC                                                               |

| Figura 6.3 - Comparativo configuração série paralelo: (a) LCC e (b)LLC                         |

| Figura 6.4 - Conversor Ressonante LLC half-bridge com retificador meia onda conectado à        |

| carga                                                                                          |

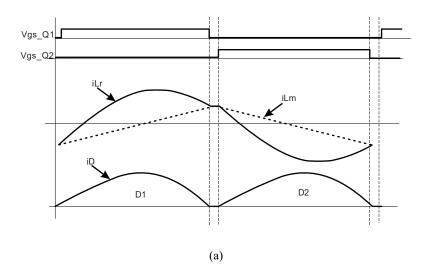

| Figura 6.5 - Operação conversor LLC: (a)fs = fr1, (b)fs < fr1 e (c)fs > fr1                    |

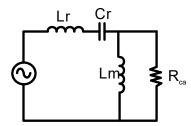

| Figura 6.6 - Conversor ressonante tipo LLC através do método FHA                               |

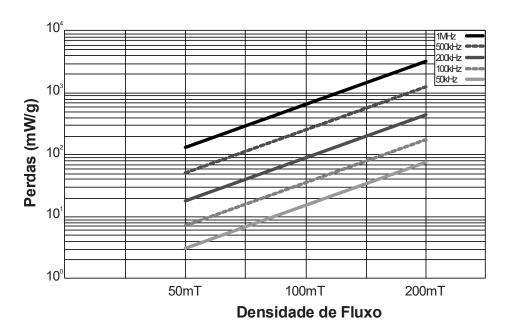

| Figura 6.7 - Perdas Núcleo de acordo com a frequência de operação                              |

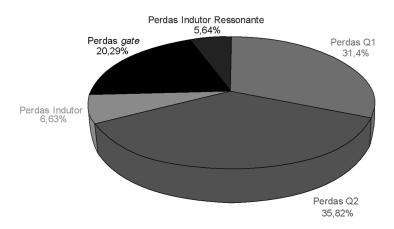

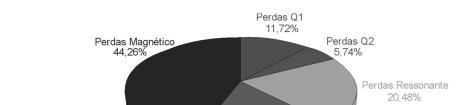

| Figura 6.8 - Divisão das perdas conversor ressonante LLC                                       |

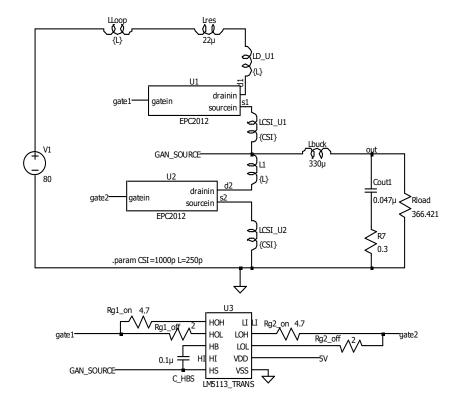

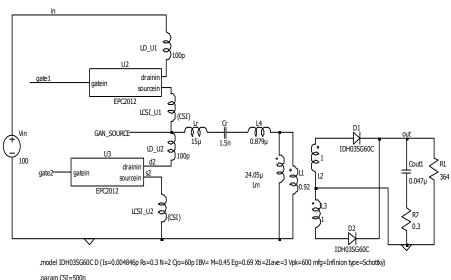

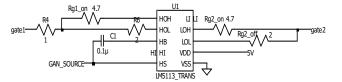

| Figura 6.9 - Esquemático para simulação conversor LLC, LTspice©                                |

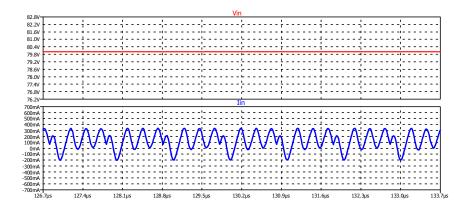

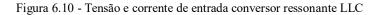

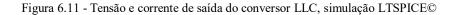

| Figura 6.10 - Tensão e corrente de entrada conversor ressonante LLC                            |

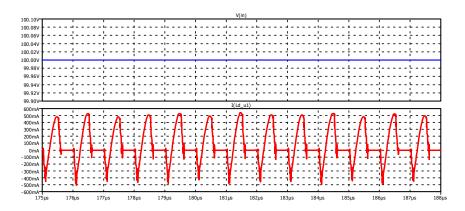

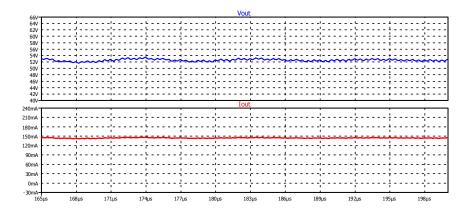

| Figura 6.11 - Tensão e corrente de saída do conversor LLC, simulação LTSPICE© 108              |

| Figura 6.12 - Verificação ZVS via simulação LTspice©                                           |

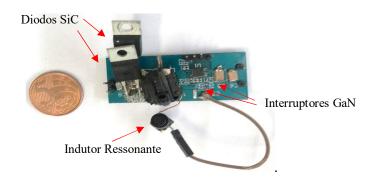

| Figura 6.13 - Placa circuito impresso conversor LLC                                            |

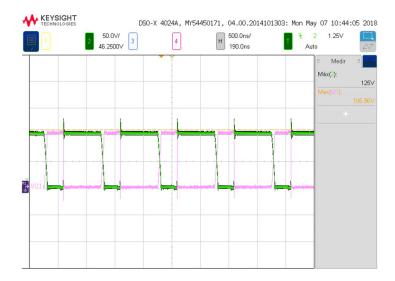

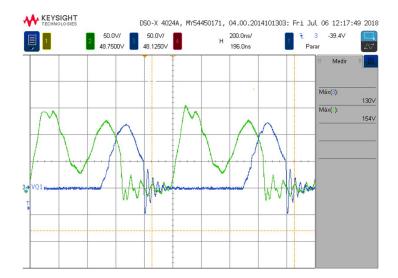

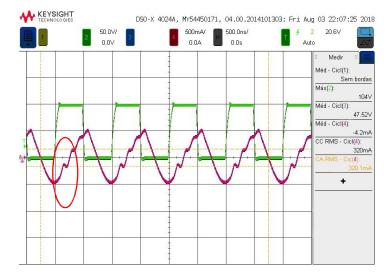

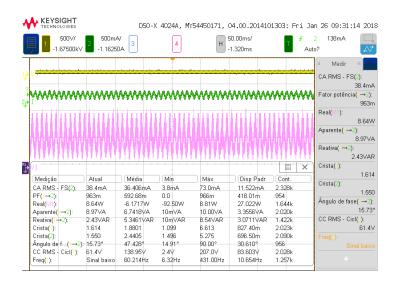

| Figura 6.14 - Tensão sobre o interruptor Q2 e corrente ressonante do conversor LLC. Canal 2 -  |

| Tensão sobre interruptor Q2 (50 V/div); Canal 4 - Correntes ressonante (500 mA/div). Escala    |

| horizontal 500 ns/div                                                                          |

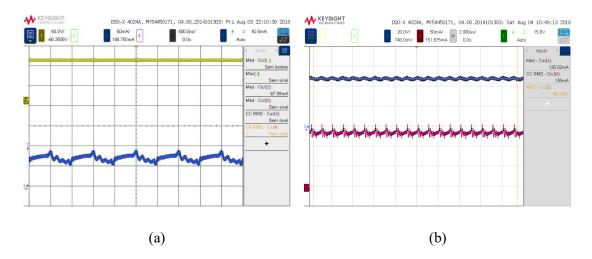

| Figura 6.15 - Resultados experimentais carga nominal LLC, tensão e corrente: (a)Entrada e      |

| (b)Saída. Canal 1 - Tensão de entrada (50 V/div); Canal 3: (a) Correntes de entrada (500       |

| mA/div) e (b) Tensão de saída (20 V/div); Canal 4 - Corrente de saída (50 mA/div). Escala      |

| horizontal: (a) 500 ns/div e (b)2 µs/div                                                       |

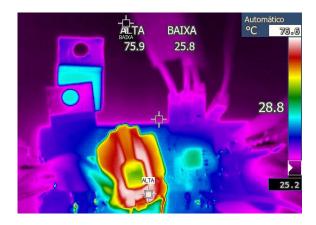

| Figura 6.16 - Temperatura conversor LLC                                                        |

#### LISTA DE TABELAS

| Tabela 2.1 - Propriedades dos materiais: Si, GaN e SiC                                     | 27    |

|--------------------------------------------------------------------------------------------|-------|

| Tabela 4.1 - Especificações para projeto do conversor <i>buck</i> síncrono                 | 52    |

| Tabela 4.2 - Componentes comerciais para <i>buck</i> síncrono                              |       |

| Tabela 4.3 - Dados transistores GaN utilizado                                              | 54    |

| Tabela 4.4 - Dados do circuito integrado utilizado para o acionamento dos dispositivos     | GaN   |

| LM5113                                                                                     |       |

| Tabela 4.5 - Resultados de perda por carga através de cálculo de perdas                    | 57    |

| Tabela 4.6-Valores médios de Entrada buck síncrono                                         |       |

| Tabela 4.7 - Valores médios de Saída <i>buck</i> síncrono                                  |       |

| Tabela 4.8 - Dissipação de potência por elementos no buck síncrono, via simulação          | 61    |

| Tabela 4.9 - Alterações de projeto para variação de carga                                  |       |

| Tabela 4.10 - Resultados de simulação de acordo com a variação de carga, via LTSPice ©     | 63    |

| Tabela 4.11 - Resultados experimentais médios para carga 50%                               |       |

| Tabela 4.12 - Resultados experimentais médios para carga de 100%                           |       |

| Tabela 4.13 - Resultados experimentais médios para carga 150%                              | 69    |

| Tabela 4.14 - Resultados experimentais médios para carga de 200%                           | 71    |

| Tabela 4.15 - Análise das perdas experimentais de acordo com a carga                       |       |

| Tabela 4.16 - Comparativo de perdas de acordo com cálculo, simulação e verific             | ação  |

| experimental                                                                               | 74    |

| Tabela 5.1 - Parâmetros de projeto conversor <i>buck</i> quase ressonante                  | 81    |

| Tabela 5.2 - Projeto <i>buck</i> quase ressonante – primeira versão                        | 81    |

| Tabela 5.3 - Projeto <i>buck</i> quase ressonante – segunda versão                         |       |

| Tabela 5.4 - Parâmetros de projeto conversor buck quase ressonante com alteração           |       |

| Tabela 5.5 - Projeto buck quase ressonante com alteração dos parâmetros de entrada         | 83    |

| Tabela 5.6 - Valores médios de Entrada buck síncrono quase ressonante                      | 86    |

| Tabela 5.7 - Valores médios de Saída buck síncrono quase ressonante, via simulação         | 86    |

| Tabela 5.8 - Dissipação de potência por elementos no buck síncrono quase ressonante        | , via |

| simulação                                                                                  | 87    |

| Tabela 5.9 - Alterações de projeto para variação de carga – <i>buck</i> quase ressonante   | 87    |

| Tabela 5.10 - Resultados de simulação de acordo com a variação de carga buck o             | ıuase |

| ressonante, via LTSPice ©                                                                  | 89    |

| Tabela 5.11 - Resultados experimentais médios para carga buck quase ressonante             |       |

| Tabela 6.1 - Parâmetros de projeto do conversor LLC                                        | . 101 |

| Tabela 6.2 - Resultado de projeto para conversor ressonante do tipo LLC                    | . 102 |

| Tabela 6.3 - Valores médios de Entrada do conversor LLC, via simulação                     | . 107 |

| Tabela 6.4 - Valores médios de Saída do conversor LLC, via simulação                       |       |

| Tabela 6.5 - Dissipação de potência por elementos no conversor LLC                         | . 109 |

| Tabela 6.6 - Resultados experimentais médios para carga nominal conversor LLC              | . 111 |

| Tabela 7.1 - Comparativo perdas interruptores entre topologias para carga nominal, via cál | lculo |

|                                                                                            | . 113 |

| Tabela 7.2 - Comparativo perdas interruptores entre topologias para carga nominal,         | , via |

| simulação                                                                                  | . 114 |

| Tabela 7.3 - Comparativo perdas interruptores entre topologias para carga nom              | inal, |

| experimentalmente                                                                          |       |

### SUMÁRIO

| 1 CONTEXTUALIZAÇÃO E JUSTIFICATIVA                             | <b>2</b> 1 |

|----------------------------------------------------------------|------------|

| 1.1 CONTEXTUALIZAÇÃO DO TRABALHO                               | 2          |

| 1.2 DEFINIÇÃO DO PROBLEMA E OBJETIVOS DO TRABALHO              | 23         |

| 1.3 ORGANIZAÇÃO DO TRABALHO                                    | 24         |

| 2 TRANSISTORES DE NITRETO DE GÁLIO                             | 25         |

| 2.1 ESTRUTURA E FUNCIONAMENTO                                  | 25         |

| 2.2 CARACTERÍSTICAS ELÉTRICAS                                  | 20         |

| 2.2.1 Tensão de ruptura (V <sub>rup</sub> )                    | 28         |

| 2.2.2 Resistência de condução (R <sub>DSon</sub> )             | 28         |

| 2.2.3 Tensão de Threshold (V <sub>th</sub> )                   | 29         |

| 2.2.4 Condução reversa                                         | 30         |

| 2.3 TIPOS DE TRANSISTORES DE NITRETO DE GÁLIO                  |            |

| 2.3.1 Tipo depleção                                            | 31         |

| 2.3.2 Tipo intensificação                                      |            |

| 2.3.3 Tipo cascode                                             | 33         |

|                                                                |            |

| 3.1 TEORIA DOS CONVERSORES RESSONANTES                         |            |

| 3.1.1 Conversores Ressonantes Convencionais - Carga Ressonante | 38         |

| 3.1.1.1 Conversor Série Ressonante                             |            |

| 3.1.1.2 Conversor Paralelo Ressonante                          |            |

| 3.1.2 Conversores quase-ressonantes                            |            |

| 3.1.3 Comutação com Zero de Corrente (ZCS)                     |            |

| 3.1.4 Comutação com Zero de Tensão (ZVS)                       |            |

| 4 CONVERSOR BUCK OPERANDO EM COMUTAÇÃO FORÇADA                 | 49         |

| 4.1 FUNCIONAMENTO BUCK SÍNCRONO                                | 49         |

| 4.2 PROJETO DO CONVERSOR                                       | 5          |

| 4.3 ANÁLISE DE PERDAS ATRAVÉS DE CÁLCULO                       | 52         |

| 4.3.1 Análise de resultados de perdas através de cálculos      | 50         |

| 4.4 ANÁLISE DE PERDAS ATRAVÉS DE SIMULAÇÃO                     | 58         |

| 4.4.1 Simulação LTSpice© com modelo completo                   | 58         |

| 4.4.2 Análise de perdas em relação à carga de saída            | 62         |

| 4.5 RESULTADOS EXPERIMENTAIS BUCK SINCRONO                     | 63         |

| 4.5.1 Análise da eficiência de acordo com a carga              |            |

| 4.5.1.1 Resultados experimentais para 50% de carga             |            |

| 4.5.1.2 Resultados experimentais para 100 % de carga                                                                                                                            | 67  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.5.1.3 Resultados experimentais para 150 % de carga                                                                                                                            |     |

| 4.5.1.4 Resultados experimentais para 200 % de carga                                                                                                                            |     |

| 4.5.2 Análise dos resultados experimentais                                                                                                                                      | 73  |

| 4.6 COMPARAÇÃO ENTRE CÁLCULO, SIMULAÇÃO E RESULTADO                                                                                                                             |     |

| EXPERIMENTAL                                                                                                                                                                    |     |

| -                                                                                                                                                                               |     |

| 5.1 O BUCK QUASE RESSONANTE                                                                                                                                                     |     |

| 5.2 ETAPAS DE OPERAÇÃO                                                                                                                                                          |     |

| 5.3 PROJETO BUCK QUASE RESSONANTE                                                                                                                                               | 79  |

| 5.4 ANÁLISE VIA CÁLCULO                                                                                                                                                         | 84  |

| 5.5 ANÁLISE VIA SIMULAÇÃO                                                                                                                                                       | 85  |

| 5.5.1 Análise de perdas em relação a carga de saída                                                                                                                             | 87  |

| 5.6 RESULTADOS EXPERIMENTAIS BUCK QUASE-RESSONANTE                                                                                                                              | 89  |

| 6 CONVERSOR RESSONANTE TIPO LLC                                                                                                                                                 | 93  |

| 6.1 CONVERSOR RESSONANTE LLC                                                                                                                                                    | 93  |

| 6.2 FUNCIONAMENTO DO CONVERSOR RESSONANTE TIPO LLC                                                                                                                              |     |

| 6.2.1 Frequência de comutação igual à frequência ressonante série $(f_s = f_{r1})$                                                                                              |     |

| 6.2.2 Frequência de comutação inferior à frequência ressonante série ( $f_s < f_{r1}$ ) 6.2.3 Frequência de comutação superior à frequência ressonante série ( $f_s > f_{r1}$ ) |     |

| 6.3 PROJETO CONVERSOR RESSONANTE TIPO LLC                                                                                                                                       |     |

| 6.4 ANÁLISE VIA CÁLCULO                                                                                                                                                         |     |

| 6.5 ANÁLISE VIA SIMULAÇÃO DO CONVERSOR LLC                                                                                                                                      |     |

| 6.6 ANÁLISE EXPERIMENTAL CONVERSOR LLC                                                                                                                                          |     |

| 7 COMPARATIVO DE TOPOLOGIAS                                                                                                                                                     |     |

| 7.1 COMPARATIVO VIA CÁLCULO                                                                                                                                                     | 113 |

| 7.2 COMPARATIVO VIA SIMULAÇÃO                                                                                                                                                   | 114 |

| 7.3 COMPARATIVO EXPERIMENTAL                                                                                                                                                    | 114 |

| CONSIDERAÇÕES FINAIS                                                                                                                                                            | 117 |

| REFERÊNCIAS                                                                                                                                                                     | 119 |

| APÊNDICE A - ANÁLISE lampada led comercial                                                                                                                                      | 125 |

|                                                                                                                                                                                 |     |

#### 1 CONTEXTUALIZAÇÃO E JUSTIFICATIVA

Esse capítulo visa contextualizar a evolução da eletrônica de potência, observando o progressivo aumento da frequência de comutação utilizada pelos sistemas. bem como apresentar os objetivos do presente trabalho e suas justificativas, os resultados esperados e a estrutura da dissertação.

#### 1.1 CONTEXTUALIZAÇÃO DO TRABALHO

A evolução em eletrônica de potência está muito atrelada ao avanço tecnológico dos semicondutores. O tiristor foi o dispositivo semicondutor precursor da eletrônica de potência, proposto por William Shockley, em 1950, e desenvolvido em 1956 pelos engenheiros da empresa General Electric (G.E), liderados por Gordon Hall (ARSOV; MIRČEVSKI, 2010). Os primeiros tiristores eram produzidos utilizando germânio, sendo que a substituição desse por silício foi alvo de pesquisas durante a década de 50 (TEXAS INSTRUMENTS, 2018a). Tal mudança ocorreu pelo fato de que as propriedades do silício são superiores às do germânio, o que limitava as capacidades de bloqueio de tensão e as correntes de condução do tiristor.

Com o tiristor tornou-se possível a produção de circuitos em larga escala em eletrônica de potência. Desta forma, iniciou-se a busca pela evolução dos dispositivos semicondutores, a qual levou aos transistores de efeito de campo de semicondutor de óxido metálico (MOSFET, do inglês *Metal-Oxide Semiconductor Field-Effect Transistor*), que alcançaram altos ganhos de corrente em meados da década de 70 (LIDOW; HERMAN; COLLINS, 1979). Após esse, no início dos anos 80, surgiram os transistores bipolares de porta isolada (IGBT, do inglês *Insulated Gate Bipolar Transistor*), que possuem menores resistências de condução quando comparados aos MOSFETs (BALIGA; ADLER; *et al.*, 1984).

Desde do surgimento do MOSFET, este tem sua tecnologia aprimorada, embora ainda apresente problemas de eficiência ao operar em altas frequências. As perdas de entrada e saída de condução do MOSFET aumentam de acordo com o aumento da frequência de comutação empregada no circuito, assim limitando o aumento de frequência comutação do MOSFET. É importante observar que conversores em alta frequência possuem como vantagem a miniaturização, a integração e a melhoria de performance, além da diminuição do volume dos

componentes passivos devido ao fato de a energia ser inversamente proporcional à frequência (MASSACHUSETTS INSTITUTE OF TECHNOLOGY, 2014), o que não seria possível se os MOSFETs continuassem sendo utilizados nesse tipo de conversores.

Essa necessidade de miniaturização dos sistemas passou a ser ainda mais almejada após a integração dos sistemas nos chamados circuitos integrados, ideia iniciada nos anos 70, com o avanço dos semicondutores (TEXAS INSTRUMENTS, 2018a). A evolução desejada dos sistemas ocorreu visando empregar os mesmos nos mais diversos segmentos, motivo pelo qual eles vinham sendo objeto prévio de estudo de alguns pesquisadores, os quais já antecipavam as necessidades futuras do mercado (HOFT, 1993).

Com as vantagens da elevação da frequência e a permanente limitação do MOSFET para esse tipo de operação, deu-se início à utilização de conversores em comutação suave e ao emprego de topologias ressonantes (KAZIMIERCZUK; CZARKOWSKI, 2011). Os conversores ressonantes possuem como vantagem a possibilidade de operação em alta frequência, devido a diminuição de perdas por comutação e também a diminuição da interferência eletromagnética (*EMI*, do inglês *Electromagnetic interference*), sendo esses possíveis através de um projeto eficiente. Além disso, os conversores de característica ressonante possuem como principais características a operação em corrente zero durante a saída de condução e a operação em tensão zero na entrada em condução do interruptor, respectivamente, ZCS (*Zero-Current Switching*) e ZVS (*Zero-Voltage Switching*).

Desta forma, com a utilização de conversores com MOSFETs em conjunto às técnicas de comutação suave, ou seja, ZVS e ZCS, é possível o desenvolvimento de sistemas com maiores densidades de potência, sendo que este o conceito está relacionado à capacidade de processamento de energia por volume do conversor.

A partir do ano de 2004 (LIDOW; STRYDOM; *et al.*, 2015), houve a introdução dos semicondutores de nitreto de Gálio (GaN), que surgiram como uma nova alternativa para eletrônica de potência em operações em alta frequência e para sistemas de maiores densidades de potência. Tal comportamento ocorre por menores perdas na entrada e na saída da comutação, assim como pelas menores resistências de condução e maior compactação do conversor em relação aos que utilizam MOSFETs de potência.

O GaN também surge como uma alternativa para unir duas necessidades do mercado: altas eficiências e miniaturização dos sistemas, visto que o mesmo permite o aumento de frequência de comutação e consequente diminuição do tamanho dos componentes passivos do sistema (CHEASTY; FLANNERY; et al., 2002). Desta forma, sistemas eficientes, compactos e de alta potência são cada vez mais desejados, aumentando a busca por sistemas com alta

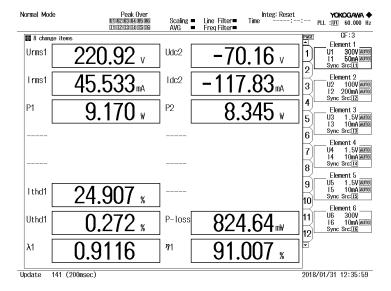

densidade de potência. Na Figura 1.1 é apresentada relação de potência e frequência para os principais dispositivos semicondutores utilizados em eletrônica de potência para cada faixa de potência e frequência.

Figura 1.1 - Evolução de potência e frequência de acordo com os dispositivos semicondutores

Fonte: (QUINN; DALAL, 2017)

Como pode ser observado na Figura 1.1 os dispositivos GaN passam a ser vantajosos em aplicações em baixa potência e para frequências superiores a algumas centenas de quilohertz. Em (DUARTE, 2017) é realizado o comparativo entre circuitos utilizando dispositivos Si e GaN, sendo esses operados em frequência de 100 kHz a 1 MHz. Onde para operações em 1 MHz é identificado o aumento de eficiência para os circuitos utilizando os semicondutores GaN, (DUARTE, 2017).

#### 1.2 DEFINIÇÃO DO PROBLEMA E OBJETIVOS DO TRABALHO

A busca por aumento da eficiência é um assunto constante nas pesquisas, uma vez que cada vez mais a tecnologia, e consequentemente a energia elétrica, está presente na vida das pessoas. Cerca de 30% da energia elétrica é consumida em eletrônica de potência, sendo estimado que, no ano de 2030, esse percentual chegará a 80% (U.S DEPARTMENT OF

ENERGY, 2011). Desta forma, a otimização de sistemas em eletrônica de potência é uma busca constante.

Por isso, este trabalho busca o estudo de eficiência para conversores utilizando GaN. Desde do seu surgimento em 2004, o GaN tornou-se uma alternativa para sistemas em alta frequência (> 800 kHz), dos quais a grande maioria até então utilizava *snubbers*, circuitos de amortecimento de picos de tensão e corrente a partir de métodos para comutação suave e conversores ressonantes (AYYANAR; MOHAN; PERSSON, 2002).

Neste trabalho são propostas três topologias utilizando semicondutores GaN, sendo empregada para duas dessas topologias circuitos ressonantes, assim adicionando aos circuitos as vantagens das topologias ressonantes para operações em 1MHz. O aumento de eficiência é esperado para os circuitos a que foram adicionadas características ressonantes.

#### 1.3 ORGANIZAÇÃO DO TRABALHO

O presente trabalho é organizado em 7 capítulos, sendo este o primeiro. O segundo capítulo terá como foco os semicondutores do tipo Nitreto de Gálio (GaN) e suas principais características. No Capítulo 3 apresentará os conversores ressonantes e suas principais topologias. O Capítulo 4 será voltado ao estudo da topologia do conversor *buck* síncrono, sendo abordados os aspectos de projeto, análise de perdas por cálculo, simulação e resultados experimentais a respeito do mesmo. Nos Capítulos 5 e 6, tratarão sobre as topologias ressonantes empregadas, juntamente com os semicondutores do tipo GaN. O Capítulo 7 e último será destinado ao comparativo de perdas entres as topologias propostas.

#### 2 TRANSISTORES DE NITRETO DE GÁLIO

Neste capítulo serão apresentados: o princípio básico de funcionamento e os semicondutores fundamentais de nitreto de gálio, assim como aspectos construtivos e características desses.

#### 2.1 ESTRUTURA E FUNCIONAMENTO

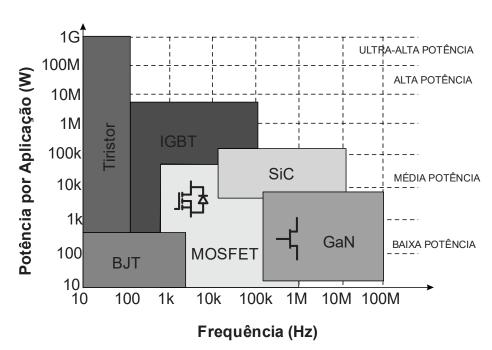

O nitreto de gálio (GaN) é um composto cristalino hexagonal que possui uma estrutura denominada wurtzite, mostrada na Figura 2.1. Essa estrutura é caracterizada por sua estabilidade e robustez mecânica, o que confere ao GaN a capacidade de operar em altas temperaturas sem se decompor. Tal cristalino também confere ao nitreto de gálio propriedades piezoelétricas que possibilitam alta condutividade, se comparado aos demais materiais semicondutores. As características piezoelétricas ocorrem devido ao deslocamento de elementos eletricamente carregados na rede cristalina sob tensão, de tal forma que a rede cristalina se deforma, de maneira que os átomos se desviam dessa rede, gerando um campo elétrico proporcional à deformação (LIDOW; STRYDOM; et al., 2015).

Figura 2.1 - Estrutura do tipo wurtzite do GaN

Fonte: (LIDOW; STRYDOM; et al., 2015)

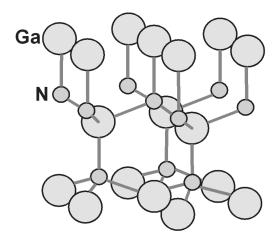

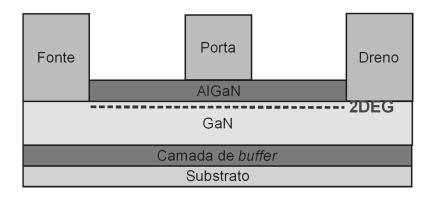

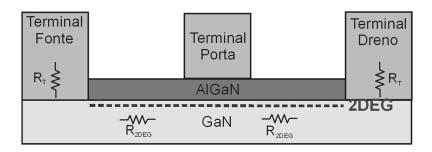

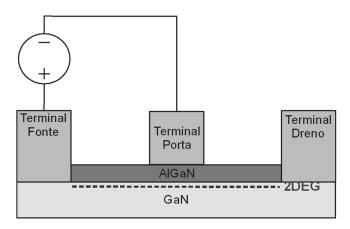

O dispositivo de nitreto de gálio pode ser também caracterizado como GaN *HEMT*, devido a sua característica de alta mobilidade de elétrons (*HEMT*, do inglês *High Electron*

Mobility Transistor). Na Figura 2.2, observa-se uma estrutura básica do GaN HEMT, por meio da qual se percebe que a estrutura do GaN é dividida basicamente em quatro camadas, sendo as de GaN e de alumínio-nitreto de gálio (AlGaN) responsáveis pela característica de alta mobilidade de elétrons, (EPC, 2011). Entre essas duas camadas é induzida uma nuvem de elétrons bidimensional (2DEG, do inglês Two-Dimensional Electron Gas), resultado de uma concentração de elétrons gerada devido às características piezoelétricas do GaN (EPC, 2017).

Figura 2.2 - Estrutura do transistor de potência GaN HEMT

Fonte: (DUARTE, 2017)

A característica *2DEG* torna inerente ao dispositivo GaN uma alta condutividade, desse modo elevando a eficiência de qualquer conversor do qual faça parte (EPC, 2017).

#### 2.2 CARACTERÍSTICAS ELÉTRICAS

Antes de abordar as características elétricas do GaN, é necessário analisar as características gerais dos semicondutores, que interferem diretamente nas características elétricas do GaN. Entre essas a serem consideradas, estão o Bandgap e o  $E_{crit}$  (campo elétrico critico).

O *Bandgap* relaciona-se à força das ligações químicas entre os átomos da estrutura: quanto mais forte essa ligação, maior é a dificuldade de o elétron mudar de um local para outro, gerando menores correntes parasitas e permitindo a operação em maiores temperaturas, (SZE; NG, 2007) e (LUTZ; SCHLANGENOTTO; *et al.*, 2011).

Semicondutores de potência devem possuir alto *bandgap*, de modo a garantir que a concentração de portadores presente na região não dopada seja inferior à da região dopada na

temperatura de operação. Um alto bandgap é vantajoso se relacionado ao campo elétrico critico  $(E_{crit})$ , visto que, para maiores bandgaps, maior é o campo elétrico que o material pode suportar sem haver dano (LUTZ; SCHLANGENOTTO;  $et\ al.$ , 2011).

O E<sub>crit</sub> é o máximo campo elétrico ao qual o material pode ser submetido sem que o processo de avalanche inicie e, dessa maneira, ocorra a destruição da estrutura cristalina. Quando comparado ao Silício (Si) e ao Carbeto de Silício (SiC), o GaN com essa forma ganha determinada vantagem, como pode ser visto na Tabela 2.1.

Tabela 2.1 - Propriedades dos materiais: Si, GaN e SiC

| Parâmetro              | Unidade              | Si   | GaN  | SiC  |

|------------------------|----------------------|------|------|------|

| Bandgap                | eV                   | 1,12 | 3,9  | 3,26 |

| Campo crítico          | MV/cm                | 0,23 | 3,3  | 2,2  |

| Mobilidade de elétrons | cm <sup>2</sup> /V.s | 1400 | 1500 | 950  |

| Permissividade         |                      | 11.8 | 9    | 9.7  |

| Condutividade Térmica  | W/cm.K               | 1.5  | 1.3  | 3.8  |

Fonte: (LIDOW; STRYDOM; et al., 2015).

Como observado na Tabela 2.1, o GaN possui valores superiores em *Bandgap*, campo crítico e mobilidade de elétrons, tais fatores são determinantes para o bom desempenho deste tipo de semicondutor principalmente quando operado em altas frequências.

Os dispositivos semicondutores de potência possuem características indispensáveis para o projeto do conversor, visto que essas, tais como tensão de ruptura ( $V_{rup}$ ), resistência em condução entre dreno e fonte do interruptor ( $R_{DSon}$ ) e tensão de Threshold ( $V_{th}$ ), influenciam diretamente no funcionamento do circuito, (DUSMEZ; COOK; KHALIGH, 2011). Além disso, essas características verificam o comportamento do interruptor GaN quando condução reversa. Pelo fato de o interruptor GaN operar em altas frequências, na maioria dos casos, é necessário conhecer as características das capacitâncias intrínsecas do mesmo.

#### 2.2.1 Tensão de ruptura ( $V_{rup}$ )

A tensão de ruptura,  $V_{rup}$ , consiste na tensão entre os terminais de dreno e fonte, sendo levados em conta diversos fatores (LIDOW; STRYDOM; *et al.*, 2015), tais como o  $E_{crit}$  do GaN, a estrutura do dispositivo, a heteroestrutura, as camadas isolantes internas ao GaN e as características do substrato. A tensão em que ocorre a ruptura corresponde a aproximadamente, (5.1).

$$V_{rup} = \frac{1}{2} \cdot w_{drift} \cdot E_{crit} \tag{5.1}$$

Onde *w<sub>drift</sub>* é a largura da região de deriva (*drift*).

Assim, a partir de (5.1), pode-se verificar que, devido à proporcionalidade com o  $E_{crit}$ , o aumento demasiado do campo elétrico interno do dispositivo leva à ruptura. Quando a tensão de ruptura  $V_{rup}$  é atingida, na maioria dos casos ocorre a destruição do dispositivo ou até a deterioração do mesmo devido à ruptura física da camada isolante., entretanto, caso isso não ocorra, o dispositivo passará a conduzir corrente mesmo quando não acionado para tal estado.

#### 2.2.2 Resistência de condução ( $R_{DSon}$ )

A resistência de condução  $R_{DSon}$  do dispositivo está relacionada ao somatório de todas as resistências intrínsecas do dispositivo, levando-se em consideração, no valor final, as resistências parasitas criadas pelo caminho que conecta as fontes de entrada e os terminais do dispositivo, conforme pode ser observado na Figura 2.3.

Figura 2.3 - Componentes intrínsecos da resistência de condução do GaN

Fonte: (LIDOW; STRYDOM; et al., 2015)

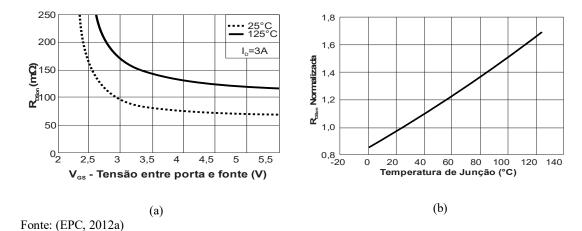

Devido ao fato de  $R_{DSon}$  ser composta pelos componentes intrínsecos do dispositivo, assim modificada de acordo com a temperatura, como destacado na Figura 2.4.

Figura 2.4 - Resistência de condução de acordo com a temperatura: (a)  $R_{DSon}$  em relação a tensão entre porta e fonte ( $V_{GS}$ ) e (b)  $R_{DSon}$  normalizada

#### 2.2.3 Tensão de Threshold ( $V_{th}$ )

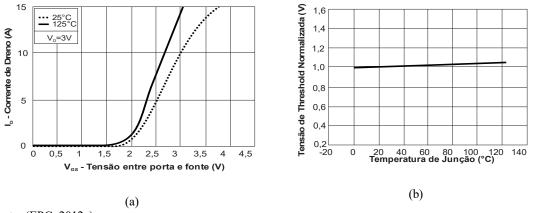

A tensão de *threshold* é o ponto de tensão entre porta e fonte,  $V_{GS}$ , em que o dispositivo entra em condução, ou seja, quando  $V_{GS}$  é inferior à  $V_{th}$ , o interruptor está aberto. A entrada em condução pode ser observada na Figura 2.5(a). Assim como as demais características internas do GaN, a  $V_{th}$  também sofre interferência da temperatura, como é visto na Figura 2.5(b).

Figura 2.5 - Tensão de threshold: (a) Característica de entrada em condução; (b) Normalizada em função da temperatura

Fonte: (EPC, 2012a)

Os dispositivos de GaN podem ser fabricados em três estruturas diferentes, o que interfere no modo de aplicação da tensão  $V_{GS}$ . Essas estruturas dos dispositivos de GaN serão vistos em detalhe posteriormente. Dois desses tipos, o intensificação e o *cascode*, possuem a  $V_{th}$  positiva, enquanto o depleção tem  $V_{th}$  negativa.

#### 2.2.4 Condução reversa

O MOSFET possui, como característica intrínseca, um diodo anti-paralelo devido à junção *p-n*. Em virtude disso, uma tensão negativa entre dreno e fonte polariza o diodo, fazendo-o conduzir. No entanto o tempo de recuperação desse diodo é lento quando comparado de diodos do tipo *p* e tipo Schottky com o mesmo valor de tensão direta (LUTZ; SCHLANGENOTTO; *et al.*, 2011). Dessa forma, para MOSFETs é comumente utilizado um diodo externo para evitar a condução pelo diodo intrínseco.

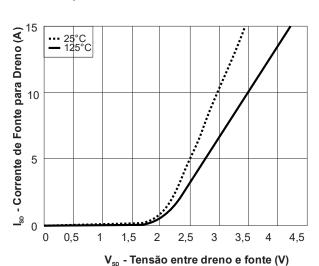

Assim, como os dispositivos GaN não possuem a junção p-n, a condução reversa opera de forma distinta, sendo essa possível somente para o tipo intensificação. Desta forma, o "diodo" reverso para os dispositivos GaN é formado pela ligação 2DEG em direção inversa, ocorrendo quando a tensão do dreno é superior, em pelo menos  $V_{th}$  na tensão de  $V_{GS}$  (LIDOW; STRYDOM;  $et\ al.$ , 2015). Na Figura 2.6, é apresentado o comportamento em condução reversa para os dispositivos GaN do tipo intensificação.

Figura 2.6 - Comportamento na condução reversa

Fonte: (EPC, 2012a)

Nos dispositivos GaN HEMT, os portadores minoritários não se deslocam na condução reversa, logo não há dissipação de energia na recuperação reversa. Para tais dispositivos, o  $Q_{rr}$  (carga de recuperação reversa) é zero, (LIDOW; STRYDOM; *et al.*, 2015), sendo essa uma vantagem perante os MOSFETs.

#### 2.3 TIPOS DE TRANSISTORES DE NITRETO DE GÁLIO

Como mencionado anteriormente, os dispositivos GaN podem ser divididos em três tipos, cada um com modo de operação distinto, além de necessitarem de controles diferenciados. Ressalta-se também que existem três configurações de GaN que podem ser utilizados em aplicações de eletrônica de potência: depleção, intensificação e *cascode*, sendo que os dois primeiros têm comportamento análogo aos tradicionais MOSFETs de silício (Si) do tipo P e do tipo N, respectivamente. Já o terceiro consiste em um dispositivo híbrido, em que são utilizados um semicondutor de Si e outro de GaN em um mesmo encapsulamento.

#### 2.3.1 Tipo depleção

Os transistores do tipo depleção, também denominados dGaN, são dispositivos de características normalmente fechadas. Assim, se não houver tensão aplicada sobre o terminal da porta (em inglês *gate*), a corrente fluirá entre os terminais de dreno e fonte.

O tipo depleção opera de forma a ser bloqueado quando é aplicada uma tensão negativa entre os terminais de porta e fonte, como pode ser observado na Figura 2.7. Esse fato ocorre, pois, o dGaN, quando em estado fechado, apresenta uma alta concentração de elétrons na camada 2DEG, de modo a facilitar a circulação de corrente. Porém, quando é aplicado um potencial negativo no terminal de porta, tal concentração é removida, bloqueando o dispositivo (LIDOW; STRYDOM; *et al.*, 2015).

Figura 2.7 - Transistor GaN Tipo depleção

Fonte: Adaptado de (FLACK; PUSHPAKARAN; BAYNE, 2016) e (LIDOW; STRYDOM; et al., 2015)

A simbologia usual de representação do tipo depleção é mostrada na Figura 2.8.

Figura 2.8 - Símbolo usual do interruptor GaN do tipo depleção (dGaN)

Em termos práticos, o GaN do tipo depleção não é muito utilizado em eletrônica de potência, pois requer, antes da aplicação de potência, um sinal negativo prévio no terminal de porta. Essa configuração de interruptor GaN é usualmente voltado para trabalhos acadêmicos, como em (ZHANG; RODRIGUEZ; MAKSIMOVIC', 2013) (RODRÍGUEZ; ZHANG; MAKSIMOVIĆ, 2014).

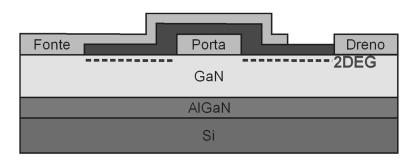

#### 2.3.2 Tipo intensificação

O tipo intensificação, ou eGaN, opera de forma similar aos MOSFETs do tipo N, ou seja, é normalmente aberto, não conduzindo corrente entre dreno e fonte se não houver tensão aplicada no terminal de porta (EPC, 2017).

Na Figura 2.9, é apresentada a estrutura do tipo intensificação, onde percebe-se que a camada 2DEG (linha pontilhada) não se estende entre os terminais de dreno e fonte. Por esse motivo, é preciso haver um potencial entre os terminais de porta e fonte, de forma que sejam atraídos elétrons para o primeiro, assim completando a camada 2DEG. Dessa maneira, é oferecido caminho para corrente entre dreno e fonte (EPC, 2017).

Figura 2.9 - Estrutura eGaN - Tipo Intensificação

Fonte: Adaptado de (EPC, 2017)

Por ser equivalente ao MOSFET do tipo N, é o mais utilizado entre as três configurações de GaN para aplicações de eletrônica de potência. Devido à essa similaridade do GaN intensificação com o MOSFET do tipo N, a mesma simbologia é utilizada para representar ambos, Figura 2.10.

Figura 2.10 - Símbolo usual do interruptor GaN do tipo intensificação, eGaN

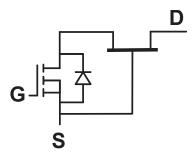

#### 2.3.3 Tipo cascode

O tipo *cascode*, ou cGaN, é uma configuração híbrida que utiliza um dispositivo GaN do tipo depleção conectado em série com um MOSFET de Si (Silício). Dessa forma, a tensão

entre os terminais de porta e dreno do MOSFET será aplicada entre os terminais de fonte e dreno do dGaN, sendo assim, o MOSFET controla a entrada e a saída de condução do dGaN (LIU, 2014). Ou seja, através desta configuração, é possível criar um semicondutor normalmente aberto. A simbologia utilizada para o cGaN é mostrada na Figura 2.11.

Figura 2.11 - Simbologia do GaN do tipo Cascode

Nessa configuração, conforme explicado anteriormente, utiliza-se um MOSFET Si e um dGaN em série, sendo que o primeiro possui baixa tensão (geralmente de, no máximo, 30V) e o segundo, alta tensão. Um dos parâmetros a serem analisados nesta configuração é a resistência de condução  $R_{DSon}$ . O MOSFET de baixa tensão possui  $R_{DSon}$  muito menor que a do dGaN de alta tensão, de forma que a resistência do dGaN tem comportamento dominante.

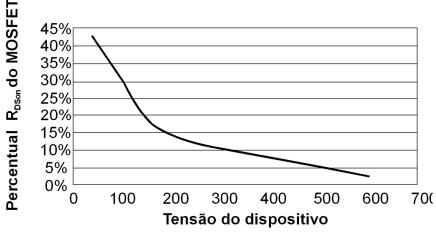

Na Figura 2.12, é apresentado o comportamento da resistência de condução  $R_{DSon}$  do cascode, onde se pode verificar que, conforme aumenta a tensão do dGaN, ocorre a diminuição de  $R_{DSon}$ .

Figura 2.12 - Participação do MOSFET de silício na resistência de condução do interruptor *cascode*

Fonte: (LIDOW; STRYDOM; et al., 2015)

Então, observando a Figura 2.12, percebe-se que quanto menor a tensão do dGaN, mais significante torna-se a resistência do MOSFET na resistência total do dispositivo, de forma que não se justifica o uso dessa topologia híbrida. Por fim, conclui-se que o uso de transistores do tipo *cascode* é viável para tensões de, no máximo, 200V (LIDOW; STRYDOM; *et al.*, 2015)

# 3 CONVERSORES RESSONANTES

Este capítulo apresenta a teoria sobre os conversores ressonantes, assim como suas principais características e classificações.

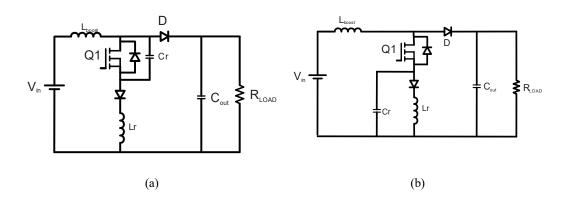

### 3.1 TEORIA DOS CONVERSORES RESSONANTES

Os conversores operando em modo de comutação forçada são os mais comumente utilizados em eletrônica de potência, empregando assim conversores com comutação por largura de pulso (*PWM – Pulse Width Modulation*), no entanto os transistores nesses tipos de conversores são ligados e desligados com tensão e corrente circulante, respectivamente. Esses comportamentos afetam a perda de potência durante a comutação, como indica a Figura 3.1 sendo que esse é um dos maiores impedimentos para o aumento da frequência de comutação (ANG; OLIVA, 2005).

Figura 3.1 - Curvas idealizadas para cálculo de perda em comutação (a) Turn-on (b) Tun-off

Fonte: (LIDOW; STRYDOM; et al., 2015)

Por essa limitação na comutação dos conversores PWM em comutação forçada, circuitos capazes permitir o aumento de frequência foram por muito tempo alvo de pesquisa. Assim surgindo os conversores ressonantes como solução. Os conversores ressonantes possuem diversas classificações, estando essas apresentadas na Figura 3.2.

Figura 3.2 - Classificação dos conversores ressonantes

Fonte: (RASHID, 2011)

A partir da Figura 3.2, é verificada a existência de três classes de conversores ressonantes: os conversores ressonantes convencionais, os quase-ressonantes e os multi-ressonantes, sendo que dentre esses três, são normalmente utilizados os conversores ressonantes convencionais e os quase-ressonantes. Os ressonantes convencionais mais usuais são os de carga ressonante, a qual podem apresentar configuração série, paralela e série-paralela.

Os quase-ressonantes são considerados técnicas de comutação suave (BELLAR; WU; et al., 1998), pois utilizam conversores estáticos do tipo *PWM* com a adição de um circuito LC, para alterar as formas de onda de corrente e tensão sobre o interruptor do sistema, resultando assim em uma característica de corrente zero durante a abertura (turn-off) ou tensão zero no fechamento (turn-on) do interruptor, denominadas ZCS e ZVS, respectivamente.

O ZCS é aplicado para reduzir as perdas de *turn-off* do sistema, enquanto o ZVS é utilizado para mitigar as perdas em *turn-on* do sistema. Geralmente os sistemas empregando ZVS são mais empregados em alta frequência (ANG; OLIVA, 2005).

### 3.1.1 Conversores Ressonantes Convencionais - Carga Ressonante

Os conversores com carga ressonante são caracterizados pela associação de indutores e capacitores, utilizados para suavizar corrente e tensão no interruptor durante a entrada e a saída de condução do interruptor. Esses apresentam perdas de *turn-off* nulas e ausência de estresse no interruptor, necessitando uma onda quadrada na entrada do sistema, de forma a atenuar os sinais de corrente e tensão da maneira mais senoidal possível, sendo que, para isso, são

utilizados conversores chaveados do tipo *half-bridge* (meia-ponte) e do tipo *full-bridge* (ponte completa).

Como citado anteriormente, o conversor ressonante convencional com carga do tipo ressonante possui três classificações internas, as quais serão descritas a seguir.

### 3.1.1.1 Conversor Série Ressonante

A topologia série ressonante, na Figura 3.3, é caracterizada pela carga conectada em série com o circuito ressonante, sendo a tensão de saída obtida a partir da corrente ressonante, o que constitui uma dependência da carga e também caracteriza esse como um conversor sensível às variações de carga. A sensibilidade é uma das principais desvantagens do conversor série ressonante, pois não há regulação de tensão de saída em baixa carga ou carga nula (KAZIMIERCZUK; CZARKOWSKI, 2011).

Figura 3.3 - Exemplo de topologia série ressonante.

Fonte: Adaptado de (RASHID, 2011)

Os conversores série ressonantes podem operar, basicamente, de três maneiras (MOHAN; UNDELAND; ROBBINS, 1995), sendo classificados de acordo com as mesmas, que são:

- Modo de condução descontinuo (fs ≤ 0.5fr);

- Modo de condução continuo (0.5fo<fs<fr) abaixo da ressonância;

- Modo de condução continuo (fs>fr) acima da ressonância.

Os modos de operação, segundo (DEPARTMENT OF ELECTRICAL, COMPUTER AND ENERGY ENGINEERING, 2014), são obtidos a partir dos intervalos e subintervalos de

operação do conversor. O modo descontínuo é caracterizado pelo fato de a corrente permanecer zero durante um determinado tempo. Dependendo da utilização do diodo anti-paralelo do interruptor (configuração de meia ponte e ponte completa), o modo descontínuo pode operar de dois modos.

O modo contínuo pode atuar de duas formas: em relação à frequência de comutação ser inferior ou em relação à mesma ser superior à frequência de ressonância. Sendo caracterizado pela continuidade da corrente no indutor durante toda a operação. De posse dessas informações, a corrente ora circula pelo interruptor (sentido positivo da corrente) ora pelo diodo anti-paralelo (sentido negativo da corrente). A diferença entre os modos de operação ocorre na frequência de operação (frequência de comutação) dos semicondutores.

### 3.1.1.2 Conversor Paralelo Ressonante

O conversor ressonante paralelo, Figura 3.4, é caracterizado por estar conectado diretamente à carga, podendo funcionar tanto quanto abaixador como elevador. Além dessas formas de operação, o conversor ressonante paralelo não possui problemas de sensibilidade de cargas.

Sem sensibilidade à carga, esse conversor é susceptível às baixas tensões e altas correntes na saída, tornando fácil a regulação da saída, visto que a tensão de saída depende da corrente circulante na carga. Mesmo operando em baixas tensões, os conversores acabam tendo a eficiência reduzida com a redução de carga, devido aos altos estresses causados pela corrente nos interruptores (KAZIMIERCZUK; CZARKOWSKI, 2011).

Figura 3.4 - Conversor Paralelo Ressonante

Fonte: (RASHID, 2011)

Da mesma forma que os série ressonantes, os conversores do tipo paralelo ressonante possuem três modos de operação, sendo o modo descontínuo caracterizado pela corrente no indutor e a tensão no capacitor estarem ambas zeradas por um determinado tempo. Em regime permanente, a corrente e a tensão inicialmente são consideradas nulas (MOHAN; UNDELAND; ROBBINS, 1995), de forma semelhante ao modo descontínuo para o conversor série ressonante. Durante esse modo, a tensão no capacitor e a corrente no indutor permanecem zeradas por tempo suficiente para que a tensão de saída seja controlada.

O modo contínuo, como analisado anteriormente, possui frequência de operação acima ou abaixo da de ressonância, com o mesmo princípio de operação para ambos: não há descontinuidade na corrente do indutor nem na tensão do capacitor. No entanto, para frequências de comutação superiores à frequência de ressonância, o diodo anti-paralelo do interruptor entra em operação antes do interruptor ligar, admitindo ZVS na entrada em condução; enquanto que, para frequência de comutação inferior à frequência de ressonância, o ZVS ocorre na saída de condução.

#### 3.1.1.3 Conversor Série-Paralelo Ressonante

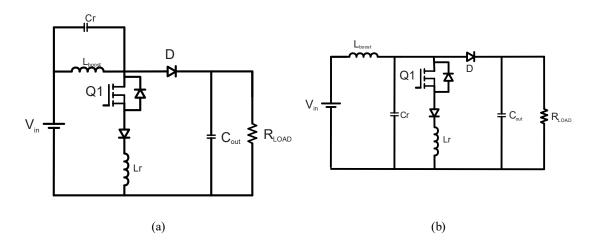

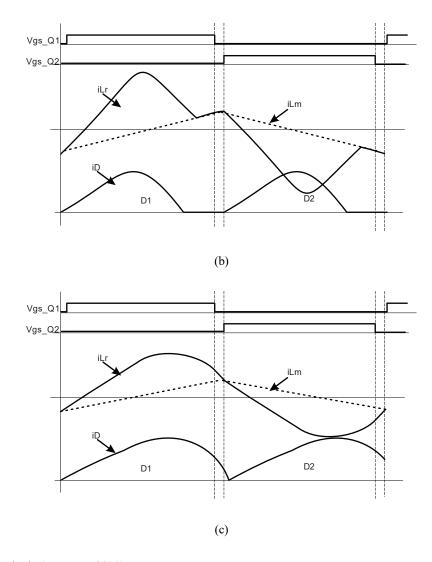

O Conversor Ressonante Série-Paralelo combina as vantagens dos dois conversores: série ressonante e paralelo ressonante, tendo como adicional um indutor ou um capacitor conectado em paralelo ao sistema ressonante. Na Figura 3.5, são mostradas duas combinações para um circuito, sendo que, além dessas, essa configuração permite diversos arranjos com o sistema ressonante.

Figura 3.5 - Tipos do Conversor Ressonante Série-Paralelo: (a) LCC e (b) LLC.

Fonte: (RASHID, 2011)

Este tipo de conversor é caracterizado pela boa regulação da tensão de saída, no entanto, quando opera em modo paralelo, a carga traz consigo o problema de eficiência conforme ocorre a redução de carga.

Para todas as configurações de circuito ressonante, são apresentadas as equações de (5.2) a (5.7), sendo que os parâmetros do conversor foram definidos através de: razão de tensão M, impedância característica  $Z_r$ , frequência de ressonância  $f_r$ , resistência de carga normalizada r e frequência normalizada  $\gamma$ .

$$M = \frac{n \cdot Vo}{Vi} \tag{5.2}$$

$$Z_r = \sqrt{\frac{L_r}{C_r}} \tag{5.3}$$

$$f_r = \frac{1}{2 \cdot \pi \cdot \sqrt{L_r \cdot C_r}} \tag{5.4}$$

$$r = \frac{n^2 \cdot R_L}{Z_r} \tag{5.5}$$

$$\gamma = \frac{f_s}{f_r} \tag{5.6}$$

$$M = \frac{1}{\sqrt{\frac{\left(\gamma - \frac{1}{\gamma}\right)^2}{\left(r^2 + 1\right)}}}$$

(5.7)

### 3.1.2 Conversores quase-ressonantes

Os conversores Quase-Ressonantes funcionam de forma híbrida, entre os conversores ressonantes convencionais e os conversores PWM. O princípio de funcionamento é baseado na substituição do interruptor do conversor PWM por um interruptor operando de modo ressonante. Dessa maneira, qualquer conversor PWM pode operar utilizando a topologia Quase-Ressonante. Os interruptores de operação ressonante podem funcionar nos modos ZCS e ZVS.

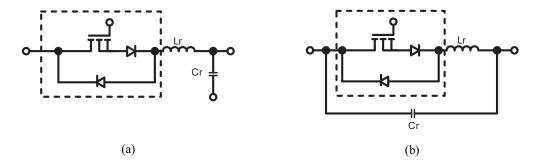

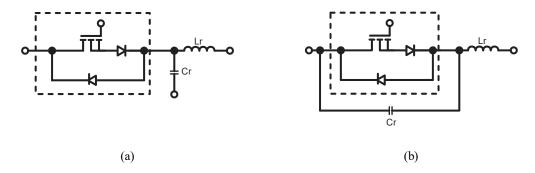

Para o modo ZCS, um indutor é inserido em série com o interruptor, assim durante o *turn-on* do interruptor o aumento da corrente lentamente. Esse crescimento possui comportamento oscilatório ocasionado pela ressonância entre indutor e capacitor acrescentados junto ao interruptor. O comportamento ressonante é responsável pelo zero de corrente durante o *turn-off* do interruptor (RASHID, 2011). Na Figura 3.6 é apresentado os interruptores ressonantes ZCS, do tipo M e tipo L, para ambos o comportamento é o mesmo (LIU; LEE, 1984).

Figura 3.6 - Interruptor Ressonante de comutação com corrente zero (Zero Current Switch).

Fonte: (RASHID, 2011)

Para o modo ZVS, um capacitor é conectado em paralelo com o interruptor de forma que esse possua característica de zero de tensão durante o *turn-on*. Com a adição do capacitor e de um indutor um comportamento ressonante é criado de forma a suavizar a tensão no interruptor durante a etapa em que essa está desligada (RASHID, 2011). Na Figura 3.7 são apresentados os tipos M e L para interruptores ZVS.

Figura 3.7 - Interruptor Ressonante de comutação com tensão zero (Zero Voltage Switch).

Fonte: (RASHID, 2011)

Utilizando essa metodologia, a corrente e a tensão no interruptor são forçadas a oscilar de uma forma quase-ressonante para que seja possível obter o ZVS e o ZCS.

# 3.1.3 Comutação com Zero de Corrente (ZCS)

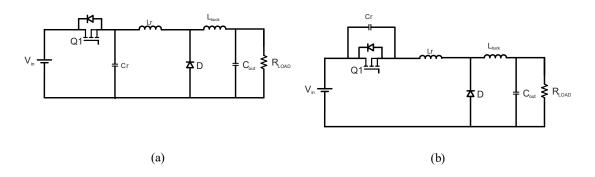

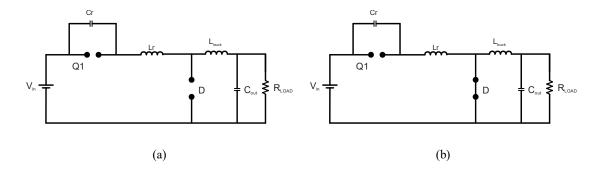

Como já comentado, o circuito ZCS é capaz de zerar a corrente na chave antes que seja realizado o desligamento do interruptor, eliminando as perdas de *turn-off*, sendo possível aplicar essa característica a qualquer conversor *PWM*, tais como *buck* e *boost*. As topologias de conversores quase-ressonantes em ZCS, analisadas acima, podem ser observadas na Figura 3.8 e na Figura 3.9, sendo *buck ZCS* e *boost* ZCS, respectivamente.

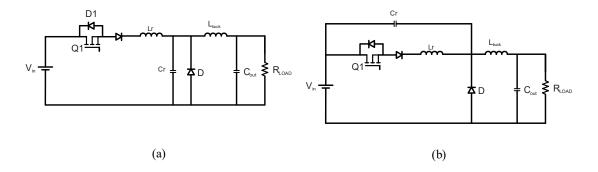

Figura 3.8 - Topologias buck quase-ressonante do tipo ZCS

Fonte: (RASHID, 2011)

Figura 3.9 - Topologias boost quase-ressonante do tipo ZCS

Fonte: (RASHID, 2011)

Os comportamentos dos conversores *buck* e *boost* podem ser analisados através da Figura 3.10. Como pode ser notado em ambos, a corrente ressonante passa a circular pelo diodo anti-paralelo do interruptor antes de ser iniciado o desligamento do mesmo, fazendo com que não haja corrente nem tensão sobre o interruptor durante o desligamento.

Figura 3.10 - Formas de onda: (a) buck ZCS; (b) boost ZCS

Fonte: Adaptado de (ANG; OLIVA, 2005)

A operação dos conversores se dá de forma muito similar à dos conversores *PWM* convencionais, possuindo como diferencial uma etapa ressonante, a qual, no caso dos conversores ZCS, ocorre durante o tempo em que o interruptor se encontra ligado.

### 3.1.4 Comutação com Zero de Tensão (ZVS)

Em relação aos conversores ZVS, esses são capazes de zerar a tensão no interruptor antes de ele ser ligado, eliminando as perdas de *turn-on*, tornando possível aplicar essa característica a qualquer conversor *PWM*, como *buck* e *boost*. As topologias *buck* e *boost* quaseressonantes do tipo ZVS podem ser observadas na Figura 3.11 e na Figura 3.12, respectivamente.

Figura 3.11 - Topologias buck quase-ressonante do tipo ZVS

Fonte: (RASHID, 2011)

Figura 3.12 - Topologias boost quase-ressonante do tipo ZVS

Fonte: (RASHID, 2011)

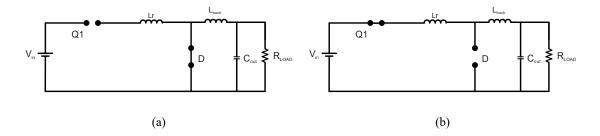

Os comportamentos dos conversores buck e boost podem ser analisados através da Figura 3.13. Sendo verificado que para ambos, a corrente ressonante passa a circular pelo diodo anti-paralelo do interruptor antes do sinal no terminal de porta do interruptor desliga-lo. Esse

fato faz com que não haja corrente ou tensão sobre o interruptor durante o desligamento do mesmo.

Vgs

V<sub>a</sub> + I<sub>a</sub>/Zr

V<sub>a</sub> + I<sub>a</sub>/Zr

V<sub>a</sub>

V<sub>a</sub>

(a)

Vgs

(b)

Figura 3.13 - Formas de onda: (a) buck ZVS; (b) boost ZVS

Fonte: Adaptado de (ANG; OLIVA, 2005)

Assim como nos conversores ZCS, os conversores ZVS possuem operação muito similar à dos conversores *PWM* convencionais, tendo como diferencial uma etapa ressonante, que, no caso dos conversores ZVS, ocorre durante o tempo em que o interruptor se encontra desligado.

# 4 CONVERSOR BUCK OPERANDO EM COMUTAÇÃO FORÇADA

Este capítulo tem por objetivo descrever os procedimentos de projeto de um conversor abaixador de tensão (*buck*) sem nenhuma técnica de comutação para amenizar as perdas. Além disso, serão avaliadas a origem dessas através de análise por cálculo, simulação e procedimento experimental.

### 4.1 FUNCIONAMENTO BUCK SÍNCRONO