# FEDERAL UNIVERSITY OF SANTA MARIA TECHNOLOGY CENTER GRADUATE PROGRAM IN COMPUTER SCIENCE

Michael Guilherme Jordan

# BOOSTING SIMD BENEFITS THROUGH A RUN-TIME AND ENERGY EFFICIENT DLP DETECTION

#### Michael Guilherme Jordan

# BOOSTING SIMD BENEFITS THROUGH A RUN-TIME AND ENERGY EFFICIENT DLP DETECTION

Dissertation presented to the Graduate Program in Computer Science (PPGCC) from the Federal University of Santa Maria (UFSM, RS) as requirement to obtain the degree of Master of Computer Science.

Advisor: Prof. Dr. Mateus Beck Rutzig

#### Jordan, Michael Guilherme

Boosting SIMD Benefits through a Run-time and Energy Efficient DLP Detection / por Michael Guilherme Jordan. – 2019.

92 f.: il.; 30 cm.

Advisor: Mateus Beck Rutzig

Dissertation - Federal University of Santa Maria, Technology Center, Graduate Program in Computer Science, RS, 2019.

1. DLP. 2. SIMD. 3. Vectorization. 4. ARM NEON. I. Rutzig, Mateus Beck. II.Boosting SIMD Benefits through a Run-time and Energy Efficient DLP Detection.

© 2019

All rights reserved to Michael Guilherme Jordan. Reproduction of parts or whole of this work can only be done by citing the source. E-mail: michael.jordan@ecomp.ufsm.br

#### Michael Guilherme Jordan

# BOOSTING SIMD BENEFITS THROUGH A RUN-TIME AND ENERGY EFFICIENT DLP DETECTION

Dissertation presented to the Graduate Program in Computer Science (PPGCC) from the Federal University of Santa Maria (UFSM, RS) as requirement to obtain the degree of Master of Computer Science.

| Approved in February 22, 2019:                   |

|--------------------------------------------------|

|                                                  |

|                                                  |

| Mateus Beck Rutzig, Dr. (UFSM)                   |

| (Presidente/Orientador)                          |

|                                                  |

| Antonio Carlos Schneider Beck Filho, Dr. (UFRGS) |

| Carlos Henrique Barriquello, Dr. (UFSM)          |

Santa Maria, RS

#### ACKNOWLEDGMENT

After an intensive period of two years, today is the day: writing this note of thanks is the finishing touch on my dissertation. It has been a period of intense learning for me, not only in the scientific level, but also on a personal level. I would like to reflect on the people who have supported and helped me so much throughout this period.

I would first like to thank my advisor, Prof. Mateus Beck Rutzig, Ph.D., for your valuable guidance, pacience, friendship, excellent cooperation and for all the opportunities I was given to conduct my research and further my dissertation.

I would also like to thank my parents, José Inácio Jordan and Silvia Inês Hoffmann Jordan, and my girlfriend, Tamires Dolores Santos Pereira, for their wise counsel and all the emotional support. You are always there for me.

In addition, i would like to thank my colleagues and friends, from GMICRO Research Group at UFSM, Tiago Knorst and Julio Vicenzi, for their wonderful collaboration. You supported me greatly.

Finally, i would like to thank my friends: Rafael Fão de Moura, Denise Lange Albrecht, Iaçanã I. Weber, Michel Duarte, Juliana Brondani, Giovani Soares, Luana Palma, Deivis Strieder, the RPG Group, the Football Group, among others. Thanks for all the fun times and the support given to each other by deliberating over our problems and findings.

Thank you very much, everyone! Michael G. Jordan Santa Maria, RS, January 29, 2019.

#### **ABSTRACT**

# BOOSTING SIMD BENEFITS THROUGH A RUN-TIME AND ENERGY EFFICIENT DLP DETECTION

AUTHOR: MICHAEL GUILHERME JORDAN ADVISOR: MATEUS BECK RUTZIG

Multimedia applications have been widely present in embedded devices. Due to their intrinsic nature, such application domain is benefited from Data Level Parallelism (DLP). In order to improve performance-energy tradeoff, current processors enable DLP by coupling SIMD (Single Instruction Multiple Data) engines, such as Intel AVX, ARM NEON and IBM Altivec. Special libraries and compilers are used to support DLP execution on such engines. However, timing overhead on hand coding is inevitable since most software developers are not skilled to extract DLP using unfamiliar libraries. Considering the auto-vectorization through compiler, although improving software productivity, it breaks software compatibility. Besides, both methods are limited to static code analysis, which compromises performance gains.

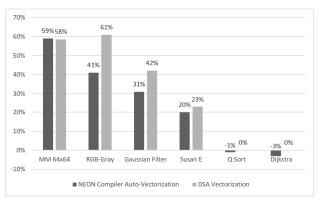

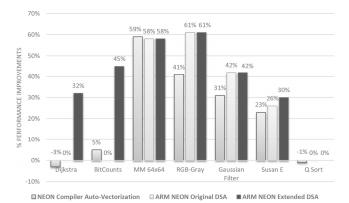

In this dissertation, we propose a runtime DLP detection named as Dynamic SIMD Assembler (DSA), which transparently identifies vectorizable code regions to execute in the ARM NEON engine. Due to its dynamic fashion, DSA keeps software compatibility and avoids timing overhead on software developing process. Results show that DSA outperforms ARM NEON auto-vectorization compiler by 32% since it applies the partial vectorization of loops and covers wider vectorizable regions, such as Dynamic Range, Sentinel and Conditional Loops. In addition, DSA outperforms hand-vectorized code using ARM library by 26% reducing 45% of energy consumption with no penalties over software development time.

**Keywords:** DLP. SIMD. Vectorization. ARM NEON.

#### **RESUMO**

### AUMENTANDO OS BENEFÍCIOS SIMD POR MEIO DE UMA DETECÇÃO DE DLP EM TEMPO DE EXECUÇÃO E ENERGETICAMENTE EFICIENTE

AUTOR: MICHAEL GUILHERME JORDAN ORIENTADOR: MATEUS BECK RUTZIG

Aplicações multimídia estão amplamente presentes em dispositivos embarcados. Devido à sua natureza intrínseca, este nicho de aplicação é beneficiado pelo Paralelismo a Nível de Dados (DLP). Para melhorar a relação performance-energia, os processadores atuais habilitam o DLP pelo acoplamento de engines SIMD (Single Instruction Multiple Data), como Intel AVX, ARM NEON and IBM Altivec. Bibliotecas e compiladores especiais são usados para suportar a execução de DLP nesses mecanismos. No entanto, a sobrecarga de tempo aplicada a vetorização através de programação manual é inevitável, uma vez que a maioria dos desenvolvedores de software não tem habilidade para extrair o DLP usando bibliotecas desconhecidas. Considerando a auto-vetorização através do uso de compilador, apesar de melhorar a produtividade de software, tal método quebra compatibilidade de software. Além disso, ambos os métodos estão limitados à análise de código estático, o que compromete os ganhos de desempenho.

Nesta dissertação, propomos uma detecção de DLP em tempo de execução chamada Dynamic SIMD Assembler (DSA), que identifica de forma transparente as regiões de código que podem ser vetorizadas para serem executadas no mecanismo ARM NEON. Devido à sua forma dinâmica, a DSA mantém compatibilidade de software e evita a sobrecarga de tempo no processo de desenvolvimento de software. Os resultados mostram que a DSA supera a auto-vetorização através do uso do compilador ARM NEON em 32%, pois aplica a vetorização parcial de loops e abrange mais regiões vetorizáveis, como Loops de Tamanho Dinâmico, Loops Sentinela e Loops Condicionais. Além disso, a DSA supera a programação manual através do uso da biblioteca ARM em 26% reduzindo 45% do consumo de energia sem penalidades em relação ao tempo de desenvolvimento do software.

Palavras-chave: DLP. SIMD. Vetorização. ARM NEON.

### LIST OF FIGURES

| CONCEPT        | UAL ANALYSIS                                               |    |

|----------------|------------------------------------------------------------|----|

| Figure 1 –     | Scalar Registers vs Vector Registers                       | 19 |

| Figure 2 –     | VMIPS Overview                                             | 20 |

| Figure 3 –     | ARM A8 Processor Schematic                                 | 21 |

| Figure 4 –     | ARM NEON Engine                                            | 22 |

| Figure 5 –     | Hand-code Programming Overview                             | 24 |

| Figure 6 –     | Auto-vectorization Compiler Overview                       | 25 |

| Figure 7 –     | Just-in-time and Traditional Compiler Comparison           | 27 |

| Figure 8 –     |                                                            | 28 |

| <b>DYNAMIC</b> | SIMD ASSEMBLER                                             |    |

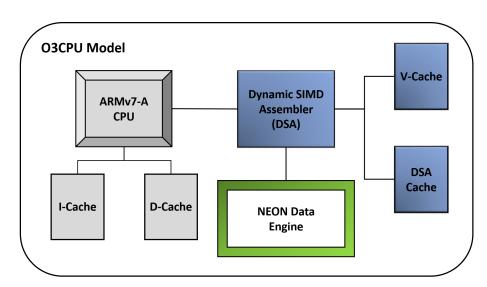

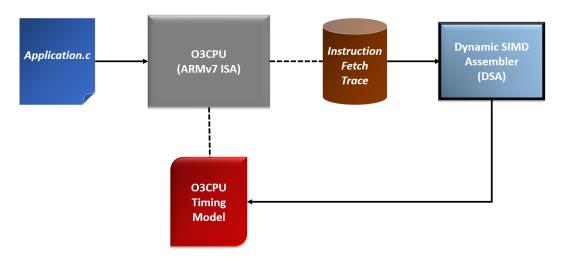

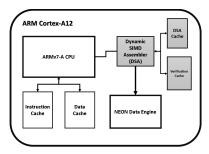

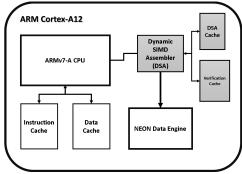

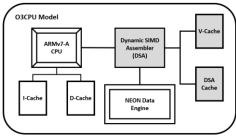

| Figure 9 –     | System Overview                                            | 33 |

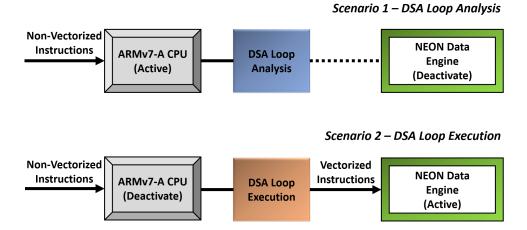

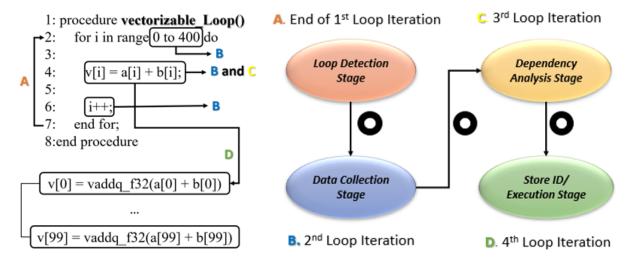

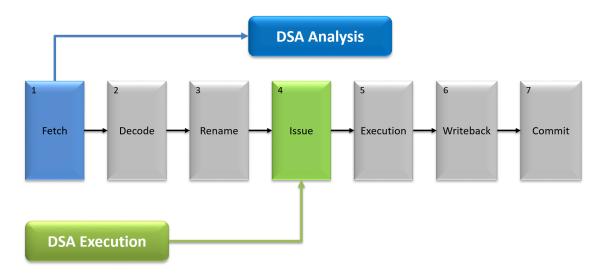

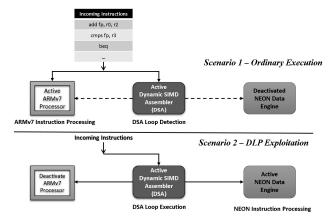

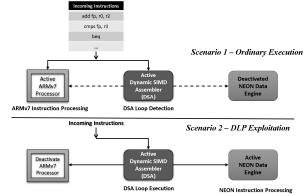

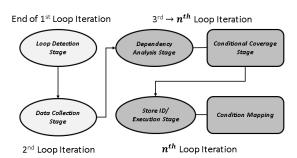

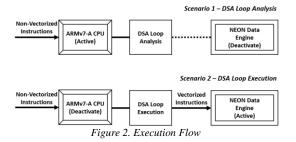

| Figure 10 –    | System Functionality Overview                              | 34 |

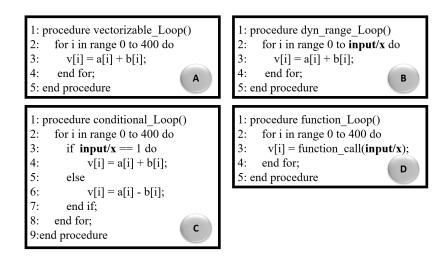

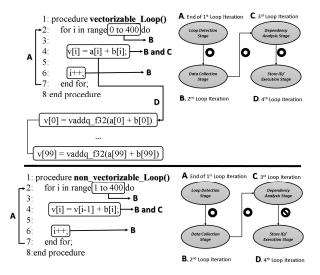

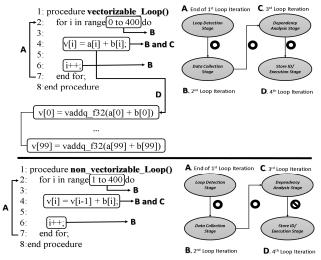

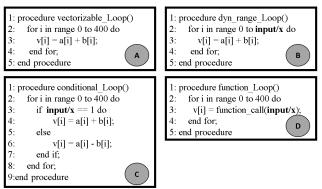

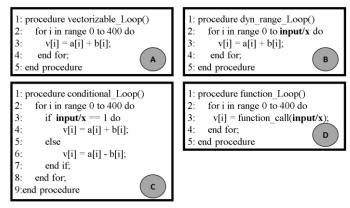

| Figure 11 –    | Loop Examples                                              | 35 |

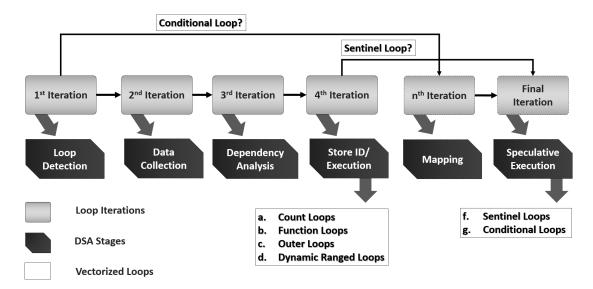

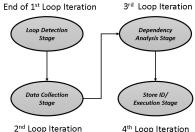

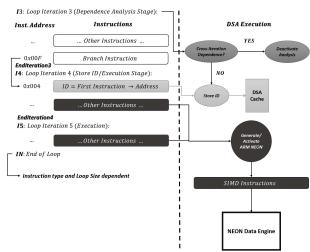

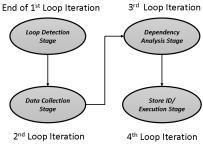

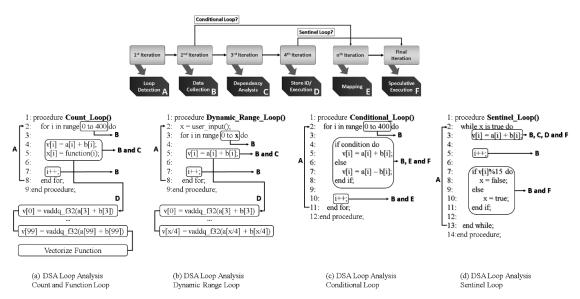

| Figure 12 –    | DSA Execution Flow                                         | 36 |

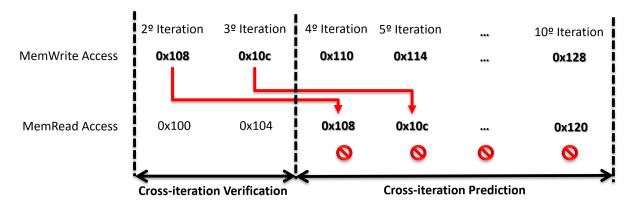

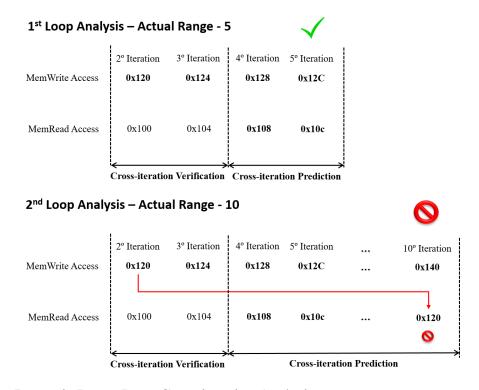

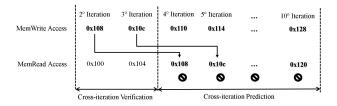

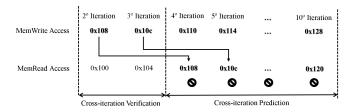

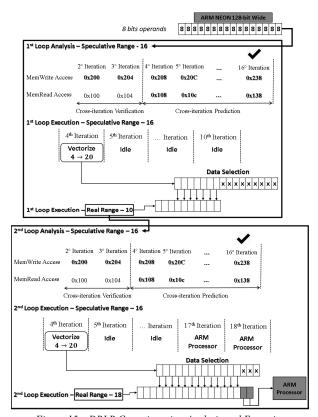

| Figure 13 –    | Cross-iteration Dependency Prediction                      | 39 |

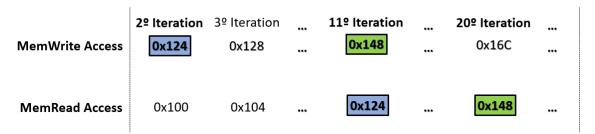

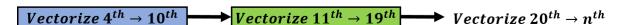

| Figure 14 –    | Partial Vectorization Analysis                             | 39 |

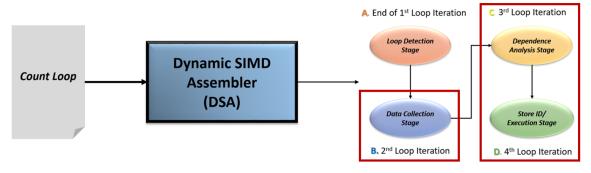

| Figure 15 –    | Count Loop Example                                         | 41 |

| Figure 16 –    | Function Loop Example                                      | 41 |

| Figure 17 –    | Outer Loop Example                                         | 42 |

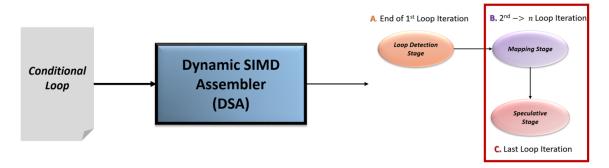

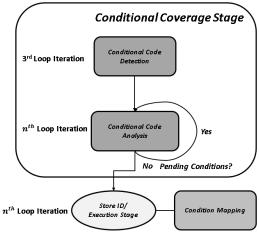

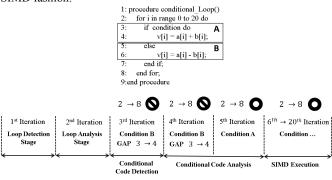

| Figure 18 –    | DSA Conditional Loop State Machine                         | 44 |

| Figure 19 –    | Conditional Loop Vectorization Analysis                    | 46 |

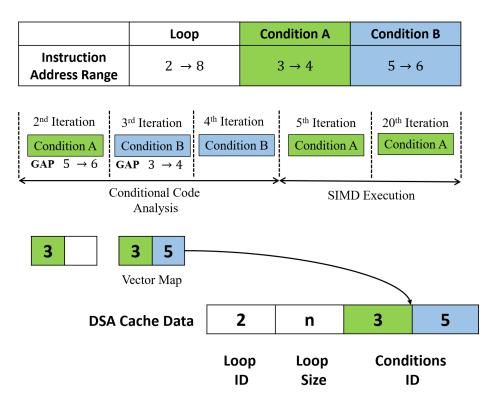

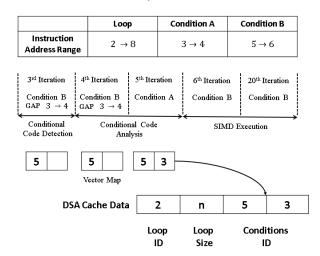

| Figure 20 –    | Conditional Code Loop Analysis Mapping and Data Storage    | 47 |

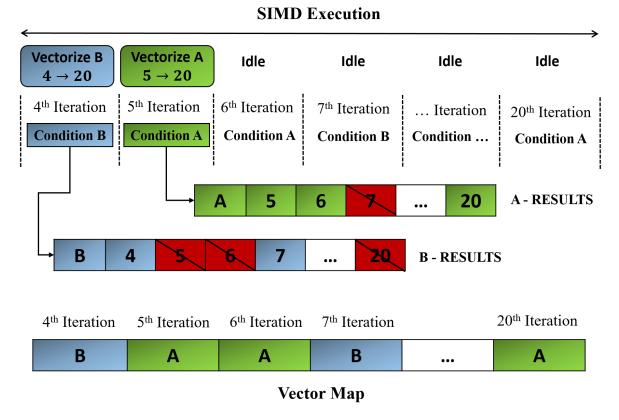

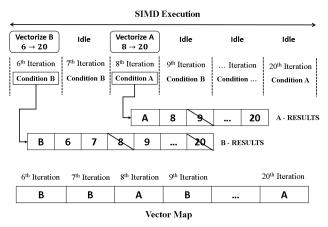

| Figure 21 –    | Conditional Code Loop Execution Mapping and Data Storage   | 48 |

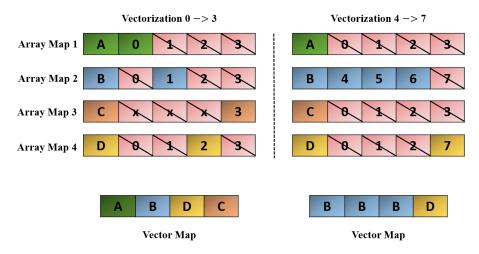

| Figure 22 –    | Conditional Code Loop Array Map Logic                      | 49 |

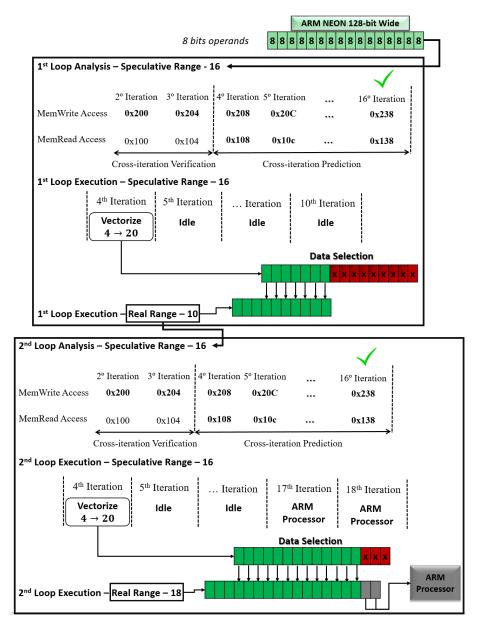

| Figure 23 –    | Sentinel Loop Cross-iteration Analysis and Execution       | 52 |

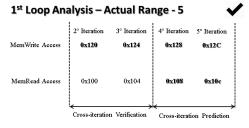

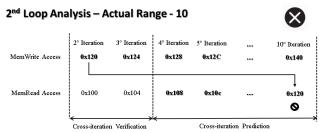

| Figure 24 –    | Dynamic Range Loop Cross-iteration Analysis                | 53 |

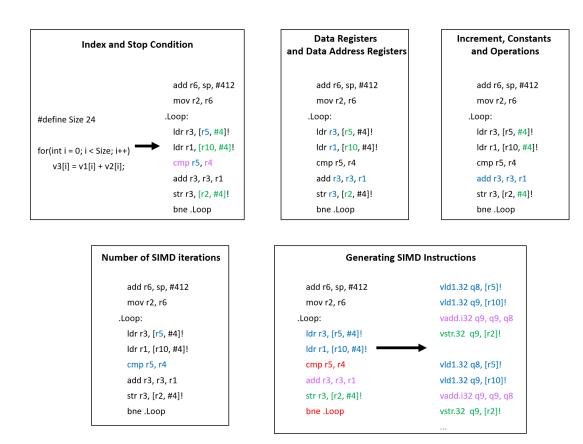

| Figure 25 –    | SIMD Instruction Generation Steps                          | 54 |

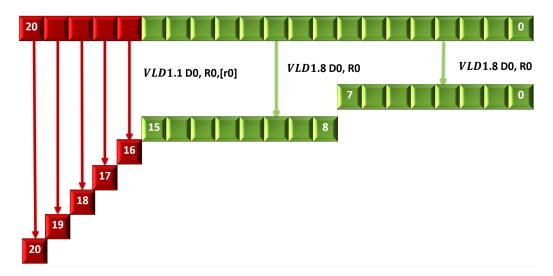

| Figure 26 –    | Leftovers                                                  | 56 |

| Figure 27 –    | Single Elements Method                                     | 56 |

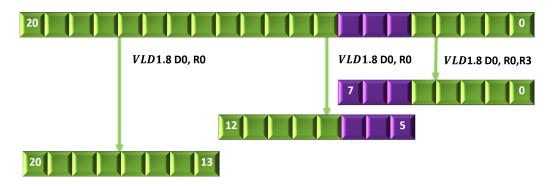

| Figure 28 –    | Overlapping Method                                         | 57 |

| Figure 29 –    | Larger Arrays Method                                       | 58 |

| <b>METHODO</b> |                                                            |    |

| Figure 30 –    | DSA Simulation Model                                       | 60 |

| Figure 31 –    | O3CPU - DSA Implementation                                 | 61 |

| Figure 32 –    | DSA Energy Analysis                                        | 62 |

| ARTICLE 1      | •                                                          |    |

| Figure 1 –     | System Overview                                            | 67 |

| Figure 2 –     | System Functionality Overview                              | 67 |

| Figure 3 –     | State Machine of DSA                                       | 67 |

| Figure 4 –     | DSA Execution                                              | 68 |

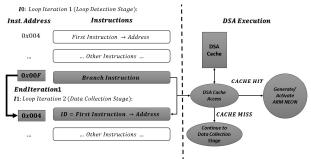

| Figure 5 –     | Loop Detection Stage Behavior                              | 68 |

| Figure 6 –     | Data Collection Stage Behavior                             | 69 |

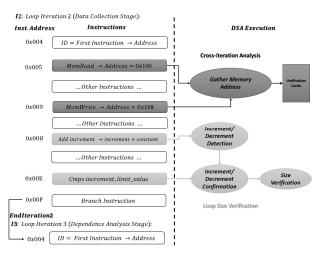

| Figure 7 –     | Data Collection Stage                                      | 69 |

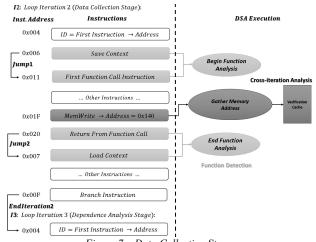

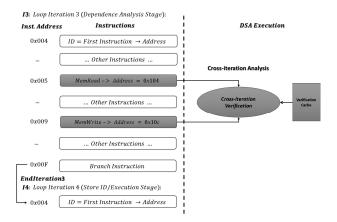

| Figure 8 –     | Dependency Analysis Stage                                  | 69 |

| Figure 9 –     | Example of a Cross-iteration Dependency Prediction Process | 70 |

| Store ID/Execution Stage Behavior                                | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ARM NEON Parallelism                                             | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| NEON Auto-Vectorization vs. DSA Vectorization Performance        | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| System Overview                                                  | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| System Functionality Overview                                    | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| State Machine of DSA                                             | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DSA Execution                                                    | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ARM NEON Parallelism                                             | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example of a Cross-iteration Dependency Prediction Process       | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Vectorizable, Dynamic Range, Conditional Code and Function Loops | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditional Loop DSA State Machine                               | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditional Code Coverage Stage                                  | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditional Code Loop Vectorization Analysis                     | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditional Code Loop Analysis Mapping and Data Storage          | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Conditional Code Loop SIMD Execution                             | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DRL Type A, DRL Type B                                           | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DRLA Cross-iteration Analysis                                    | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DRLB Cross-iteration Analysis and Execution                      | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ARM NEON Compiler AutoVec. vs. ARM NEON Original DSA vs. ARM     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| NEON Extended DSA Performance                                    | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| System Overview                                                  | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Execution Flow                                                   | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example of Loops                                                 | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DSA Analysis and Execution Process                               | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example of a Cross-iteration Dependency Prediction Process       | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DSA Partial Vectorization Technique                              | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

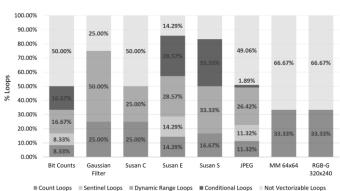

| Percentage of Loop Types in the Selected Applications            | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

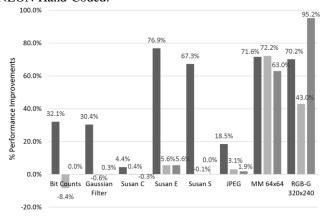

| Performance Improvements over ARM Original Execution             | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

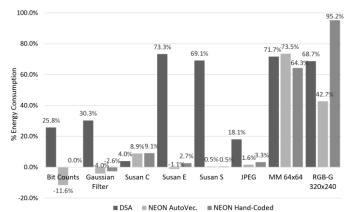

| Energy Savings over ARM Original Execution                       | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                  | ARM NEON Parallelism NEON Auto-Vectorization vs. DSA Vectorization Performance  System Overview System Functionality Overview State Machine of DSA DSA Execution ARM NEON Parallelism Example of a Cross-iteration Dependency Prediction Process Vectorizable, Dynamic Range, Conditional Code and Function Loops Conditional Loop DSA State Machine Conditional Code Coverage Stage Conditional Code Loop Vectorization Analysis Conditional Code Loop Analysis Mapping and Data Storage Conditional Code Loop SIMD Execution DRL Type A, DRL Type B DRLA Cross-iteration Analysis DRLB Cross-iteration Analysis and Execution ARM NEON Compiler AutoVec. vs. ARM NEON Original DSA vs. ARM NEON Extended DSA Performance  System Overview Execution Flow Example of Loops DSA Analysis and Execution Process Example of a Cross-iteration Dependency Prediction Process DSA Partial Vectorization Technique Percentage of Loop Types in the Selected Applications |

### LIST OF TABLES

| INTRODU       | CTION                                                          |    |

|---------------|----------------------------------------------------------------|----|

| Table 1 –     | Factors that Limit or Prevent the Automatic Loop Vectorization | 14 |

| Table 2 –     | Vectorization Techniques Comparison                            | 28 |

| RELATED       | WORK                                                           |    |

| Table 3 –     | Related Works and Proposed Technique Characteristics           | 31 |

| <b>METHOD</b> | OLOGY                                                          |    |

| Table 4 –     | Systems Setup                                                  | 62 |

| ARTICLE       | 1                                                              |    |

| Table 1 –     | Related Works and Proposed Technique Characteristics           | 67 |

| Table 2 –     | Systems Setups                                                 | 70 |

| Table 3 –     | Area overhead of DSA                                           | 71 |

| ARTICLE       | 2                                                              |    |

| Table 1 –     | Related Works and Proposed Technique Characteristics           | 74 |

| Table 2 –     | Systems Setups                                                 | 79 |

| Table 3 –     | DSA Latency                                                    | 80 |

| ARTICLE       | 3                                                              |    |

| Table 1 –     | System Setups                                                  | 86 |

| Table 2 –     | DSA Detection Latency                                          | 86 |

| Table 3 –     | DSA Energy Consumption                                         | 86 |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ALU Arithmetic Logic Unit

CGRA Coarse Grain Reconfigurable Architecture

CID Cross-iteration Dependency

CIDP Cross-iteration Dependency Prediction

CUDA Compute Unified Device Architecture

CPU Central Processing Unit

DLP Data Level Parallelism

DRAM Dynamic Random Access Memory

DSA Dynamic SIMD Assembler

FU Functional Unit

FP Floating Point

GPP General Purpose Processor

GPU Graphic Processing Units

HDL Hardware Description Language

ID Identification

ILP Instruction Level Parallelism

ISA Instruction Set Architecture

JIT Just-in-time

LLVM Low Level Virtual Machine

LPA Loop-Oriented Pointer Analysis

LRU Least Recently Used

McPAT Multicore Power, Area, and Timing

MMX Multimedia Extensions

NCID No Cross-Iteration Dependency

ROB Reorder Buffer

RTL Register Transfer Level

SIMD Single Instruction Multiple Data

SM State Machine

SoC System-on-Chip

SRP Samsung Reconfigurable Processor

SSE Streaming SIMD Extensions

SW Software

TLP Thread Level Parallelism

VC Verification Cache

VHDL VHSIC Hardware Description Language

### **SUMMARY**

| 1       | INTRODUCTION                                          | 14 |

|---------|-------------------------------------------------------|----|

| 2       | CONCEPTUAL ANALYSIS                                   | 17 |

| 2.1     | ILP, TLP AND DLP EXPLOITATION                         |    |

| 2.2     | SIMD ARCHITECTURES                                    | 18 |

| 2.2.1   | Vector Architectures                                  |    |

| 2.2.2   | SIMD Instruction Set Extensions                       | 20 |

| 2.2.3   | Graphic Processing Units                              | 23 |

| 2.3     | CODE VECTORIZATION                                    |    |

| 2.3.1   | Hand-code Programming Vectorization                   | 24 |

| 2.3.2   | Auto-vectorization Compiler                           |    |

| 2.3.3   | Just-in-time Vectorization Compilers                  | 26 |

| 2.3.4   | Critical Analysis                                     |    |

| 2.4     | CROSS-ITERATION DEPENDENCIES                          |    |

| 3       | RELATED WORKS                                         | 29 |

| 3.1     | AUTO-VECTORIZATION COMPILER AND VECTOR LIBRARY APPRO- |    |

|         | ACHES                                                 |    |

| 3.2     | ISA/HARDWARE MODIFICATION APPROACHES                  | 30 |

| 3.3     | JUST-IN-TIME APPROACHES                               | 31 |

| 4       | DYNAMIC SIMD ASSEMBLER                                | 33 |

| 4.1     | SYSTEM OVERVIEW                                       | 33 |

| 4.2     | DSA COVERAGE                                          | 34 |

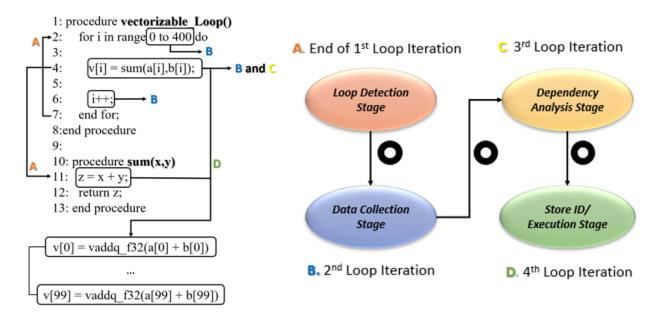

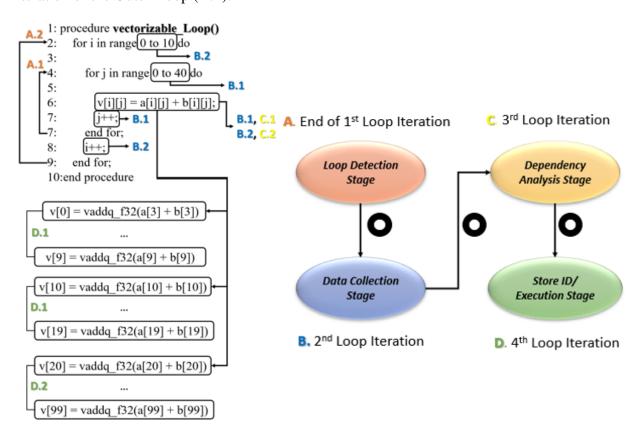

| 4.3     | DSA OVERVIEW                                          | 35 |

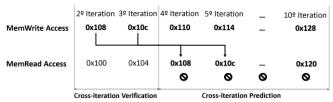

| 4.4     | CROSS-ITERATION DEPENDENCY VERIFICATION               | 38 |

| 4.5     | PARTIAL VECTORIZATION                                 | 39 |

| 4.6     | DSA - ANALYSIS AND EXECUTION                          | 40 |

| 4.6.1   | Count Loops                                           | 40 |

| 4.6.2   | Function Loops                                        | 41 |

| 4.6.3   | Inner/Outer Loops                                     | 42 |

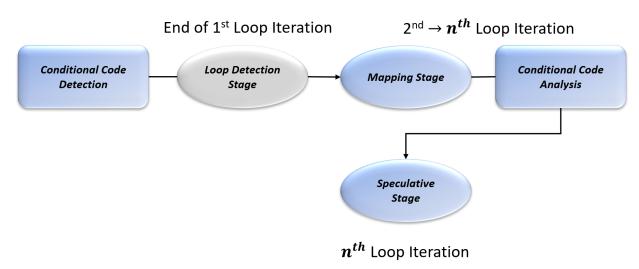

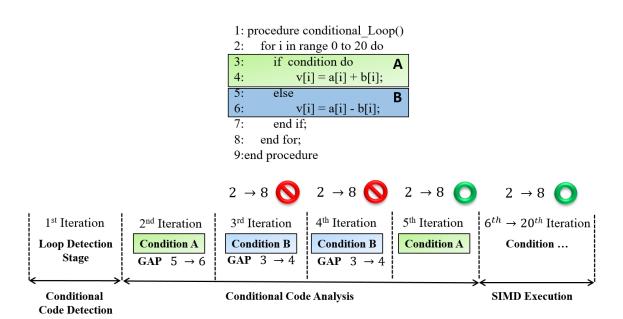

| 4.6.4   | Conditional Loops                                     | 43 |

| 4.6.4.1 | Conditional Loops Vectorization                       | 45 |

| 4.6.4.2 | Conditional Loop SIMD Execution                       | 47 |

| 4.6.4.3 | Conditional Loop DSA Limitations                      | 48 |

| 4.6.5   | Sentinel Loops Vectorization                          | 50 |

| 4.6.6   | Dynamic Range Loop Vectorization                      | 52 |

| 4.7     | GENERATING SIMD INSTRUCTIONS                          | 53 |

| 4.8     | DEALING WITH LEFTOVERS                                | 55 |

| 4.8.1   | Single Elements                                       | 56 |

| 4.8.2   | Overlapping                                           | 57 |

| 4.8.3   | Larger Arrays                                         | 57 |

| 5       | METHODOLOGY                                           | 59 |

| 5.1     | O3CPU PROCESSOR/DSA IMPLEMENTATION                    | 60 |

| 5.2     | DSA AND O3CPU ENERGY RESULTS                          | 61 |

| 5.3     | SYSTEMS SETUP                                         | 62 |

| 6       | ARTICLE 1 - IMPROVING SOFTWARE PRODUCTIVITY AND PER-  |    |

|         | FORMANCE THROUGH A TRANSPARENT SIMD EXECUTION         | 64 |

| 7  | ARTICLE 2 - RUNTIME VECTORIZATION OF CONDITIONAL CODE |    |

|----|-------------------------------------------------------|----|

|    | AND DYNAMIC RANGE LOOPS TO ARM NEON ENGINE            | 71 |

| 8  | ARTICLE 3 - BOOSTING SIMD BENEFITS THROUGH A RUN-TIME |    |

|    | AND ENERGY EFFICIENT DLP DETECTION                    | 80 |

| 9  | DISCUSSION                                            | 87 |

| 10 | CONCLUSION AND FUTURE WORK                            | 89 |

#### 1 INTRODUCTION

The benefits of the classical transistor shrink may cease in 2021 (COURTLAND, 2016), along with it, the increasing number of multimedia applications has been demanding for more and more performance. In order to provide such performance requirements considering the technological limitation, most architectural solutions attempt to exploit some inherent parallelism available in such applications.

In this scenario, the exploitation of Data Level Parallelism (DLP) has gained increasing relevance since multimedia algorithms are plentiful of Data-Parallel Statements. The DLP can be classified as the capability of performing operations simultaneously over multiple data. Currently, Single Instruction Multiple Data (SIMD) engines are used in market processors to boost multimedia application performance through DLP exploitation. ARM NEON (ARM LI-MITED, 2008), Intel SSE/AVX (LOMONT et al., 2011) and IBM Altivec (DIEFFENDORF et al., 2000) are SIMD engines coupled to general purpose processors (GPP) with the purpose of benefiting from the energy-performance tradeoff on data-parallel applications. The execution of such engines is supported by vector instructions that are applied to vectorizable regions in code. The most significant parcel of vectorizable regions is found in loop statements, which have the property of repeating operations over multiple data. In order to convert loops to vector instructions, SIMD engines apply vectorization techniques such as: auto-vectorization through compiler or hand-coding vectorization. The hand-coding vectorization consists on using lowlevel functions available on specific libraries to convert vectorizable regions (loops) in SIMD instructions during programming time. Such method requires programming expertise reducing software productivity. The auto-vectorization technique lies on converting vectorizable regions to SIMD instructions during compile time, which does not affect software productivity since no specific library usage is required.

Table 1 shows some factors that inhibit the automatic loop vectorization through compiler. Some limitations can be overcome by combining both techniques (Lines 8 and 10 - Table 1). However, loops with dynamic behavior, such as sentinel loops, dynamic ranged loops and conditional loops, which depend on information generated during execution time, are not efficiently vectorized by such methods since both operate during programming or compile time (statically) (Lines 4, 9 and 12 – Table 1).

Table 1 – Factors that limit or prevent the automatic loop vectorization

|                                                      | Inhibiting Factor              | Extent to which applies                                                              |  |  |  |  |

|------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|

| 1                                                    | No vector access pettern       | If variables in a loop lack a vector access pattern, the                             |  |  |  |  |

| 1                                                    | No vector access pattern       | compiler cannot automatically vectorize the loop.                                    |  |  |  |  |

|                                                      |                                | Where there is a possibility of the use and storage of arrays overlapping on dif-    |  |  |  |  |

| 2                                                    | Data dependencies between      | ferent iterations of a loop, there is a data dependency problem. A loop cannot be    |  |  |  |  |

| 2                                                    | different iterations of a loop | safely vectorized if the vector order of operations can change the results, so the   |  |  |  |  |

|                                                      |                                | compiler leaves the loop in its original form or only partially vectorizes the loop. |  |  |  |  |

|                                                      |                                | Performing relatively few arithmetic operations on large data sets retrieved         |  |  |  |  |

| 3                                                    | Memory hierarchy               | from main memory is limited by the memory bandwidth of the system. Most              |  |  |  |  |

|                                                      | Memory merarchy                | processors are relatively unbalanced between memory bandwidth and pro-               |  |  |  |  |

|                                                      |                                | cessor capacity This can adversely affect the automatic vectorization process.       |  |  |  |  |

|                                                      | Iteration count not fi-        | For automatic vectorization, it is generally best to write simple lo-                |  |  |  |  |

| 4                                                    | xed at start of loop           | ops with iterations that are fixed at the start of the loop. If a loop does          |  |  |  |  |

|                                                      | acd at start of loop           | not have a fixed iteration count, automatic addressing is not possible.              |  |  |  |  |

| 5                                                    | Carry-around scalar variables  | Carry-around scalar variables are a problem for automatic vectorization because      |  |  |  |  |

|                                                      |                                | the value computed in one pass of the loop is carried forward into the next pass.    |  |  |  |  |

| 6                                                    | Pointer aliasing               | Pointer aliasing prevents the use of automatically vectorized code.                  |  |  |  |  |

| 7                                                    | Indirect addressing            | Indirect addressing is not vectorizable because the NEON unit                        |  |  |  |  |

|                                                      |                                | can only deal with vectors stored consecutively in memory.                           |  |  |  |  |

|                                                      | Separating access to dif-      | Each part of a structure must be accessed within                                     |  |  |  |  |

| 8                                                    | ferent parts of a struc-       | the same loop for automatic vectorization to occur.                                  |  |  |  |  |

|                                                      | ture into separate loops       |                                                                                      |  |  |  |  |

| 9                                                    | Inconsistent length of mem-    | If members of a loop structure are not all the same                                  |  |  |  |  |

|                                                      | bers within a loop structure   | length, the compiler does not attempt to use vector loads.                           |  |  |  |  |

|                                                      |                                | Calls to non-inline functions from within a loop inhibits vectori-                   |  |  |  |  |

| 10                                                   | Calls to non-inline functions  | zation. If such functions are to be considered for vectorization,                    |  |  |  |  |

|                                                      |                                | they must be marked with theinline orforceinline keywords.                           |  |  |  |  |

| 11                                                   | Source code without loops      | Automatic vectorization involves loop analysis.                                      |  |  |  |  |

| Without loops, automatic vectorization cannot apply. |                                |                                                                                      |  |  |  |  |

| 12                                                   | if and switch statements       | Extensive use of if and switch statements in loop                                    |  |  |  |  |

| 12                                                   | ii and switch statements       | can affect the efficiency of automatic vectorization.                                |  |  |  |  |

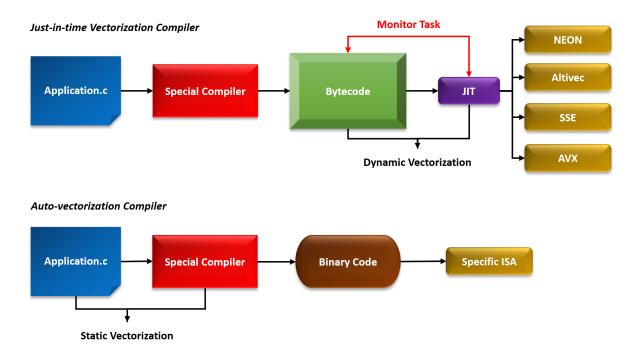

Besides both methods present performance limitations due their static fashion, the automatic vectorization and hand-coding programming also require code recompilation, which breaks binary compatibility. To overcome such limitations, Just-in-time (JIT) compiler vectorization approaches emerge. The JIT compiler is capable of exploiting DLP by monitoring vectorizable regions present in a code during runtime. By its dynamic fashion, it is possible to vectorize loops with dynamic behavior and no code recompilation is required, since a JIT compiled code is ISA (Instruction Set Architecture) independent. However, a JIT compiled code generation demands more time than a binary generation, which is produced by an autovectorization compiler. In addition, such method requires monitor tasks to detect vectorizable regions, which results in performance penalties.

The solution proposed in this dissertation lies on removing the dependency of static DLP exploitation methods through an engine that is capable of exploiting DLP during execution time. In this way, we created the Dynamic SIMD Assembler (DSA). The DSA can analyze vectorizable regions during runtime and generate SIMD instructions based on such regions. By operating at runtime, DSA increases software productivity, keeps binary compatibility and

embraces parallelism opportunities that have both static and dynamic behavior. Unlike a JIT compiler approach, the DSA implies in no performance penalties, since it detects vectorizable regions parallel to the binary execution by using its own hardware. Considering the DSA system proposed in (JORDAN, 2018), it is capable of outperforming the ARM NEON autovectorization technique in 32%. When compared to the ARM NEON library usage approach (Hand-vectorized Code), it can outperform such method by 26%. In addition, the DSA achieves 45% of energy savings over the ARM original execution.

The remaining chapters of this dissertation are based on the Integrated Scientific Articles format, where the formatting imposed by each conference will be respected. Chapter 2 presents the conceptual analysis. Chapter 3 presents the related works. In Chapter 4, the description and implementation of the DSA is addressed. Chapter 5 discusses the methodology used to perform experiments. Scientific articles are presented during chapter 6, 7 and 8, where the order of presentation respects the submission dates of each article. In chapter 9 there is a discussion about the articles. Finally, the conclusion will be presented during chapter 10. It is important to emphasize that all the articles present in this dissertation were submitted and approved in the following conferences: Improving Software Productivity and Performance through a Transparent SIMD Execution (Chapter 6 - SBCCI), Runtime Vectorization of Conditional Code and Dynamic Range Loops to ARM NEON Engine (Chapter 7 - SBESC) and Boosting SIMD Benefits through Run-time and Energy Efficient DLP Detection (Chapter 8 - DATE).

#### 2 CONCEPTUAL ANALYSIS

This chapter provides a quantitative sight of the concepts mentioned in this work. The section 2.1 presents all types of parallelism in which an application may present. Section 2.2 discusses Conventional SIMD Architectures. Section 2.3 presents Code Vectorization techniques applied to SIMD Architectures.

#### 2.1 ILP, TLP AND DLP EXPLOITATION

Pipelining technique (HENESSY; PATTERSON 2011) is able to overlapping the execution of instructions when they are data independent. The potential overlap among instructions is denominated Instruction Level Parallelism (ILP) since the instructions can be executed in parallel in order to accelerate applications. However, the study suggested by (WALL, 1991), proves that there are acceleration bounds related with ILP exploitation. The approach takes five processors, ranging from a best one (perfect branch predictor, perfect memory alias analysis and perfect register renaming) to a worst one (branches always mispredicted, no alias analysis, no register renaming). It is shown that the limits of ILP could be as high as 20 instructions per cycle in the perfect processor, for most of the benchmarks.

To overcome such limit, many micro-architectural techniques like superscalar execution, out-of-order execution, register renaming and speculative execution have been applied considering the hardware perspective (HENESSY; PATTERSON 2011). From the software perspective, compile and programming techniques that involves prediction of data and control flow, loop unrolling and software pipelining (ALLEN et al., 2001) (AHO et. al, 2014) are constantly applied.

Thread Level Parallelism (TLP) emerged as a performance and energy alternative due to the limits on performance gains imposed by ILP exploitation. The TLP Exploitation is achieved when each processor executes threads of the same application over different processors using the same or different data.

According to the Amdahl's Law (AMDAHL, 1967), the serial portions of a program that cannot be executed in parallel limits the speed-up provided by the TLP technique. Plenty researches (HILL et al., 2008) (SUN et al., 2010) reevaluate Amdahl's law premise. To expand the ILP and TLP exploitation the Data Level Parallelism (DLP) emerges.

In contrast to the TLP concept, which divides different operations to execute over the

same or different data concurrently, the DLP is based on running the same operation over a dataset. DLP opportunities are mostly present in application loops, where operations are executed multiple times over vector structures.

To improve applications performance by exploiting DLP, SIMD (Single Instruction Multiple Data) architectures, such as ARM NEON (ARM LIMITED, 2008), Intel SSE/AVX (LOMONT et al., 2011) and IBM Altivec (DIEFFENDORF et al., 2000), are widely present in market processors. Such SIMD architectures are usually coupled with special vector libraries and compilers that enable the DLP exploitation over applications.

#### 2.2 SIMD ARCHITECTURES

Considering Patterson and Henessey's approach (HENESSY; PATTERSON 2012), there are three SIMD variations: Vector Architectures, SIMD Instruction Set Extensions and Graphic Processing Units (GPUs).

#### 2.2.1 Vector Architectures

Vector Architectures are based on applying SIMD instructions into a single processor's execution pipeline. Such approaches are easier to understand and compile than other SIMD variations since there are few vector instructions that operate over a fixed data vector length and their vector loads and stores specify regular access pattern, leading to less memory misalignment issues.

However, vector architectures are considered more expensive than the SIMD Extensions, mainly due the cost of sufficient dynamic random access memory (DRAM) bandwidth, given the general reliance on caches to meet memory performance demands on conventional microprocessors.

Vector architectures gather sets of data scattered about memory, place them into large, sequential register files, operate on data in those register files and then store the results back into memory. A single instruction operates over data vectors, which results in dozens of register-to-register operations on independent data elements. These large register files work as controlled buffers to hide memory latency and to take advantage of the large memory bandwidth. Since vector loads and stores are deeply pipelined, the program relies on long memory latency only once per vector load or store and once per element load/store, thus amortizing the latency over

multiple elements.

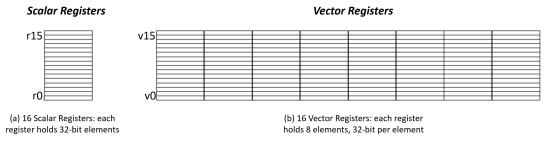

Figure 1 shows a comparison between Scalar and Vector Registers. As it can be seen, Vector Registers can hold multiple elements of n-bit per register while the Scalar Register holds a single n-bit element per register. In such case, the Scalar Register has 16 scalar registers holding 32-bit element each while the Vector Register has 16 vector registers holding 8 elements, 32-bit per element.

Figure 1 – Scalar Registers vs Vector Registers

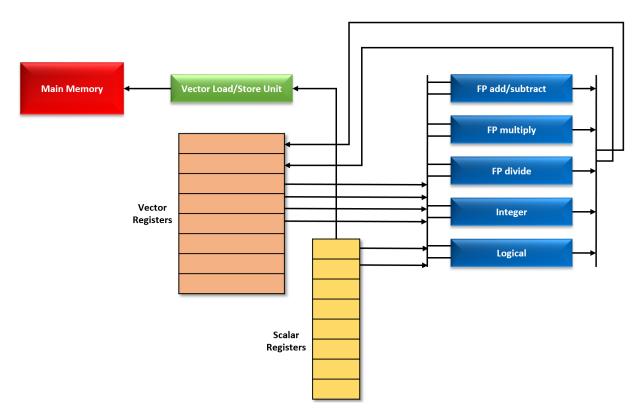

Vector Architectures are usually composed of: Vector Functional Units, Vector Registers, Vector Load-Store units and Scalar Registers. Figure 2 presents a Vector architecture example (VMIPS). As can be seen, the VMIPS is composed of:

- Vector Registers: VMIPS has eight vector registers holding 64 elements, 64-bit per element. Such registers must provide enough ports to feed all the vector functional units. The VMIPS has 16 read ports and 8 write ports that are connected to the functional unit inputs or outputs through crossbar switches. The large number of ports is one of the reasons of the long memory latency;

- Vector Functional Units (FUs): Each unit is fully pipelined, which means that all units are capable of starting a new operation on every clock cycle. A control unit is needed to detect structural and data hazards. The functional units present on the figure are the Floating-point FUs (FP add/subtract, FP multiply, FP divide), Integer FU and Logical FU;

- Vector load/store unit: The vector memory unit load or stores a vector to or from memory.

The VMIPS vector loads and stores are also fully pipelined. In this way, words can be moved between the vector registers and memory with a bandwidth of one word per clock cycle (after an initial latency). This unit is also capable of handle scalar loads and stores;

- Scalar Registers: Such registers provide input data to the vector functional units. They are also responsible for computing addresses to pass to the vector load/store unit. These

are the normal general-purpose and floating-point registers present in the original MIPS. One input of the vector functional units locks scalar values as they are read out of the scalar register file;

Cross-bar: Responsible for connecting Vector Registers, Functional Units and Load/Store Units.

Figure 2 – VMIPS Overview

#### 2.2.2 SIMD Instruction Set Extensions

The SIMD Instruction Set Extensions (SIMD Extensions) are found in most modern instruction set architectures that support multimedia applications. Considering x86 architectures, the SIMD instruction extensions started with the MMX (Multimedia Extensions) in 1996, which were followed by several SSE (Streaming SIMD Extensions) versions in the next decade. Nowadays, such architectures are commonly seen in Intel AVX and ARM NEON instruction set extensions.

SIMD Extensions have been coupled to general-purpose processors since many multimedia applications do not fully explore the vector structure sizes offered by Vector Architectures. By partitioning such structures, a vector engine could perform simultaneous operations on short vectors, offering more flexible vector operations. A vector structure of 128-bit, could perform parallel operations over sixteen 8-bit operands, eight 16-bit operands, four 32-bit operands or two 64-bit operands. Unlike vector machines with large register files, which can hold up to sixty-four 64-bit elements each of 8 vector registers (VMIPS), SIMD Extensions run over fewer operands and consequently use much smaller register files.

In contrast to vector architectures, SIMD Extensions fix the number of data operands in the opcode leading to the addition of hundreds of instructions. Vector architectures have a vector length register that specifies the number of operands for the current operation. Besides, SIMD Extensions do not offer the more refined addressing modes present in vector architectures. Such particularities make it harder for the compiler to generate SIMD code and increase the difficulty of programming for SIMD extensions.

However, besides such weaknesses, Multimedia SIMD Extensions are prominent due to their smaller cost to add to the standard arithmetic unit. Another advantage of using SIMD Extensions lies on the fact that a lot of memory bandwidth is needed to support a vector architecture, which many computers and embedded devices do not support. Also, the use of short, fixed-length of SIMD extensions makes it easy to introduce flexible instructions that can be applied to new media standards, such as instructions that consume fewer of more operands than vector can produce or instructions that perform permutations.

An example of SIMD Multimedia Extension is the ARM NEON engine. The ARM NEON is a solution for exploiting Data Level Parallelism on embedded devices. It works as a co-processor, where vector statements (NEON statements) are executed in their own pipeline.

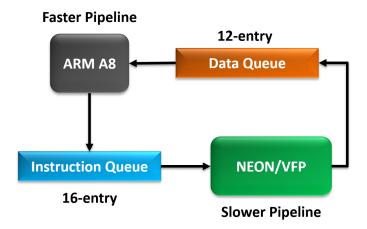

Figure 3 – ARM A8 Processor Schematic

Figure 3 presents a simple ARM A8 Processor schematic. As it can be seen, such architecture operates through the use of Instruction and Data queues to perform vector instructions

in the ARM NEON/VFP Engine. ARM A8 has a faster pipeline than the NEON Engine, which means that scalar instructions and vector instructions are executed over independent pipelines. Some ARM A8/NEON Engine aspects are:

- NEON instructions execute in their own 10-stage pipeline;

- ARM can dispatch 2 NEON instruction per cycle to the Instruction Queue;

- 16-entry instruction queue holds NEON instructions until they can enter the NEON pipeline;

- 12-entry data queue holds operations results until they can be received by the ARM A8 general-processor;

- The ARM general-processor will not stall until the NEON queue fills or some data hazard between scalar and vector instruction is found. That means that the ARM general-processor can dispatch several NEON instructions while performing other work until the NEON finishes its execution.

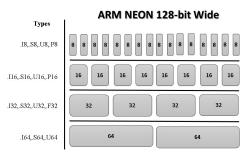

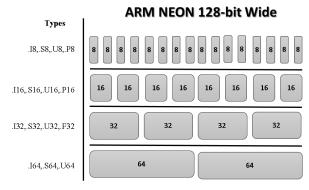

Figure 4 shows the different degrees of parallelism that can be obtained through the 128-bit wide NEON Engine depending on the type of data involved in the SIMD instruction. As it can be seen, we can perform up to 16 operations simultaneously with 8-bit integer data (.I8). With 32-bit float data (.F32), only 4 operations can be performed in parallel.

Figure 4 – ARM NEON Engine

#### 2.2.3 Graphic Processing Units

The GPU offers higher performance potential on exploiting thread level parallelism than traditional multicore computers since it is composed of thousands of processing elements. In 2006, NVIDIA created the Compute Unified Device Architecture (CUDA), a parallel processing technology that enables acceleration in general-purpose computing performance. With the specific programming language CUDA C [NVIDIA 2011], it is possible to control such processing elements and, in this way, it is possible to explore not only graphical applications but also to optimize general-purpose applications with high data-level parallelism.

Like vector architectures, GPUs work well with DLP issues. Both styles have gather-scatter data transfer and mask registers, and GPU processors have even more registers than do vector processors. In addition, both vector architectures and GPUs do not abstract hardware complexity, which demands high programming expertise to generate efficient code, affecting software productivity. Unlike most vector architectures, GPUs also rely on multithreading within a single multithread SIMD processor to hide memory latency. Besides, the GPU has many simple functional units and no scalar processor, opposed to a few deeply pipelined units like a vector processor.

#### 2.3 CODE VECTORIZATION

In 1970 decade (RUSSEL, 1977), the first computer to successfully implement a vector processor emerged. Since then, with the multimedia applications arise, vector processors and SIMD engines are present in most computers and embedded devices. Such processors have their potential exploited by Code Vectorization techniques. Code Vectorization is an optimization technique that exploits DLP through the use of SIMD instructions. Most DLP opportunities are present in loops which operate the same instruction over multiple data. Depending the number of data elements that can be merged into one vector operation, an application can reach high acceleration. To enable code vectorization, SIMD engines adopt three common methods: hand-code programming vectorization, auto-vectorization through compiler and Just-in-time (JIT) Compiler vectorization.

#### 2.3.1 Hand-code Programming Vectorization

An efficient code vectorization is challenging. Hand-code programming, where the programmer directly indicates which SIMD instruction to use, demands huge effort from the programmer since most vectorization libraries are not portable when targeting different Instruction Set Architectures (ISAs).

Figure 5 presents a Matrix Sum hand-code algorithm adapted to the NEON, SSE and Altivec extensions. As it can be seen, such vectorization libraries do not abstract hardware complexity, requiring a high programming expertise. In the NEON case, the 64-bit vector registers can placed two float elements while the 128-bit vector registers of the Altivec and SSE approaches can vectorize four float elements in parallel. Besides, each approach has its own functions to enable the use of each SIMD Engine. To solve such complexity, auto-vectorization techniques have been added to compilers in order to perform Code Vectorization automatically.

```

float sum=0;

float sum;

v2float vsum=\{0,0\};

for (i=0; i<n; i++)

for (i=0; i< n; i+=2) {

// \text{ vsum } += a[i+2:i+3];

sum += a[i+2];

vx = vld1_f32(&a[i+2]);

vsum = vadd_f32(vx,vsum);

sum = finalize_reduc(vsum);

(a) Scalar

(b) NEON (64-bit Wide)

float sum;

float sum;

v4float vsum={0,0,0,0};

v4float vsum={0,0,0,0};

vm = get_permute_vect(&a[2]);

va = lvx(&a[0]);

for (i=0; i<n; i+=4) {

for (i=0; i< n; i+=4) {

// vsum += a[i+2:i+5];

vb = lvx(&a[i+4]);

vx = movdqu(&a[i+2]);

vsum = vadd(vx,vsum);

vx = vperm (va, vb, vm);

vsum = vadd(vx, vsum);

va = vb;

sum = finalize_reduc(vsum); sum = finalize_reduc(vsum);

(c) SSE (128-bit Wide)

(d) Altivec (128-bit Wide)

```

Figure 5 – Hand-code Programming Overview

#### 2.3.2 Auto-vectorization Compiler

The Auto-vectorization Compiler is responsible for vectorizing loops during compile time. Figure 6 illustrates how the Auto-vectorization Compiler works. As it can be seen, a non-adapted code is compiled with an auto-vectorization compiler. The compilation results in

an assembly code containing SIMD instructions (vectorizable instructions). However, although improving software productivity, such method may reduce performance when compared with the hand-code programming approach.

```

0: .L2

1: add

r2, r0, r3

2: fldd