## UNIVERSIDADE FEDERAL DE SANTA MARIA CENTRO DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Catherine Marquioro de Freitas

PLATAFORMA PARA TESTES DE LEIS DE CONTROLE DE INVERSORES CONECTADOS À REDE UTILIZANDO HARDWARE-IN-THE-LOOP

#### Catherine Marquioro de Freitas

# PLATAFORMA PARA TESTES DE LEIS DE CONTROLE DE INVERSORES CONECTADOS À REDE UTILIZANDO HARDWARE-IN-THE-LOOP

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica, Área de Concentração em Processamento de Energia Elétrica, da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Prof. Leandro Michels

Freitas, Catherine Marquioro de Plataforma para Testes de Leis de Controle de Inversores Conectados à Rede Utilizando Hardware-In-The Loop / Catherine Marquioro de Freitas.- 2023. 104 p.; 30 cm

Orientador: Leandro Michels Dissertação (mestrado) - Universidade Federal de Santa Maria, Centro de Tecnologia, Programa de Pós-Graduação em Engenharia Elétrica, RS, 2023

1. Eletrônica de Potência 2. Energia Fotovoltaica 3. Firmware 4. Geração Distribuída 5. Inversor Conectado à Rede I. Michels, Leandro II. Título.

Sistema de geração automática de ficha catalográfica da UFSM. Dados fornecidos pelo autor(a). Sob supervisão da Direção da Divisão de Processos Técnicos da Biblioteca Central. Bibliotecária responsável Paula Schoenfeldt Patta CRB 10/1728.

Declaro, CATHERINE MARQUIORO DE FREITAS, para os devidos fins e sob as penas da lei, que a pesquisa constante neste trabalho de conclusão de curso (Dissertação) foi por mim elaborada e que as informações necessárias objeto de consulta em literatura e outras fontes estão devidamente referenciadas. Declaro, ainda, que este trabalho ou parte dele não foi apresentado anteriormente para obtenção de qualquer outro grau acadêmico, estando ciente de que a inveracidade da presente declaração poderá resultar na anulação da titulação pela Universidade, entre outras consequências legais.

#### Catherine Marquioro de Freitas

# PLATAFORMA PARA TESTES DE LEIS DE CONTROLE DE INVERSORES CONECTADOS À REDE UTILIZANDO HARDWARE-IN-THE-LOOP

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Engenharia Elétrica, Área de Concentração em Processamento de Energia Elétrica, da Universidade Federal de Santa Maria (UFSM, RS), como requisito parcial para obtenção do grau de **Mestre em Engenharia Elétrica**.

Aprovado em 23 de agosto de 2023:

Leandro Michels, Dr. (UFSM)

(Presidente/Orientador)

Bruno Wanderley França, Dr. (UFF)

Lucas Vizzotto Bellinaso, Dr. (UFSM)

## DEDICATÓRIA

A minha família.

#### **AGRADECIMENTOS**

Gostaria de deixar registrado a minha gratidão a todas as pessoas que, de alguma forma, contribuíram com este trabalho. O apoio e colaboração de vocês foi essencial para a realização desse trabalho.

Inicialmente agradeço a Deus.

Agradeço a toda minha família por todo amor incondicional e incentivo, em especial, à minha mãe Rosangela, ao meu pai Gilson e ao meu irmão Miguel. Ao meu namorado, e colega de profissão, Gustavo Eckhardt por todo o amor, incentivo e ajuda na elaboração desse trabalho.

Agradeço imensamente ao meu orientador, Leandro Michels pela oportunidade e pela orientação concedida durante todo o processo de pesquisa. Sua orientação e conhecimento foram fundamentais para o desenvolvimento dessa dissertação. Estendo meu agradecimento aos demais professores do Programa de Pós-Graduação em Engenharia Elétrica (PPGEE) por todo conhecimento transmitido.

Gostaria de expressar minha gratidão à Universidade Federal de Santa Maria (UFSM), ao PPGEE, bem como ao Grupo de Eletrônica de Potência e Controle (GEPOC) e ao Instituto de Redes Inteligentes (INRI) por fornecer um ambiente de pesquisa e recursos essenciais ao desenvolvimento do trabalho. Agradeço aos meus colegas e amigos do INRI pelo companheirismo e troca de conhecimento.

Agradeço ao INCT-GD, CAPES e EMBRAPII pelo apoio financeiro.

Viver é melhor que sonhar.

#### **RESUMO**

# PLATAFORMA PARA TESTES DE LEIS DE CONTROLE DE INVERSORES CONECTADOS À REDE UTILIZANDO HARDWARE-IN-THE-LOOP

AUTORA: Catherine Marquioro de Freitas Orientador: Leandro Michels

O uso de inversores em sistemas de energia tem crescido rapidamente devido ao avanço das fontes de energia renovável. O aprimoramento desses equipamentos é essencial para garantir a compatibilidade e integração com outros sistemas, bem como assegurar a confiabilidade, eficiência e segurança da rede elétrica e dos equipamentos conectados a ela. Nesse sentido, esse trabalho propõe o desenvolvimento de um firmware que permite testar leis de controle de inversores fotovoltaicos. O *firmware* desenvolvido é responsável pelo controle e funcionamento adequado do inversor e tem a proposta de ser modular. Dessa forma, é possível substituir e ajustar diferentes módulos do controle, sem que ele interfira no restante do funcionamento do inversor, eliminando a necessidade de reescrever ou adaptar todo o código do firmware. Com isso, diferentes funcionalidades e leis de controle podem ser testadas e comparadas de maneira simples e independente, possibilitando um processo de desenvolvimento mais eficiente. A implementação desse *firmware* modular tem potencial para acelerar o processo de desenvolvimento e validação de novas leis de controle para inversores fotovoltaicos, além de adaptá-los a diferentes condições e requisitos que possam surgir. O firmware foi validado a partir de ensaios normatizados da portaria do INMETRO nº 140, utilizando Hardware-In-The-Loop (HIL). O HIL permite a troca de informações em tempo real entre o firmware real e o modelo virtual do inversor e da rede elétrica, garantindo uma simulação mais precisa. Além disso, é possível emular diferentes cenários de operação e avaliar o desempenho do inversor em um ambiente controlado, seguro e de forma ágil. Nesse sentido, a plataforma de firmware modular em conjunto com o HIL oferece uma abordagem flexível e eficiente para o desenvolvimento e validação de novas tecnologias, impulsionando o avanço de inversores fotovoltaicos.

**Palavras-chave:** Eletrônica de Potência. Energia Fotovoltaica. *firmware*. Geração Distribuída. Inversor Conectado à Rede.

#### **ABSTRACT**

#### PLATFORM FOR TESTING CONTROL LAWS OF GRID-CONNECTED INVERTERS USING HARDWARE-IN-THE-LOOP

AUTHOR: Catherine Marquioro de Freitas ADVISOR: Leandro Michels

The use of inverters in power systems has experienced rapid growth due to the advancement of renewable energy sources. Improving these devices is essential to ensure compatibility and integration with other systems, as well as to guarantee the reliability, efficiency, and safety of the electrical grid and connected equipment. In this sense, this work proposes the development of firmware that allows testing control laws for photovoltaic inverters. The developed firmware is responsible for the proper control and functioning of the inverter and is designed to be modular. This allows for the replacement and adjustment of different control modules without interfering with the rest of the inverter's operation, eliminating the need to rewrite or adapt the entire firmware code. Consequently, different functionalities and control laws can be tested and compared in a simple and independent manner, enabling a more efficient development process. The implementation of this modular firmware has the potential to accelerate the development and validation of new control laws for photovoltaic inverters, as well as to adapt them to different conditions and requirements that may arise. The firmware was validated through standardized tests based on INMETRO Ordinance No. 140, using Hardware-In-The-Loop (HIL) simulation. HIL enables real-time information exchange between the actual firmware and the virtual models of the inverter and electrical grid, ensuring more precise simulation. Additionally, it allows for the emulation of different operating scenarios and the evaluation of the inverter's performance in a controlled, secure, and agile environment. Therefore, the combination of the modular firmware platform with HIL provides a flexible and efficient approach for the development and validation of new technologies, driving the advancement of photovoltaic inverters.

**Keywords:** Power Electronics. Photovoltaic Energy. Firmware. Distributed Generation. Grid-Connected Inverter.

#### LISTA DE FIGURAS

| Figura 1 – Estrutura de controle do conversor de dois estágios                            | 18 |

|-------------------------------------------------------------------------------------------|----|

| Figura 2 - Classificação dos inversores de acordo com o número de estágios de conversão   |    |

| (a) Estágio único (b) Múltiplos estágios                                                  | 19 |

| Figura 3 – Estrutura de controle do conversor de dois estágios                            | 20 |

| Figura 4 – Configuração clássica de um conversor <i>boost</i>                             | 21 |

| Figura 5 – Modelo do inversor <i>full-bridge</i>                                          | 22 |

| Figura 6 – Topologias de inversores <i>full-bridge</i> modificadas                        | 23 |

| Figura 7 – Topologias de inversor NPC (a) Topologia clássica (b) Topologia tipo T         | 24 |

| Figura 8 – Topologias de filtro de saída.                                                 | 24 |

| Figura 9 – Técnicas de amortecimento passivo                                              | 25 |

| Figura 10 – Representação da plataforma de testes em HIL                                  | 28 |

| Figura 11 – Topologia do circuito de potência utilizado                                   | 29 |

| Figura 12 – Circuito equivalente do conversor <i>boost</i>                                | 30 |

| Figura 13 – Etapas de operação do conversor boost. (a) Primeira etapa de operação. (b)    |    |

| Segunda etapa de operação                                                                 | 31 |

| Figura 14 – Representação do fluxo de potência no barramento CC                           | 33 |

| Figura 15 – Circuito composto pelo inversor e filtro de saída                             | 34 |

| Figura 16 – Circuito equivalente para modelagem                                           | 34 |

| Figura 17 – Gráfico de variação da indutância                                             | 36 |

| Figura 18 – Diagrama de bode para diferentes valores de $R_d$                             | 39 |

| Figura 19 – Estrutura básica do PLL                                                       | 39 |

| Figura 20 – Estrutura do SOGI-PLL                                                         | 40 |

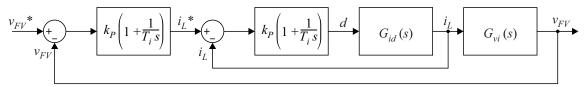

| Figura 21 – Resposta em frequência do controle de corrente em malha aberta                | 42 |

| Figura 22 – Curvas características do painel de 460 W                                     | 43 |

| Figura 23 – Algoritmo de rastreamento de ponto de operação de potência                    | 44 |

| Figura 24 – Algoritmo de LPPT                                                             | 44 |

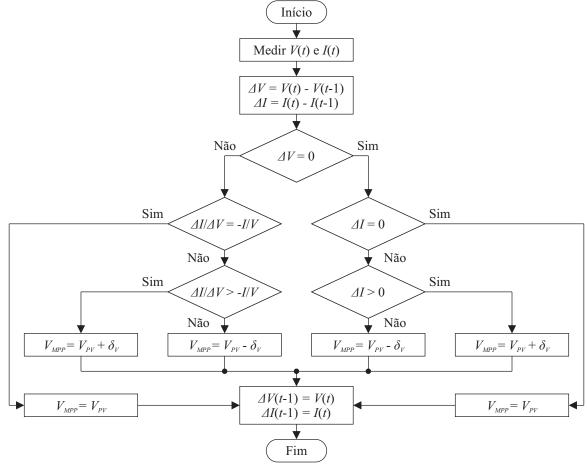

| Figura 25 – Algoritmo de MPPT                                                             | 46 |

| Figura 26 – Estrutura de controle do <i>boost</i>                                         | 47 |

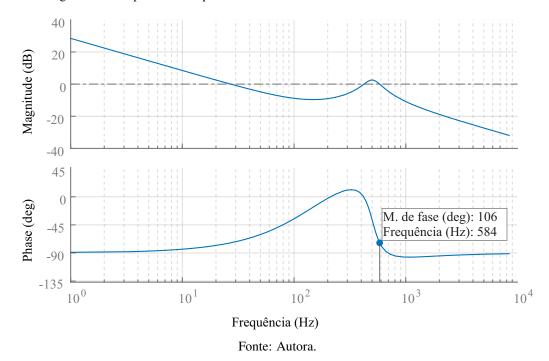

| Figura 27 – Resposta em frequência de malha aberta do controle de corrente do boost       | 48 |

| Figura 28 – Resposta em frequência de malha aberta do controle de tensão do <i>boost.</i> | 49 |

| Figura 29 – Estrutura de controle do barramento CC                                        | 49 |

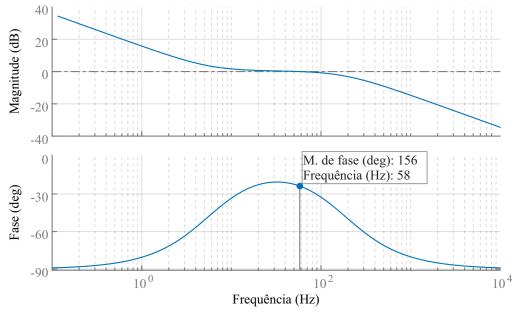

| Figura 30 – Resposta em frequência de malha aberta do controle do barramento CC           | 50 |

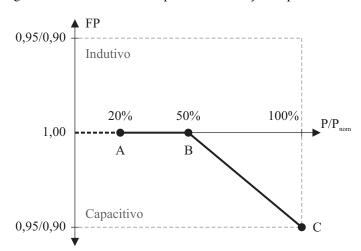

| Figura 31 – Curva do fator de potência em função da potência ativa                        | 51 |

| Figura 32 – Curva de potência por variação de frequência                                  | 53 |

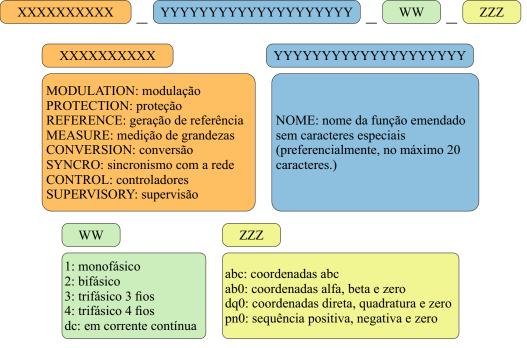

| Figura 33 – Padronização para o nome das funções                                          | 56 |

| Figura 34 – Padronização para o nome das funções.                                         | 56 |

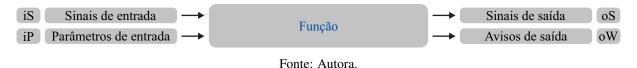

| Figura 35 – Estrutura de entradas e saídas.                                               | 57 |

|-------------------------------------------------------------------------------------------|----|

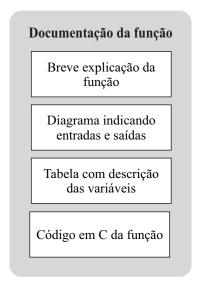

| Figura 36 – Documentação das funções.                                                     | 58 |

| Figura 37 – Estrutura de controle implementada.                                           | 59 |

| Figura 38 – Representação da função de sincronismo com a rede                             | 60 |

| Figura 39 – Representação da função de de geração de corrente de referência               | 62 |

| Figura 40 – Representação da função de geração de corrente de referência                  | 63 |

| Figura 41 – Representação da função de rastreamento de ponto de operação de potência.     | 64 |

| Figura 42 – Representação da função de rastreamento decontrole do conversor <i>boost.</i> | 65 |

| Figura 43 – Representação da função de controle do barramento CC                          | 66 |

| Figura 44 – Representação da função de controle de FP                                     | 67 |

| Figura 45 – Representação da função de proteção contra variações de tensão                | 68 |

| Figura 46 – Representação da função de proteção contra variações de frequência            | 70 |

| Figura 47 – Representação da função de controle de potência em sobrefrequência            | 71 |

| Figura 48 – Potência do MPPT diante a variações de radiação. (a) Método de condutância    |    |

| Incremental. (b) Método Perturba e Observa.                                               | 72 |

| Figura 49 – Potência do MPPT diante a variações de temperatura. (a) Método de condu-      |    |

| tância Incremental. (b) Método Perturba e Observa                                         | 72 |

| Figura 50 – Setup de testes usando o Typhoon HIL.                                         | 74 |

| Figura 51 – Circuito simulado no Typhoon HIL.                                             | 74 |

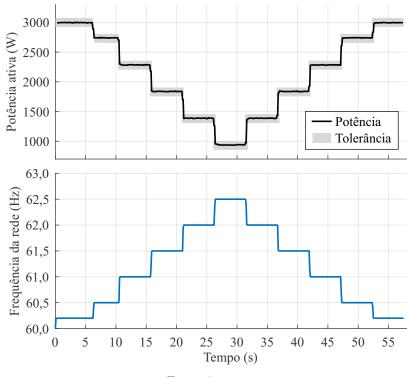

| Figura 52 – Resultado do ensaio de fator de potência em relação a potência ativa          | 79 |

| Figura 53 – Resultado do teste de determinação do nível de desconexão por subtensão       | 80 |

| Figura 54 – Resultado do teste de determinação do tempo de desconexão por subtensão       | 80 |

| Figura 55 – Resultado do teste de determinação do nível de desconexão por sobretensão.    | 81 |

| Figura 56 – Resultado do teste de determinação do tempo de desconexão por sobretensão.    | 81 |

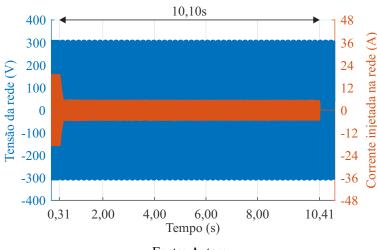

| Figura 57 – Resultado do teste de determinação do nível de desconexão por subfrequência.  | 82 |

| Figura 58 - Resultado do teste de determinação do tempo de desconexão por subfrequên-     |    |

| cia                                                                                       | 83 |

| Figura 59 – Resultado do testes de determinação do nível de desconexão por sobrefrequên-  |    |

| cia                                                                                       | 83 |

| Figura 60 – Tempo de desconexão por sobrefrequência.                                      | 84 |

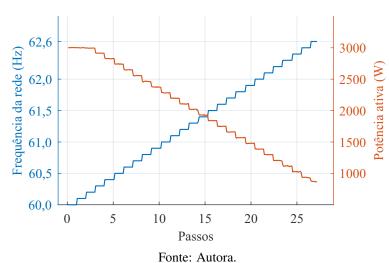

| Figura 61 – Resultado do teste de controle de potência subfrequência                      | 85 |

| Figura 62 – Resultado do teste de controle de potência sobrefrequência                    | 86 |

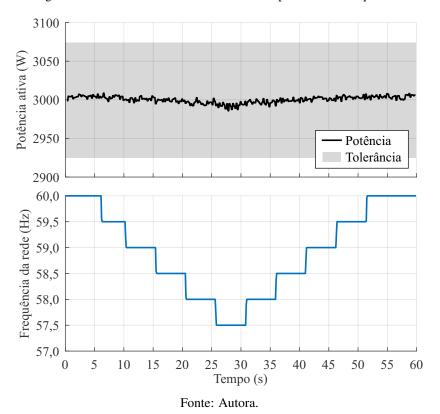

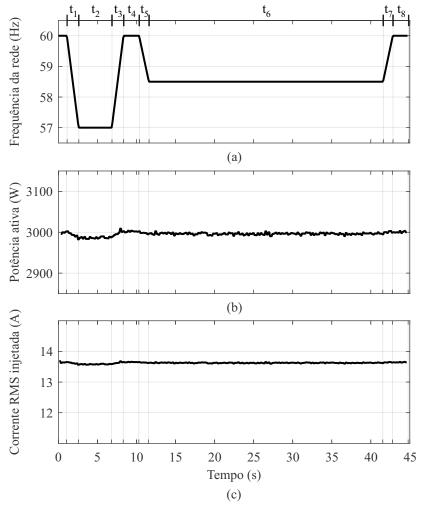

| Figura 63 – Resultado do teste de imunidade a variações de subfrequência (a) Valor de     |    |

| frequência que o inversor é submetido. (b) Comportamento da potência do                   |    |

| inversor. (c) Comportamento da corrente do inversor.                                      | 87 |

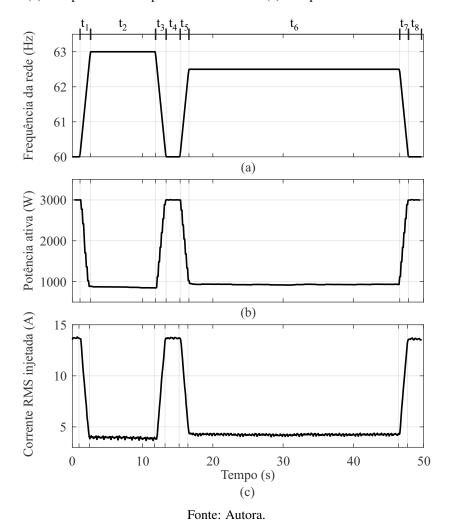

| Figura 64 – Resultado do teste de imunidade a variações de sobrefreqência (a) Valor de    |    |

| frequência que o inversor é submetido. (b) Comportamento da potência do                   |    |

| inversor. (c) Comportamento da corrente do inversor.                                      | 88 |

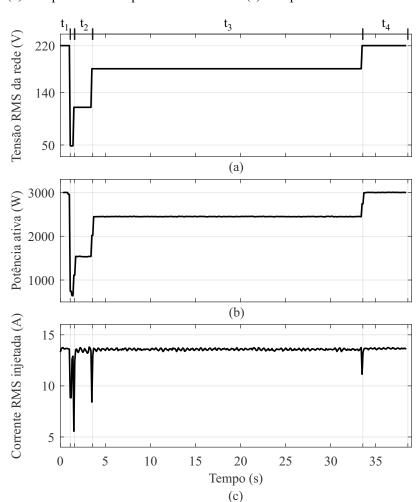

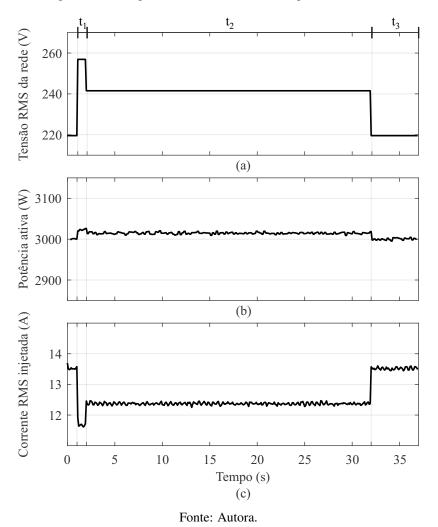

| Figura 65 – Resultado do teste de imunidade a variações de subtensão (a) Valor de tensão  |    |

| que o inversor é submetido. (b) Comportamento da potência do inversor. (c)                 |    |

|--------------------------------------------------------------------------------------------|----|

| Comportamento da corrente do inversor                                                      | 90 |

| Figura 66 – Resultado do teste de imunidade a variações de sobretensão (a) Valor de tensão |    |

| que o inversor é submetido. (b) Comportamento da potência do inversor. (c)                 |    |

| Comportamento da corrente do inversor                                                      | 91 |

#### LISTA DE TABELAS

| Tabela | 1 – Parâmetros do Sistema.                                                | 30 |

|--------|---------------------------------------------------------------------------|----|

| Tabela | 2 – Parâmetros para projeto do conversor <i>boost</i>                     | 36 |

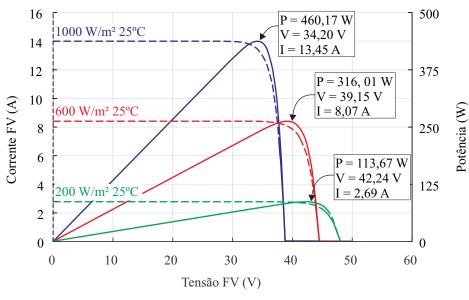

| Tabela | 3 – Parâmetros do módulo FV de 460 <i>W</i>                               | 43 |

| Tabela | 4 – Ajustes para a proteção de subtensão                                  | 52 |

| Tabela | 5 – Ajustes para a proteção de sobretensão                                | 52 |

| Tabela | 6 – Ajustes para a proteção de subfrequência                              | 53 |

| Tabela | 7 – Ajustes para a proteção de sobrefrequência                            | 53 |

| Tabela | 8 – Nome padrão para variáveis.                                           | 58 |

| Tabela | 9 – Operação do fator de potência.                                        | 68 |

| Tabela | 10 – Resultado do ensaio de injeção de corrente CC                        | 75 |

| Tabela | 11 – Limites de distorção harmônica individual                            | 76 |

| Tabela | 12 – Resultado do ensaio de THD.                                          | 76 |

| Tabela | 13 – Resultado do ensaio de harmônicas individuais                        | 77 |

| Tabela | 14 – Resultado do ensaio de fator de potência fixo                        | 78 |

| Tabela | 15 – Resultado do ensaio de fator de potência em relação a potência ativa | 78 |

| Tabela | 16 – Requisitos para o ensaio de imunidade a variações de frequência      | 86 |

| Tabela | 17 – Intervalos de tempo de aplicação dos níveis de subfrequência         | 87 |

| Tabela | 18 – Intervalos de tempo de aplicação de níveis de sobrefrequência        | 89 |

| Tabela | 19 – Requisitos para o ensaio de imunidade a variações de tensão          | 89 |

| Tabela | 20 – Intervalos de tempo de aplicação de níveis de subtensão              | 90 |

| Tabela | 21 – Intervalos de tempo de aplicação de níveis de subtensão.             | 91 |

## LISTA DE QUADROS

| Quadro 1 – Variáveis utilizadas na função de sincronismo.                                | 60 |

|------------------------------------------------------------------------------------------|----|

| Quadro 2 – Variáveis utilizadas na função de geração de referência de corrente           | 62 |

| Quadro 3 – Variáveis utilizadas na função de controle de corrente do inversor            | 63 |

| Quadro 4 - Variáveis utilizadas na função de rastreamento de ponto de operação de potên- |    |

| cia                                                                                      | 64 |

| Quadro 5 – Variáveis utilizadas na função de controle do conversor <i>boost</i>          | 65 |

| Quadro 6 – Variáveis utilizadas na função de controle do barramento CC                   | 66 |

| Quadro 7 – Variáveis utilizadas na função de de FP.                                      | 67 |

| Quadro 8 – Variáveis utilizadas na função de proteção contra variações de tensão         | 69 |

| Quadro 9 – Variáveis utilizadas na função de proteção contra variações de frequência     | 70 |

| Quadro 10 – Variáveis utilizadas na função de controle de potência em sobrefrequência    | 71 |

# SUMÁRIO

| 1       | INTRODUÇÃO                                                        | 16 |

|---------|-------------------------------------------------------------------|----|

| 1.1     | OBJETIVO GERAL                                                    | 18 |

| 1.2     | OBJETIVOS ESPECÍFICOS                                             | 18 |

| 2       | REVISÃO BIBLIOGRÁFICA                                             | 19 |

| 2.1     | ESTRUTURA DE POTÊNCIA E CONTROLE DE INVERSORES CONECTA-           |    |

|         | DOS À REDE                                                        | 19 |

| 2.2     | CONVERSOR CC-CC                                                   | 21 |

| 2.3     | TOPOLOGIAS DE INVERSORES NÃO ISOLADOS                             | 22 |

| 2.3.1   | Inversores Full-Bdridge                                           | 22 |

| 2.3.2   | Inversores NPC                                                    | 23 |

| 2.4     | FILTRO DE SAÍDA                                                   | 24 |

| 2.5     | RESOLUÇÕES BRASILEIRAS REFERENTES À CERTIFICAÇÃO DE IN-           |    |

|         | VERSORES                                                          | 26 |

| 2.5.1   | INMETRO Portaria nº 140                                           | 26 |

| 2.6     | HARDWARE-IN-THE-LOOP                                              | 27 |

| 3       | ESTUDO DE CASO: FIRMWARE PARA INVERSOR FOTOVOLTAICO               |    |

|         | CONECTADO À REDE                                                  | 29 |

| 3.1     | TOPOLOGIA                                                         | 29 |

| 3.2     | MODELOS DINÂMICOS DOS ESTÁGIOS DE CONVERSÃO                       | 30 |

| 3.2.1   | Estágio de Entrada                                                | 30 |

| 3.2.2   | Barramento CC                                                     | 33 |

| 3.2.3   | Estágio de Saída                                                  | 33 |

| 3.3     | DIMENSIONAMENTO DOS ELEMENTOS PASSIVOS DOS CONVERSORES            | 36 |

| 3.3.1   | Estágio de entrada                                                | 36 |

| 3.3.2   | Barramento CC                                                     | 37 |

| 3.3.3   | Estágio de saída                                                  | 37 |

| 3.4     | SISTEMA DE CONTROLE, PROTEÇÃO E GERAÇÃO DE REFERÊNCIAS            | 39 |

| 3.4.1   | Geração de referências de sincronismo com a rede                  | 39 |

| 3.4.2   | Gerador de referência de corrente do estágio de saída             | 40 |

| 3.4.3   | Controlador de corrente do estágio de saída                       | 41 |

| 3.4.4   | Gerador de referência para seguimento de ponto de máxima potência | 42 |

| 3.4.4.1 | Método de LPPT                                                    | 44 |

| 3.4.4.2 | Método de MPPT                                                    | 45 |

| 3.4.5   | Controlador de tensão do estágio de entrada                       | 46 |

| 3.4.5.1 | Controlador da malha interna do estágio de entrada                | 47 |

| 3 4 5 2 | Controlador da malha externa do estágio de entrada                | 48 |

| 3.4.6   | Controlador de tensão do barramento CC                                  | 49        |

|---------|-------------------------------------------------------------------------|-----------|

| 3.4.7   | Funções de Proteção e de Suporte à Rede                                 | 50        |

| 3.4.7.1 | Ajuste do Fator de Potência                                             | 50        |

| 3.4.7.2 | Proteção de Sobretensão e Subtensão                                     | 52        |

| 3.4.7.3 | Proteção de Sobrefrequência e Subfrequência                             | 52        |

| 3.4.7.4 | Controle de Potência em Sobrefrequência                                 | 53        |

| 3.5     | CONSIDERAÇÕES FINAIS                                                    | 54        |

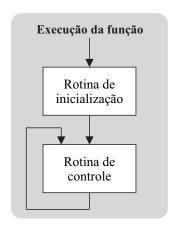

| 4       | METODOLOGIA PROPOSTA PARA ESTRUTURAÇÃO DE FIRMWARE                      | 55        |

| 4.1     | PADRONIZAÇÃO DE ESTRUTURA DO PROGRAMA                                   | 55        |

| 4.2     | PADRONIZAÇÃO PARA O NOME DAS FUNÇÕES                                    | 56        |

| 4.3     | PADRONIZAÇÃO DE REPRESENTAÇÃO DE VARIÁVEIS DE ENTRADA E                 |           |

|         | SAÍDA                                                                   | 57        |

| 4.4     | METODOLOGIA PARA DOCUMENTAÇÃO DAS FUNÇÕES                               | 58        |

| 4.5     | APLICAÇÃO DA METODOLOGIA PROPOSTA PARA GERAÇÃO DE FIRMWAI               | RE        |

|         | DO ESTUDO DE CASO PROPOSTO                                              | 59        |

| 4.5.1   | Implementação da função de gerador de referências de sincronismo com a  |           |

|         | rede                                                                    | 60        |

| 4.5.2   | Implementação da função de gerador de referência de corrente do estágio |           |

|         | de saída                                                                | 62        |

| 4.5.3   | Implementação da função de controlador de corrente do estágio de saída  | 62        |

| 4.5.4   | Implementação da Função de gerador de referência para seguimento de     |           |

|         | ponto de máxima potência                                                | 64        |

| 4.5.5   | Implementação da Função do controlador de tensão do estágio de entrada  | 65        |

| 4.5.6   | Implementação da função de controle do barramento CC                    | 66        |

| 4.5.7   | Implementação da Função de controle de fator de potência                | 67        |

| 4.5.8   | Implementação da Função de Proteção contra Variação de Tensão           | 68        |

| 4.5.9   | Implementação da Função de Proteção contra Variação de Frequência       | 69        |

| 4.5.10  | Implementação da Função em Linguagem C - Controle de Potência em So-    |           |

|         | brefrequência                                                           | <b>70</b> |

| 4.6     | VALIDAÇÃO DA MODULARIDADE DAS FUNÇÕES                                   | 71        |

| 4.7     | CONSIDERAÇÕES FINAIS                                                    | 73        |

| 5       | RESULTADOS EXPERIMENTAIS                                                | <b>74</b> |

| 5.1     | TESTE 1: INJEÇÃO DE CORRENTE CC NA REDE ELÉTRICA                        | 75        |

| 5.2     | TESTE 2: LIMITE DE DISTORÇÃO HARMÔNICA DE CORRENTE                      | 76        |

| 5.3     | TESTE 3: FATOR DE POTÊNCIA                                              | 77        |

| 5.4     | TESTE 4: RELAÇÃO POTÊNCIA ATIVA X FATOR DE POTÊNCIA                     | 78        |

| 5.5     | TESTE 5: DESCONEXÃO POR SUBTENSÃO E SOBRETENSÃO                         | 79        |

| 5.5.1   | Desconexão por Subtensão                                                | <b>79</b> |

| 5.5.2   | Desconexão por Sobretensão                                              | 81        |

| 5.6    | TESTE 6: DESCONEXÃO POR SUBFREQUÊNCIA E SOBREFREQUÊNCIA. | 82        |

|--------|----------------------------------------------------------|-----------|

| 5.6.1  | Desconexão por Subfrequência                             | 82        |

| 5.6.2  | Desconexão por Sobrefrequência                           | 83        |

| 5.7    | TESTE 7: CONTROLE EM SUBFREQUÊNCIA                       | 84        |

| 5.8    | TESTE 8: CONTROLE EM SOBREFREQUÊNCIA                     | 85        |

| 5.9    | TESTE 9: IMUNIDADE À VARIAÇÕES DE FREQUÊNCIA             | 86        |

| 5.9.1  | Imunidade à Variações de Subfrequência                   | <b>87</b> |

| 5.9.2  | Imunidade à Variações de Sobrefrequência                 | 88        |

| 5.10   | TESTE 10: IMUNIDADE À VARIAÇÕES DE TENSÃO                | 89        |

| 5.10.1 | Imunidade à Variações de Subtensão                       | 89        |

| 5.10.2 | Imunidade à Variações de Sobretensão                     | 90        |

| 5.11   | CONSIDERAÇÕES FINAIS                                     | 92        |

| 6      | CONCLUSÃO                                                | 93        |

| 6.1    | SUGESTÃO DE TRABALHOS FUTUROS                            | 94        |

| 6.2    | ARTIGOS PUBLICADOS                                       | 94        |

|        | REFERÊNCIAS BIBLIOGRÁFICAS                               | 95        |

|        | APÊNDICE A – DOCUMENTAÇÃO DA FUNÇÃO DE SINCRONISMO       | 99        |

|        |                                                          |           |

## 1 INTRODUÇÃO

Há quase 150 anos a energia elétrica é fornecida aos consumidores através de geradores síncronos localizados em grandes centrais geradoras. No entanto, a rede elétrica está passando por uma significativa transição. Nas últimas décadas, observou-se um aumento expressivo na utilização de inversores de potência, principalmente devido as fontes de energia renováveis que utilizam esses equipamentos para se conectarem à rede (TUCKEY; ROUND, 2022).

A integração das fontes de energia solar e eólica à matriz energética ocorre em parte através da geração distribuída (GD). A GD é caracterizada pela geração local de pequena escala, descentralizada e ocorre em grande parte, por meio de fontes de energia renováveis (SMIL, 2019). As vantagens desse tipo de geração incluem a redução dos impactos ambientais, a partir do uso de fontes renováveis, além de diversificar a matriz energética e diminuir as perdas de transmissão (SMIL, 2019) (KHAN et al., 2020).

A matriz elétrica brasileira é predominantemente renovável, em virtude da abundância de recursos naturais. De acordo com a Empresa de Pesquisa Energética (EPE) no ano de 2022, cerca de 86,1% da eletricidade utilizada no país foi gerada através de fontes renováveis. Dessa parcela 61,9% é referente a geração hidráulica, 11,8% eólica, 8,0% biomassa e 4,4% solar (EPE, 2023).

Ainda de acordo com a EPE a capacidade instalada de geração através da fonte solar em 2022 teve um aumento de 82,4% em relação ao ano de 2021. Sendo a fonte de energia elétrica que mais cresceu no último ano. Além disso, a micro e mini GD em 2022 aumentou 87,8% em relação a 2021, onde a energia solar fotovoltaica (FV) representou 94,3% da micro e mini GD instalada, sendo a principal fonte responsável pelo aumento da GD (EPE, 2023).

Em virtude desse alto nível de inserção de sistemas FV conectados à rede, a integração dos recursos baseados em inversores (RBI) no sistema de energia tem experimentado um rápido crescimento. O aprimoramento desses equipamentos é essencial para garantir a compatibilidade e integração com outros sistemas, bem como assegurar a confiabilidade, eficiência e segurança da rede elétrica e dos equipamentos conectados a ela.

Nesse sentido, há a necessidade de padronizar os inversores FV (FIGUEIRA et al., 2015). A Associação Brasileira de Normas Técnicas (ABNT), definiu os requisitos mínimos para sistemas FV interligados à rede, através da NBR 16149, que estabelece as exigências para a interface de conexão de inversores FV com o sistema elétrico de distribuição. De acordo com essa normativa, o inversor deve ser capaz de identificar desvios dos padrões de qualidade de energia e cessar o fornecimento em casos de desconformidade (ABNT, 2013b).

Ainda a ABNT estabelece, na NBR 16150, os procedimentos de ensaios que verificam se os inversores a serem conectados à rede estão em conformidade com os requisitos propostos pela NBR 16149 (ABNT, 2013a). No ano de 2014 foi publicada pelo Instituto Nacional de Metrologia, Qualidade e Tecnologia (INMETRO) a portaria n° 357, que tornava obrigatório

que todos os inversores conectados à rede com potência nominal de até 10 kW estivessem em conformidade com os limites das normas da ABNT NBR 16149 e NBR 16150.

Em março de 2022 foi publicada pelo INMETRO a portaria nº 140 que revogou a portaria nº 357, passando a regulamentar os requisitos de avaliação da conformidade para equipamentos de geração, condicionamento e armazenamento de energia elétrica em sistemas FV, tornando obrigatória a certificação de inversores FV conectados à rede com potência nominal de até 75 kW.

A atualização das regulamentações demonstra o compromisso das autoridades em garantir a integração eficiente e segura dos RBI na rede elétrica, diante do rápido avanço da tecnologia de inversores FV. Atualizações regulatórias permitem o aprimoramento de funcionalidades dos inversores, de forma que eles ofereçam suporte à rede, contribuindo para a estabilidade e segurança do sistema elétrico.

À medida que as regulamentações são atualizadas, os testes que estes equipamentos estão sujeitos, são atualizados. Sendo necessário o ajuste do *firmware* dos inversores para que o equipamento esteja em conformidade com a regulamentação atualizada.

Nesse sentido, esse trabalho propõe o desenvolvimento de um *firmware* que permite testar leis de controle de inversores FV. O *firmware* desenvolvido é responsável pelo controle e funcionamento adequado do inversor e tem a proposta de ser modular. Dessa forma, é possível substituir e ajustar diferentes módulos do controle, sem que ele interfira no restante do funcionamento do inversor, eliminando a necessidade de reescrever ou adaptar todo o código do *firmware*. Ao dividir o *firmware* em módulos independentes, diferentes funcionalidades e leis de controle podem ser testadas e comparadas de maneira simples e independente, possibilitando um processo de desenvolvimento mais eficiente.

Ainda, a estrutura modular facilita a manutenção do *firmware* a longo prazo. Quando for necessário a atualização de uma função específica, é possível alterar apenas o módulo em questão sem afetar outras partes do código. Além disso, essa abordagem permite a reutilização de módulos para futuros projetos ou atualizações.

A implementação desse *firmware* modular tem potencial para acelerar o processo de desenvolvimento e validação de novas leis de controle para inversores FV, além de adaptá-los a diferentes condições e requisitos que possam surgir.

O *firmware* foi validado a partir de ensaios normatizados da portaria do INMETRO nº 140, utilizando *hardware-in-the-loop* (HIL). O HIL permite a troca de informações em tempo real entre o *firmware* real e o modelo virtual do inversor e da rede elétrica, garantindo uma simulação mais precisa. Além disso é possível emular diferentes cenários de operação e avaliar o desempenho do inversor em um ambiente controlado e seguro e de forma ágil.

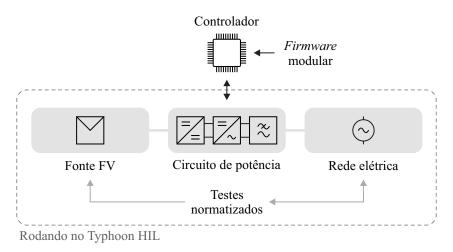

A Figura 1 apresenta a plataforma de testes utilizadas nessa dissertação. A plataforma é composta pelo *firmware* modular que é inserido em um controlador físico. Esse conjunto de controlador e *firmware* conduzem a operação do circuito de potência do inversor. A avaliação da conformidade com a portaria do INMETRO nº 140 é feita a partir das rotinas de testes

desenvolvida por Menegazzo (2023).

Figura 1 – Estrutura de controle do conversor de dois estágios.

Fonte: Autora.

A proposta de *firmware* modular em conjunto com o HIL oferece uma abordagem flexível e eficiente para o desenvolvimento e validação de novas tecnologias, impulsionando o avanço de inversores FV.

#### 1.1 OBJETIVO GERAL

O objetivo central dessa dissertação é criar um *firmware* modular para um inversor FV, de forma que cada função seja desenvolvida de forma independente do restante do código. A principal vantagem dessa abordagem é permitir que diferentes funcionalidades sejam testadas individualmente, sem comprometer o funcionamento geral do inversor.

#### 1.2 OBJETIVOS ESPECÍFICOS

Para atingir o objetivo geral descrito são abordados os seguintes objetivos específicos:

- definir diretrizes para padronizar o uso dos módulos do *firmware*;

- projeto e dimensionamento de um inversor monofásico para realizar os testes do *firmware* desenvolvido;

- desenvolver as funcionalidades necessárias para conectar o inversor na rede;

- desenvolver os códigos do firmware modular; e

- avaliar o desempenho do *firmware* desenvolvido a partir de testes normatizados utilizando HIL.

#### 2 REVISÃO BIBLIOGRÁFICA

Este capítulo apresenta a revisão bibliográfica que abrange tópicos fundamentais para a compreensão do trabalho proposto. Inicialmente, na seção 2.1 é apresentada a estrutura de potência e de controle de inversores conectados à rede de dois estágios. Nas seções seguintes são abordados os dois estágios de conversão do inversor, o estágio CC-CC (seção 2.2) e o estágio CC-CA (seção 2.3), onde são destacadas as topologias mais utilizadas em sistemas conectados à rede. Na seção 2.4 são apresentadas as topologias de filtros de saída utilizadas para fazer a interface entre o inversor e a rede elétrica, utilizado para melhorar a qualidade da corrente produzida.

A seção 2.5 discorre sobre as regulamentações brasileiras referentes a certificação de inversores com foco na Portaria nº 140 do INMETRO. Por fim, a seção 2.6 apresenta o conceito referente a HIL e plataforma de teste utilizada para a validação do trabalho é apresentada.

# 2.1 ESTRUTURA DE POTÊNCIA E CONTROLE DE INVERSORES CONECTADOS À REDE

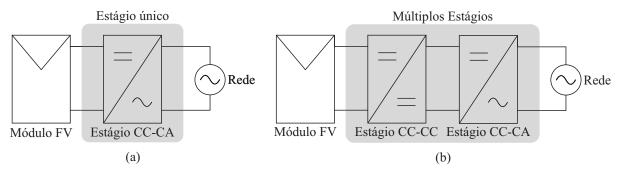

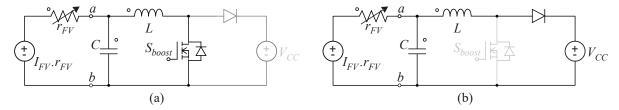

Os inversores conectados à rede podem ser classificados em duas categorias de acordo com o número de estágios de processamento de potência utilizados: inversores de estágio único, Figura 2 (a) e inversores de múltiplos estágios, Figura 2 (b) (ZEB et al., 2018).

Figura 2 – Classificação dos inversores de acordo com o número de estágios de conversão (a) Estágio único (b) Múltiplos estágios.

Fonte: Adaptado de Zeb et al. (2018).

Os inversores de estágio único apresentam a vantagem de possuir perdas de conversão reduzidas e menor custo, uma vez que todo o processo é concentrado em apenas um conversor (GONçALVES, 2020). Eles são utilizados principalmente para elevadas potências em que é feita a associação de uma grande quantidade de painéis FV em série para elevar o nível de tensão.

Nos inversores de estágio único todas as funções necessárias para a operação do inversor

são realizadas por um único conversor. Essas funções são: controle de corrente, controle do fluxo de potência, rastreamento do ponto de máxima potência (MPPT) e sincronismo com a rede (GONçALVES, 2020). Isso faz com que a complexidade do sistema de controle seja alta e reduz o grau de liberdade (GONçALVES, 2020).

Os inversores de múltiplos estágios são aplicados para potências mais baixas ou inversores de múltiplas *strings*, onde o número de painéis associados em série não é suficiente para assegurar o nível de tensão mínimo do barramento CC. Dessa forma o primeiro estágio é composto por um conversor CC-CC que faz a adequação da tensão do barramento e o segundo estágio é composto por um conversor que faz a inversão de corrente contínua para corrente alternada.

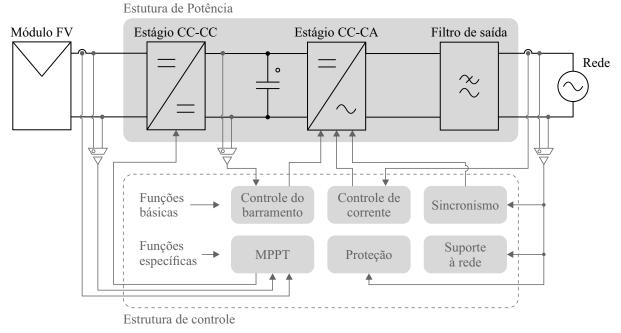

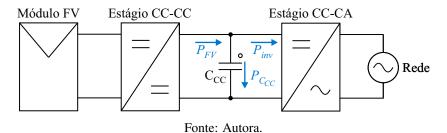

Com mais de um estágio de conversão as funções de operação do inversor são divididas entre os estágios, possibilitando uma maior flexibilidade de controle. A Figura 3 apresenta a estrutura de potência de um conversor de dois estágios, juntamente com a arquitetura de controle.

Figura 3 – Estrutura de controle do conversor de dois estágios.

Fonte: Autora.

O controlador inclui as funções básicas e específicas. As funções básicas são as necessárias para garantir a operação adequada do inversor, incluindo as funções de sincronismo com a rede, controle do barramento CC e o controle da corrente injetada. As funções específicas são implementadas visando atender os requisitos normativos referente a conexão com a rede e rastrear o ponto de máxima potência dos módulos FV.

#### 2.2 CONVERSOR CC-CC

Os módulos FV são constantemente submetidos a diferentes níveis de radiação e temperatura. Para cada combinação desses fatores há um valor de corrente e tensão específico que gera a máxima potência do módulo. Com o objetivo de maximizar o potencial energético dos sistemas FV é necessário fazer o rastreamento do melhor ponto de operação. Esse rastreamento é, na maioria dos casos, realizados pelo conversor CC-CC empregado.

Adicionalmente, em sistemas de baixa potência, os arranjos FV produzem tensões reduzidas, tornando essencial o uso de conversores CC-CC elevadores para assegurar a tensão mínima requerida no barramento CC (GONçALVES, 2020).

Entre as topologias de conversores isolados pode-se citar os conversores flyback, forward e push-pull. Essas topologias requerem o emprego de transformadores, que oferecem desvantagens como elevadas perdas no núcleo, alto estresse de tensão sobre os interruptores, problema de interferência eletromagnética além do elevado peso e volume (CARVALHO, 2018).

Dessa forma, em aplicações FV em que a isolação galvânica não é necessária, os conversores não isolados se toram alternativas mais vantajosas (CARVALHO, 2018). Eles conseguem alcançar elevado ganho de tensão com maior eficiência, além de serem mais compactos (JALIL-ZADEH et al., 2018). Dentre as topologias de conversores elevadores de tensão não isolados, destacam-se o conversor boost, buck-boost, sepic, cuk e zeta.

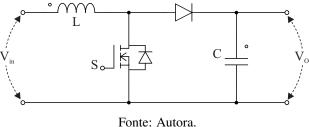

Em aplicações de baixa potência, o conversor boost é utilizado, principalmente devido a simplicidade de modelagem, projeto e implementação, decorrentes ao baixo número de dispositivos empregados (FOROUZESH et al., 2017). A configuração clássica de um conversor boost é apresentada na Figura 4.

Figura 4 – Configuração clássica de um conversor boost.

O conversor *boost* possui característica de fonte de corrente na entrada e fonte de tensão na saída. Possuindo, teoricamente, ganho de tensão infinito quando o valor da razão cíclica se aproxima de 1. No entanto, em razão das perdas de condução dos componentes o ganho de tensão, bem como a eficiência do conversor são reduzidas (SCHMITZ et al., 2015). Nesse sentido, o conversor boost é uma boa solução para aplicações que não exijam um elevado ganho de tensão.

#### 2.3 TOPOLOGIAS DE INVERSORES NÃO ISOLADOS

O inversor é o elemento principal dos sistemas de energia FV conectados à rede, cuja principal função é produzir uma corrente alternada compatível e sincronizada com a tensão da rede elétrica. O desenvolvimento das tecnologias para inversores busca principalmente o aumento da eficiência, bem como a redução de custos e o prolongamento da vida útil (TE-ODORESCU; LISERRE; RODRIGUEZ, 2011). Nesse sentido, há uma vasta quantidade de topologias utilizadas no mercado, sendo as principais delas baseadas nas topologias *full-bridge* e NPC (*Neutral Point Clamped*).

#### **2.3.1** Inversores *Full-Bdridge*

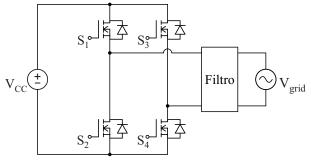

A estrutura do inversor *full-bridge* é mostrada na Figura 5. O circuito é formado por dois braços inversores compostos por um par de chaves que são comandadas de maneira complementar (MARTINS; BARBI, 2008).

Figura 5 – Modelo do inversor *full-bridge*.

Fonte: Autora.

Com o intuito de melhorar a eficiência da topologia são feitas modificações, geralmente com a inclusão de uma ou duas chaves. Exemplos de topologias modificadas do inversor *full-bridge* são a topologia H5, H6, Heric e topologia *full-bridge* com desvio CC. As diferentes topologias são apresentadas na Figura 6.

FV  $C_{FV}$   $C_{FV}$

Figura 6 – Topologias de inversores *full-bridge* modificadas.

Fonte: Autora.

Essa inclusão tem o objetivo de desconectar o módulo FV da rede elétrica durante o estado de tensão zero, isso reduz as perdas geradas por eventuais correntes de fuga (SREYA; RAJESH, 2022).

#### 2.3.2 Inversores NPC

O NPC é uma topologia de inversor multinível de alta eficiência. Com ele é possível produzir tensões com uma quantidade de níveis de tensão proporcional ao número de capacitores utilizados no barramento CC. As perdas nesse inversor são reduzidas, uma vez que, durante o estágio de tensão zero, não há conexão entre o módulo FV da rede elétrica (TEODORESCU; LISERRE; RODRIGUEZ, 2011). No entanto, requer o dobro da tensão de barramento em relação as topologias *full-bridge*.

A topologia NPC, na maioria dos casos, pode assumir duas diferentes configurações. A configuração clássica é mostrada na Figura 7 (a) e a configuração tipo T é mostrada na Figura 7 (b).

$V_{CC} = C_{FV1} - C_{FV1} - C_{FV2} - C_{FV$

Figura 7 – Topologias de inversor NPC (a) Topologia clássica (b) Topologia tipo T.

Fonte: Autora.

O conversor NPC possui performance similar comparado com as topologias H5 e Heric. Possuindo como desvantagem o desbalanceamento da perda entre os semicondutores. Essa desvantagem é contornada pelo conversor tipo T, que ainda possui perdas reduzidas em relação ao NPC clássico, uma vez que o conversor clássico apresenta dispositivos semicondutores em série em algumas etapas de operação (TEODORESCU; LISERRE; RODRIGUEZ, 2011).

#### 2.4 FILTRO DE SAÍDA

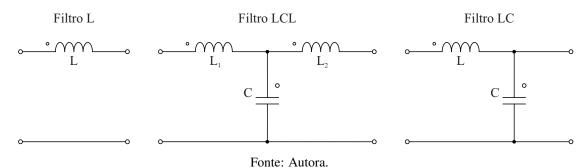

O filtro de saída é o elemento responsável pela interface entre o inversor e a rede elétrica. Ele se torna necessário para minimizar o conteúdo harmônico gerado pelo PWM e, dessa forma, melhorar a qualidade da corrente injetada na rede (QIAN et al., 2021). De maneira geral, o filtro de saída deve possuir característica indutiva, uma vez que a saída do conversor e a rede elétrica tem características de fonte de tensão (WU et al., 2022). Nesse sentido, as topologias de filtros mais utilizadas estão o filtro L, composto apenas por um indutor, e o filtro LCL, composto por dois indutores e um capacitor (COSTA; PINTO; SILVA, 2022). Em alguns casos é considerado um filtro LC, em que, combinado com a impedância da rede, forma um filtro LCL. A Figura 8 mostra as três topologias de filtro citadas.

Figura 8 – Topologias de filtro de saída.

O filtro L é um filtro de primeira ordem, com uma atenuação de  $-20 \, dB/dec$ . A vantagem dele está na simplicidade, tanto de modelagem como de implementação. No entanto, requer uma alta frequência de comutação das chaves para que a potência reativa seja pequena, caso contrário resulta em um indutor muito grande, aumentando o tamanho e custo do sistema (MARTINS et al., 2018).

O filtro LCL, por outro lado, proporciona uma atenuação de  $-60 \ dB/dec$  em alta frequência, oferecendo uma maior atenuação das harmônicas sem haver o aumento da potência reativa (QIAN et al., 2021). Dessa forma, é possível produzir filtros de menores dimensões e peso, que refletem em um menor custo. Além disso, a indutância de saída garante uma maior robustez diante de variações da rede. Por estas razões, o filtro LCL se apresenta como uma opção mais interessante para inversores conectados à rede (HAN et al., 2019).

A interação entre os elementos indutivos e capacitivos gera um efeito de ressonância indesejada que causa instabilidade do sistema. Nesse sentido, a utilização do filtro LCL requer estratégias para atenuar a ressonância produzida pelo filtro, o que pode tornar a implementação do filtro mais complexa. As técnicas de atenuação de ressonância podem ser feitas de forma passiva ou ativa. As técnicas passivas envolvem a inserção de um elemento resistivo em série ou paralelo com algum dos elementos do filtro, conforme apresentado na Figura 9.

Figura 9 – Técnicas de amortecimento passivo.

Fonte: Adaptado de Gomes, Cupertino e Pereira (2018).

A vantagem da utilização da técnica de amortecimento passivo é a simplicidade de implementação, além de não requerer nenhuma modificação na estratégia de controle de corrente empregada. No entanto, o método altera a atenuação do filtro e insere perdas no sistema, reduzindo a eficiência de conversão (GOMES; CUPERTINO; PEREIRA, 2018).

Os métodos de amortecimento ativo realizam modificações na estratégia de controle, de forma a obter o amortecimento em malha fechada (GOMES; CUPERTINO; PEREIRA, 2018). Exemplos de técnicas de amortecimento ativo incluem: estratégias baseadas na realimentação da corrente ou tensão do capacitor; método fundamentado em filtro *notch*; e método de retroação parcial de estados. Entretanto, a desvantagem dessas abordagens reside no aumento da complexidade do controle e na necessidade, em alguns casos, de um sensor adicional.

#### 2.5 RESOLUÇÕES BRASILEIRAS REFERENTES À CERTIFICAÇÃO DE INVERSORES

Diante do alto nível de inserção de sistemas FV conectados à rede no Brasil há a necessidade de realizar a padronização dos equipamentos, através de normas técnicas, de forma a manter a qualidade da energia gerada, bem como garantir a segurança do sistema elétrico.

No Brasil, as normas técnicas relacionadas aos sistemas de energia elétrica são elaboradas pela Agência Nacional de Energia Elétrica (ANEEL) e pela ABNT. A ANEEL é responsável pela normatização dos sistemas que abrangem a geração, transmissão e distribuição de energia, enquanto a ABNT se encarrega de normatizar a operação dos equipamentos utilizados nesses sistemas (BITENCOURT, 2021).

A ABNT publicou em 2012 a norma ABNT NBR IEC 62116 (ABNT, 2012), que aborda os procedimentos para ensaio de medidas de proteção contra ilhamento. Em 2013 foram publicadas as normas ABNT NBR 16149 (ABNT, 2013b) e ABNT NBR 16150 (ABNT, 2013a). A primeira define as exigências para a interface de conexão de inversores FV com o sistema elétrico de distribuição. Já a segunda contempla os procedimentos de ensaios que verificam se os inversores conectados à rede estão em conformidade com os requisitos propostos pela ABNT NBR 16149. Ainda o INMETRO publicou, em março de 2022, a portaria nº 140 (INMETRO, 2022), que regulamenta os requisitos de avaliação da conformidade para equipamentos de geração, condicionamento e armazenamento de energia elétrica em sistemas FV, tornando compulsória a certificação de inversores FV conectados à rede com potência nominal de até 75 kW.

#### 2.5.1 INMETRO Portaria nº 140

A portaria nº 140 de 2022 do INMETRO possui o objetivo de estabelecer as diretrizes para a regulamentação da qualidade e conformidade dos equipamentos utilizados na geração, condicionamento e armazenamento de energia elétrica em sistemas FV. Foi o principal documento consultado para o desenvolvimento das funções de proteção e suporte à rede, mais especificamente o anexo I do documento. O anexo I é responsável por definir os requisitos obrigatórios relacionados à segurança e ao desempenho do produto (INMETRO, 2022).

O regulamento aplica-se, entre outros equipamentos, a inversores com potência nominal até 75 kW, de uso em sistemas FV conectados ou não na rede elétrica, e com ou sem armazenamento de energia (INMETRO, 2022). O anexo I, da portaria nº 140, é dividido em sete seções, sendo as primeiras destinadas a apresentar o objetivo do anexo, siglas e definições utilizadas no documento.

A seção 4 do anexo I aborda os requisitos gerais que todos os equipamentos abrangidos pela norma devem seguir. Os equipamentos fabricados devem oferecer segurança aos usuários e às instalações em relação aos riscos elétricos, mecânicos e de incêndios. A seção aborta também características construtivas, proibindo a presença de arestas, bordas, cantos, saliências ou pontas afiadas que possam expor os usuários a riscos de corte ou outros ferimentos. Além disso, os equipamentos devem cumprir os limites máximos de concentração de substâncias perigosas conforme a legislação nacional em vigor. E durante o funcionamento normal, os equipamentos não podem causar interferência de rádio em sistemas de radiodifusão ou radiocomunicação vizinhos (INMETRO, 2022).

A quinta seção do anexo I aborda os requisitos técnicos para os equipamentos de geração, condicionamento e armazenamento de maneira individual. Em relação aos inversores conectados à rede, são apresentados os requisitos técnicos relacionados a operação em condições nominais de frequência e tensão, apresentando os níveis de tolerância de potência, requisitos de injeção de corrente contínua, harmônicas e fator de potência. São apresentadas as proteções necessárias dos inversores como: falha de isolação nas portas FV; corrente residual; proteção contra variações de frequência e tensão; e proteção contra ilhamento. Além disso, são descritas as funcionalidades de suporte a rede como: controle de potência em sobrefrequência; controle de potência em subfrequência; variação do fator de potência; e suportabilidade a variações de tensão e frequência.

#### 2.6 HARDWARE-IN-THE-LOOP

O *firmware* desenvolvido nesse trabalho será validado através da simulação em HIL. A ferramenta HIL permite a simulação de circuitos de potência em tempo real, onde os dispositivos modelados são substituídos por componentes de hardware físicos reais, aumentando a precisão dos resultados da simulação (SPARN et al., 2018).

A metodologia HIL foi desenvolvida para a aplicação no setor automotivo e aeroespacial e se expandiu para a simulação em tempo real de componentes do sistema de energia, podendo ser utilizada para avaliar o desempenho do *hardware*, especialmente em condições específicas difíceis de reproduzir em um sistema físico (SPARN et al., 2018).

Nesse sentido, sistemas envolvendo plataformas HIL têm ganhado destaque em pesquisas relacionadas ao setor FV. Em González-Castaño et al. (2021) a técnica de HIL é utilizada para validar uma técnica de rastreamento de ponto de máxima potência (MPPT - *Maximum*

Power Point Tracking) desenvolvida, baseada em SVM (*support vector machines*). Brito et al. (2011) utiliza HIL para avaliar o comportamento dinâmico de um inversor solar FV durante mudanças de tensão e frequência, bem como condições de falha de curto circuito.

Em 2018, Johnson et al. (2018) apresentam a implementação da metodologia HIL como uma alternativa para os fornecedores de equipamentos FV a atender aos padrões da rede em evolução, validando o desempenho e promovendo melhorias em seus sistemas durante a fase de projeto. Em 2020, Menegazzo et al. (2020) mostram a implementação de uma bancada experimental para teste de *firmware* de inversor FV de acordo com as normas brasileiras de conexão com a rede elétrica de distribuição. A plataforma HIL desenvolvida possibilita o teste e desenvolvimento de inversores, em que o conversor estático de potência é emulado, enquanto o controle é realizado externamente pelo processador do inversor FV.

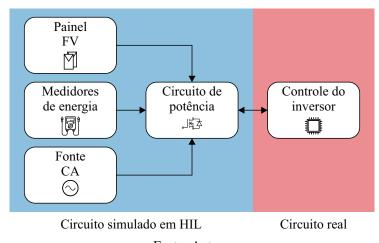

Nesse trabalho será utilizada a plataforma desenvolvida em (MENEGAZZO et al., 2020) para testar o *firmware* desenvolvido. Uma representação da plataforma de testes é mostrada na Figura 10.

Figura 10 – Representação da plataforma de testes em HIL.

Fonte: Autora.

O controlador físico será utilizado para controlar o modelo da planta simulado, trocando os sinais por meio de entradas e saídas do equipamento HIL.

#### 3 ESTUDO DE CASO: FIRMWARE PARA INVERSOR FOTOVOLTAICO CONEC-TADO À REDE

Esse capítulo aborda o projeto de um inversor fotovoltaico conectado à rede, utilizado para validar a metodologia que será apresentada no Capítulo 4.

Inicialmente, na seção 3.1, é feita a escolha da topologia do inversor utilizado para a realização dos testes. Com a topologia definida, na seção 3.2 é feita a modelagem do estágio de entrada, do barramento CC e do estágio CC-CA, juntamente com o filtro de saída. Em seguida, na seção 3.3 é feito o projeto dos elementos passivos do circuito.

Na seção 3.4 é apresentada a implementação das funções necessárias para o funcionamento do inversor, sendo elas: função de sincronismo com a rede; geração de referência; controle da corrente do inversor; gerador de referência para seguidor de ponto de operação de potência; controle do conversor *boost*; controle do barramento CC; além das funções de proteção e suporte a rede.

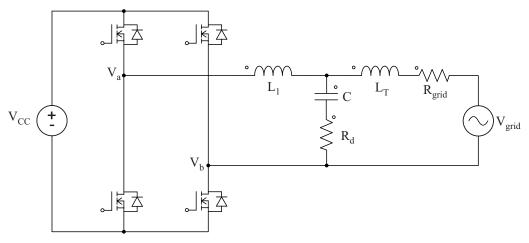

#### 3.1 TOPOLOGIA

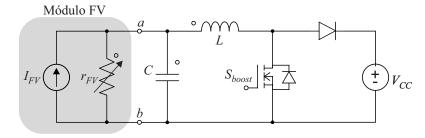

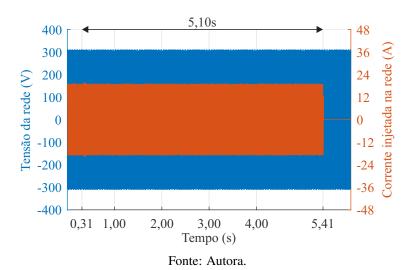

Para realizar os testes do *firmware* do inversor, foi definida a utilização de um inversor de 3,00~kW conectado a uma rede monofásica de  $220~V_{rms}$  e 60~Hz. A configuração escolhida é mostrada na Figura 11.

Figura 11 – Topologia do circuito de potência utilizado.

O estágio CC-CC é composto por um conversor elevador de tensão do tipo *boost*. A etapa de conversão CC-CA é realizada por um inversor *full-bridge* com modulação unipolar. A saída do inversor é conectado a um filtro de terceira ordem, LCL para fazer a interface com a rede. Os parâmetros do sistema proposto estão descritos na Tabela 1

Tabela 1 – Parâmetros do Sistema.

| Parâmetro                            | Valor     |

|--------------------------------------|-----------|

| Tensão RMS da rede $(V_g)$           | 220 V     |

| Frequência nominal da rede $(f_g)$   | 60Hz      |

| Potência nominal (P)                 | 3000 W    |

| Tensão do barramento CC ( $V_{CC}$ ) | 400 V     |

| Frequência de comutação $(f_s)$      | 21,60 kHz |

Fonte: Autora.

#### 3.2 MODELOS DINÂMICOS DOS ESTÁGIOS DE CONVERSÃO

#### 3.2.1 Estágio de Entrada

O estágio CC-CC é responsável por elevar a tensão, garantindo um valor adequado para o barramento CC, bem como fazer o rastreamento do ponto de operação de potência. Esse último funciona em dois modos de operação, o MPPT que faz o rastreamento de ponto de máxima potência, e o LPPT (*Limited Power Point Tracking*), que faz o rastreamento de potência limitada.

O circuito equivalente do conversor *boost* está representado na Figura 12.

Figura 12 – Circuito equivalente do conversor *boost*.

Fonte: Autora.

O circuito a esquerda dos terminais a e b, representa o circuito equivalente dos módulos FV. A fonte de corrente equivalente ( $I_{FV}$ ) é proporcional à irradiância, enquanto a resistência equivalente ( $r_{FV}$ ) está relacionada com ao quociente entre a tensão e a corrente, em um determinado ponto de operação da curva I-V do painel FV (FIGUEIRA et al., 2018).

Considerando a operação do conversor em modo de condução contínua, há duas etapas de operação. A primeira etapa ocorre enquanto o chave  $S_{boost}$  está conduzindo, durante o período  $D \cdot T_s$ , sendo D a razão cíclica e  $T_s$  o período de comutação. A segunda etapa ocorre quando a chave  $S_{boost}$  é bloqueada, pelo período de  $(1-D) \cdot T_s$ . As duas etapas de operação são apresentadas na Figura 13 (a) e (b), respectivamente.

Figura 13 – Etapas de operação do conversor *boost*. (a) Primeira etapa de operação. (b) Segunda etapa de operação.

Fonte: Autora.

Para a obtenção do modelo, as duas etapas de operação serão representadas em espaço de estados através das Equações 3.1 e 3.2.

$$\frac{d}{dt}\mathbf{x}(t) = \mathbf{A} \cdot \mathbf{x}(t) + \mathbf{B} \cdot \mathbf{u}(t), \tag{3.1}$$

$$\mathbf{y}(t) = \mathbf{C} \cdot \mathbf{x}(t),\tag{3.2}$$

onde,  $\mathbf{x}(t)$  é o vetor de estados sendo  $\mathbf{x}(t) = [v_C(t) \ i_L(t)]^T$ ,  $\mathbf{u}(t)$  é a matriz de entrada, nesse caso sendo  $\mathbf{u}(t) = [v_{CC} \ I_{FV}]^T$ . O vetor  $\mathbf{y}(t)$  representa as saídas do modelo. Para a realização do controle, é desejável ter como saída a corrente sobre o indutor e a tensão sobre o capacitor.

A partir da análise de circuitos são obtidas as seguintes matrizes de estado para a primeira etapa de operação:

$$\mathbf{A_1} = \begin{bmatrix} -\frac{1}{r_{FV} \cdot C} & -\frac{1}{C} \\ \frac{1}{L} & 0 \end{bmatrix} \quad \mathbf{B_1} = \begin{bmatrix} 0 & \frac{1}{C} \\ 0 & 0 \end{bmatrix} \quad \mathbf{C_1} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}. \tag{3.3}$$

Para a segunda etapa de operação são obtidas as seguintes matrizes:

$$\mathbf{A_2} = \begin{bmatrix} -\frac{1}{r_{FV} \cdot C} & -\frac{1}{C} \\ \frac{1}{L} & 0 \end{bmatrix} \quad \mathbf{B_2} = \begin{bmatrix} 0 & \frac{1}{C} \\ -\frac{1}{L} & 0 \end{bmatrix} \quad \mathbf{C_2} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}. \tag{3.4}$$

Para a obtenção do modelo, inicialmente é obtido o modelo médio, para isso é utilizada a aproximação de pequenas ondulações. Assim, assume-se que  $\mathbf{x}(t)$  e  $\mathbf{u}(t)$  não possuem grandes variações em um período de comutação. Dessa forma, o modelo médio em espaço de estados é resultado da média das matrizes para um período de comutação. Portanto, as equações médias em espaços de estados são dadas por:

$$\frac{d}{dt} \langle \mathbf{x}(t) \rangle_{T_s} = [d(t) \cdot \mathbf{A_1} + d'(t) \cdot \mathbf{A_2}] \cdot \langle \mathbf{x}(t) \rangle_{T_s} + [d(t) \cdot \mathbf{B_1} + d'(t) \cdot \mathbf{B_2}] \cdot \langle \mathbf{u}(t) \rangle_{T_s}, \quad (3.5)$$

$$\mathbf{y}(t) = [d(t) \cdot \mathbf{C_1} + d'(t) \cdot \mathbf{C_2}] \cdot \langle \mathbf{x}(t) \rangle_{T_s}, \tag{3.6}$$

onde d'(t) é o complemento da razão cíclica dado por d'(t) = 1 - d(t).

As matrizes médias obtidas são não-lineares, portanto é necessário fazer a linearização em torno de um ponto de operação, resultando em um modelo dinâmico de pequenos sinais. Para isso é necessário obter os valores dos estados e da saída em regime permanente, **X** e **Y**, dados por:

$$\mathbf{X} = -\mathbf{A}^{-1} \cdot \mathbf{B} \cdot \mathbf{U},\tag{3.7}$$

$$\mathbf{Y} = (-\mathbf{C} \cdot \mathbf{A}^{-1} \cdot \mathbf{B}) \cdot \mathbf{U},\tag{3.8}$$

onde A, B e C são as matrizes médias obtidas anteriormente para um ponto de operação de razão cíclica, e U é o vetor de entrada em regime permanente.

A linearização é feita com o método de pequenas perturbações, assim, todas as variáveis médias e a razão cíclica são consideradas como sendo a soma dos valores em regime permanente com um pequeno valor de perturbação, dessa forma se tem:

$$\langle \mathbf{x}(t) \rangle_{T_s} = \mathbf{X} + \hat{\mathbf{x}}(t),$$

(3.9)

$$\langle \mathbf{u}(t) \rangle_{T_c} = \mathbf{U} + \hat{\mathbf{u}}(t),$$

(3.10)

$$\langle \mathbf{y}(t) \rangle_{T_s} = \mathbf{Y} + \mathbf{\hat{y}}(t),$$

(3.11)

$$d(t) = \mathbf{D} + \hat{\mathbf{d}}(t). \tag{3.12}$$

Substituindo as Equações 3.9, 3.10, 3.11 e 3.12 em 3.5, 3.6 e considerando  $d\mathbf{X}/dt$  igual a zero, desprezando os termos não-lineares de  $2^a$  ordem e os termos em regime permanente, chega-se ao modelo dinâmico linearizado dado por:

$$\frac{d}{dt}\hat{\mathbf{x}}(t) = \mathbf{A} \cdot \hat{\mathbf{x}}(t) + \mathbf{B} \cdot \hat{\mathbf{u}}(t) + \{(\mathbf{A_1} - \mathbf{A_2}) \cdot \mathbf{X} + (\mathbf{B_1} - \mathbf{B_2}) \cdot \mathbf{U}\} \cdot \hat{d}(t), \tag{3.13}$$

$$\mathbf{y}(t) = \mathbf{C} \cdot \hat{\mathbf{x}}(t) + \{(\mathbf{C_1} - \mathbf{C_2}) \cdot \mathbf{X}\} \cdot \hat{d}(t). \tag{3.14}$$

Para fazer a representação em espaço de estados na forma padrão dada por 3.1 e 3.2 é necessário multiplexar o vetor de entradas, bem como a matriz  $\mathbf{B}$  que é associada ao vetor de entradas. Dessa forma chega-se a um novo vetor de entrada  $\hat{\mathbf{u}}_{\mathbf{t}}(t)$  e a uma nova matriz  $\mathbf{B}_{\mathbf{t}}$  dados por:

$$\hat{\mathbf{u}}_{\mathbf{t}}(\mathbf{t}) = \begin{bmatrix} \hat{\mathbf{u}}(t) \\ \hat{d}(t) \end{bmatrix} \quad \mathbf{B}_{\mathbf{t}} = \begin{bmatrix} \mathbf{B} & (\mathbf{A}_{1} - \mathbf{A}_{2}) \cdot \mathbf{X} + (\mathbf{B}_{1} - \mathbf{B}_{2}) \cdot \mathbf{U} \end{bmatrix}. \tag{3.15}$$

As matrizes A e C permanecem as mesmas.

#### 3.2.2 Barramento CC

Entre o *boost* e o inversor há o barramento CC, o qual deve ter sua tensão controlada. O modelo do barramento CC, utilizado para o projeto do controlador, se fundamenta em relação ao somatório das potências envolvidas no processo de carga e descarga do banco de capacitores (TIBOLA, 2017), ilustrado na Figura 14.

Figura 14 – Representação do fluxo de potência no barramento CC.

Dessa forma, tem-se que:

$$P_{FV} = P_{inv} + P_{CCC}, (3.16)$$

onde:

$$P_{Ccc} = \frac{C}{2} \frac{d}{dt} V_{CC}^{2}.$$

(3.17)

O controle do barramento é feito através da potência do inversor. Dessa forma, para a obtenção do modelo para controle, a potência proveniente do *boost*  $P_{FV}$  é considerado um distúrbio e é desconsiderada da função de transferência. Dessa forma, o modelo que relaciona a tensão do barramento com a potência de referência do inversor, é dado por:

$$G_{\nu}(s) = \frac{V_{CC}^2}{P_{inv}} = -\frac{2}{C \cdot s}.$$

(3.18)

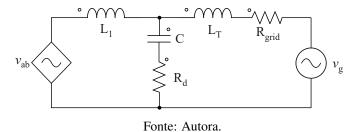

#### 3.2.3 Estágio de Saída

Para realizar a modelagem do inversor e do filtro de saída, o primeiro estágio de conversão composto pelo inversor CC-CC é simplificado para uma fonte de tensão fixa com tensão  $V_{CC}$ . Ainda, é adicionado em série com a rede uma resistência que compõe a impedância da rede. A indutância referente a rede é agrupada com o indutor  $L_2$  do filtro, resultando na indutância  $L_T$ . O circuito a ser modelado está apresentado na Figura 15. A modelagem é feita tendo como referência o trabalho de Enderle (2012).

Figura 15 – Circuito composto pelo inversor e filtro de saída.

Fonte: Autora.

Inicialmente, o inversor é representado por uma fonte controlada cujo valor de tensão é  $v_{ab}(t)$ , que é a diferença de tensão entre os terminais a e b da Figura 15. O circuito equivalente é mostrado na Figura 16.

Figura 16 – Circuito equivalente para modelagem.

O modelo médio do circuito da Figura 16 é representado em espaço de estados através das Equações 3.19 e 3.20.

$$\frac{d}{dt}\mathbf{x}(t) = \mathbf{A} \cdot \mathbf{x}(t) + \mathbf{B} \cdot u(t) + \mathbf{B}_{\mathbf{w}} \cdot w(t), \tag{3.19}$$

$$\mathbf{y}(t) = \mathbf{C} \cdot \mathbf{x}(t). \tag{3.20}$$

Nesse caso,  $\mathbf{x}(t)$  é o vetor de estados onde  $\mathbf{x}(t) = [i_{L_1}(t) \quad i_{L_2}(t) \quad v_C(t)]^T$ , u(t) é a entrada, nesse caso sendo  $u(t) = v_{ab}(t)$  e w(t) é um distúrbio onde  $w(t) = v_g(t)$ . A tensão da rede é considerada como sendo uma perturbação para a planta, uma vez que é uma entrada exógena ao circuito, a qual não se tem controle.

A partir da análise de circuitos se tem as seguintes matrizes de estado:

$$\mathbf{A} = \begin{bmatrix} -\frac{R_d}{L_1} & -\frac{R_d}{L_1} & -\frac{1}{L_1} \\ -\frac{R_d}{L_2 + L_g} & -\frac{(R_d + R_g)}{L_2 + L_g} & -\frac{1}{L_2 + L_g} \\ \frac{1}{C} & \frac{1}{C} & 0 \end{bmatrix} \quad \mathbf{B} = \begin{bmatrix} \frac{1}{L_1} \\ 0 \\ 0 \end{bmatrix} \quad \mathbf{B}_{\mathbf{w}} = \begin{bmatrix} 0 \\ \frac{1}{L_2 + L_g} \\ 0 \end{bmatrix} \quad \mathbf{C} = \begin{bmatrix} 0 & 1 & 0 \end{bmatrix}. \quad (3.21)$$

A tensão  $v_{ab}$  é definida como  $v_a(t) - v_b(t)$ , onde:

$$v_a(t) = d(t) \cdot V_{CC} \tag{3.22}$$

$$v_b(t) = [1 - d(t)] \cdot V_{CC} \tag{3.23}$$

onde d(t) é a razão cíclica variante no tempo, assim, obtém-se:

$$v_{ab}(t) = [(2 \cdot d(t) - 1)] \cdot V_{CC}, \tag{3.24}$$

desprezando a componente CC, chegamos à:

$$v_{ab}(t) = 2 \cdot d(t) \cdot V_{CC}. \tag{3.25}$$

Ainda, para obter o modelo do sistema em razão da ação de controle u(t), é obtido o modelo dinâmico do modulador. As chaves do inversor são acionadas utilizando a técnica de modulação por largura de pulso (PWM - *Pulse Widht Modulation*). A modulação unipolar é utilizada de forma que a tensão de saída varia entre 3 níveis:  $+V_{CC}$ , zero e  $-V_{CC}$ . Dessa forma, tem-se a relação dada pela Equação 3.26

$$d(t) = 0.5 + \frac{1}{V_M} \cdot u(t), \tag{3.26}$$

onde  $V_M$  é o valor de pico a pico da portadora triangular. Desprezando a componente CC se obtém:

$$d(t) = \frac{1}{V_M} \cdot u(t). \tag{3.27}$$

Utilizando a Equação 3.25 e 3.27 chega-se a expressão da tensão  $v_{ab}$ :

$$v_{ab} = 2 \cdot \frac{1}{V_M} \cdot u(t) \cdot V_{CC}. \tag{3.28}$$

Substituindo 3.28 nas matrizes de espaço de estados dadas na Equação 3.21, obtém-se a equação de estados que relaciona a corrente de saída do conversor, com o sinal de controle u(t), dada pela Equação 3.29.

$$\begin{bmatrix} i_{L_{1}}(t) \\ i_{L_{2}}(t) \\ v_{C}(t) \end{bmatrix} = \begin{bmatrix} -\frac{R_{d}}{L_{1}} & -\frac{R_{d}}{L_{1}} & -\frac{1}{L_{1}} \\ -\frac{R_{d}}{L_{2} + L_{g}} & -\frac{(R_{d} + R_{g})}{L_{2} + L_{g}} & -\frac{1}{L_{2} + L_{g}} \\ \frac{1}{C} & \frac{1}{C} & 0 \end{bmatrix} \cdot \begin{bmatrix} i_{L_{1}}(t) \\ i_{L_{2}}(t) \\ v_{C}(t) \end{bmatrix} + \begin{bmatrix} \frac{2 \cdot V_{CC}}{L_{1} \cdot V_{M}} \\ 0 \\ 0 \end{bmatrix} \cdot \begin{bmatrix} u(t) \end{bmatrix} + \begin{bmatrix} 0 \\ \frac{1}{L_{2} + L_{g}} \\ 0 \end{bmatrix} \cdot \begin{bmatrix} V_{g}(t) \end{bmatrix}.$$

(3.29)

## 3.3 DIMENSIONAMENTO DOS ELEMENTOS PASSIVOS DOS CONVERSORES

# 3.3.1 Estágio de entrada

O dimensionamento dos elementos passivos do conversor *boost* considera os parâmetros da Tabela 2.

Tabela 2 – Parâmetros para projeto do conversor boost.

| Parâmetro                               | Valor      |

|-----------------------------------------|------------|

| Potência ativa ( <i>P</i> )             | 3000 W     |

| Frequência de comutação $(f_s)$         | 43,20  kHz |

| Ondulação de corrente ( $\Delta i_L$ )  | 10%        |

| Ondulação de tensão ( $\Delta V_{FV}$ ) | 7%         |

| Tensão de saída ( $V_{CC}$ )            | 400 V      |

| Mínima tensão FV ( $V_{FV_{min}}$ )     | 100 V      |

Fonte: Autora.

Para o cálculo do indutor é utilizado a Equação 3.30 (MARTINS; BARBI, 2006).

$$L = \frac{V_{FV} \cdot D}{\Delta i_L \cdot f_s} \tag{3.30}$$

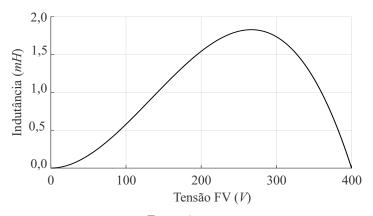

O valor da tensão  $V_{FV}$  varia dependendo da radiância e da temperatura do módulo. Além disso, está associada com o modelo de painel FV utilizado. Nesse sentido a Equação 3.30 é aplicada para diferentes valores de  $V_{FV}$  variando de 0 V a 400 V, resultando no gráfico da Figura 17.

Figura 17 - Gráfico de variação da indutância

Fonte: Autora.

A partir da análise do gráfico, observa-se que para manter a ondulação de corrente dentro

do valor estabelecido, para todos os casos, o valor da indutância deve ser superior a 1,83 mH. Dessa forma é estabelecida uma indutância de 2 mH para o conversor boost.

O dimensionamento do capacitor de entrada é calculado pela Equação 3.31 (REIS, 2017).

$$C = \frac{P}{2 \cdot f_s \cdot V_{FV} \cdot \Delta V_{FV}} \tag{3.31}$$

Para o cálculo da capacitância é utilizado o valor mínimo de  $V_{FV}$ , que resulta na maior capacitância necessária. Assim, para manter a ondulação de tensão especificada, o capacitor deve ser maior que 49,60  $\mu F$ . Nesse sentido, é estabelecido um capacitor de 50  $\mu F$  para o conversor *boost*.

#### 3.3.2 Barramento CC

O dimensionamento do capacitor do barramento CC é dado pela Equação 3.32 (ME-MON; BHUTTO; BURIRO, 2020).

$$C_{CC} = \frac{S}{2 \cdot \pi \cdot f_g \cdot V_{CC} \cdot \Delta V_{CC}},\tag{3.32}$$

onde S é a potência nominal aparente do inversor,  $f_g$  é a frequência da rede e  $\Delta V_{CC}$  é a ondulação de tensão sobre o barramento.

De acordo com Memon, Bhutto e Buriro (2020), o valor da ondulação de tensão deve ser mantido abaixo de 8,5%. Para o projeto do capacitor do barramento, é considerada uma ondulação de tensão permitida de 5%, que resultou em um capacitor de 1000  $\mu F$ .

# 3.3.3 Estágio de saída

O projeto do filtro de saída do inversor é feito utilizando os procedimentos demonstrados em Zhou et al. (2020). Inicialmente é realizada a escolha do indutor do lado do conversor  $L_1$ . O dimensionamento é feito a partir da análise de ondulação da corrente de saída do inversor. Quanto menor for a ondulação de corrente requerida, melhor será a qualidade da corrente gerada, todavia, gera elementos passivos demasiadamente grandes.

Para o projeto é definida uma ondulação de corrente de 20%. A Equação 3.33 é utilizada para determinar o valor da indutância.

$$\Delta I_{m\acute{a}x} = \frac{1}{8} \frac{V_{CC}}{L_1 \cdot f_s},\tag{3.33}$$

onde  $V_{CC}$  é a tensão no barramento de entrada do inversor,  $f_s$  é a frequência de chaveamento, e  $\Delta I_{m\acute{a}x}$  é a ondulação de corrente definida. A partir da equação se obteve um valor de indutância

de 1,20 *mH*.

O dimensionamento do capacitor deve ponderar entre a qualidade da filtragem e a limitação de perdas. Dessa forma, determina-se que a potência reativa consumida pelo capacitor deve se limitar a 5% da potência nominal do sistema. Assim, a Equação 3.34 é utilizada para determinar o valor do capacitor do filtro.

$$C \le 5\% \frac{P}{2 \cdot \pi \cdot f_g \cdot V_g^2},\tag{3.34}$$

onde P é a potência de saída do inversor,  $f_g$  e  $V_g$  são a frequência e a tensão da rede, respectivamente. A partir da equação é determinada uma capacitância de  $8,00~\mu F$ .

Para o dimensionamento do indutor do lado da rede,  $L_2$ , é considerada a frequência de ressonância do filtro,  $f_{res}$ , que é dada pela Equação 3.35.

$$f_{res} = \frac{1}{2 \cdot \pi} \sqrt{\frac{L_1 + L_2}{L_1 \cdot L_2 \cdot C}}.$$

(3.35)

Tipicamente, a frequência de ressonância deve deve ser maior que 10 vezes a frequência fundamental da rede e menor que a metade da frequência de comutação. Frequências de ressonância muito próximas da frequência da rede dificultam o controle do inversor. No entanto, se esta for muito próxima da frequência de chaveamento, os ruídos de comutação não são atenuados. Além disso, quanto menor for a frequência de ressonância, melhor é a filtragem das harmônicas, mas maior serão os elementos passivos.

Considerando as restrições, é definida uma frequência de ressonância de 3,00 kHz que resulta em um indutor para o lado da rede de 0,5 mH. Para amortecer a ressonância é utilizada a técnica passiva de inserir um resistor em série com o capacitor. A técnica é escolhida devido a sua simplicidade, no entanto, a inserção do resistor gera perdas indesejáveis para o sistema. Dessa forma, para limitar as perdas, sugere-se que o resistor de amortecimento tenha o valor limitado pela Equação 3.36.

$$R_{d,m\acute{a}x} = \frac{1}{2 \cdot \pi \cdot f_{res} \cdot C}.$$

(3.36)

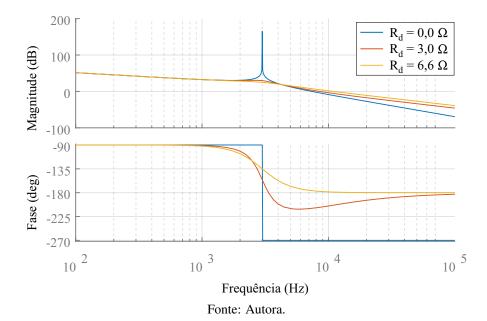

A partir da Equação 3.36 se obteve um resistor máximo de amortecimento de 6,63  $\Omega$ . No entanto para limitar mais ainda as perdas foi definido um  $R_d$  de 3,00  $\Omega$  que foi suficiente para deixar o controle estável.

A Figura 18 mostra o diagrama de bode do sistema sem o amortecimento, com  $R_d$  de 3,0  $\Omega$  e 6,6  $\Omega$ .

Através da figura é possível observar que a inserção da resistência de amortecimento faz com que o pico de ressonância seja eliminado. Além disso, avaliando o comportamento da fase, é possível observar que quanto maior for a resistência de amortecimento, melhor é a margem de fase aumentando a margem de estabilidade do sistema.

Figura 18 – Diagrama de bode para diferentes valores de  $R_d$ .

# 3.4 SISTEMA DE CONTROLE, PROTEÇÃO E GERAÇÃO DE REFERÊNCIAS

# 3.4.1 Geração de referências de sincronismo com a rede

A corrente injetada pelo inversor deve operar em sincronismo com a rede elétrica (ABNT, 2013b). Portanto é necessário um algoritmo de sincronização para corrigir o ângulo de fase entre a tensão da rede e a corrente injetada. Tendo a magnitude e o ângulo de fase da tensão da rede é possível regular a potência ativa e reativa fornecida à rede (TEODORESCU; LISERRE; RODRIGUEZ, 2011). Além disso, o algoritmo fornece o valor da frequência, utilizada para as proteções de sobrefrequência e subfrequência além das funções de suporte a rede.

Dentre os métodos de sincronização, a estrutura PLL (*phase-locked loop*) é uma das mais populares (WU et al., 2022) e será o método implementado nessa dissertação. A Figura 19 ilustra a estrutura básica de um PLL (TEODORESCU; LISERRE; RODRIGUEZ, 2011).

PD LF VCO  $k_{P} + k_{i} \int cos(x) dx$   $k_{P} + k_{i} \int cos(x) dx$

Figura 19 – Estrutura básica do PLL.

Fonte: Adaptado de (TEODORESCU; LISERRE; RODRIGUEZ, 2011).

O PD (*phase detector*) gera um sinal proporcional à diferença de fase entre o sinal de entrada e o sinal gerado pelo oscilador. O LF (*loop filter*) faz a filtragem para atenuar componentes alternadas de alta frequência do sinal de saída do PD. O LF é usualmente constituído por um filtro passa-baixas de primeira ordem ou por um controlador PI. O VCO (*voltage-controlled*

oscillator) gera um sinal CA com frequência que varia em relação a uma frequência central dada,  $\omega_c$ .

Na literatura exitem diversos formas de implementar o detector de fase. Exemplos são PLL baseado na transformada de Hilbert (FØYEN et al., 2020), PLL baseado na transformada inversa de Park (NAYAK; GURUNATH; RAJASEKAR, 2016), PLL com filtro *notch* adaptativo (BREZOVIĆ; KUDJÁK, 2010), PLL baseado em Integrador Generalizado de Segunda Ordem (SOGI-PLL) (TEODORESCU; LISERRE; RODRIGUEZ, 2011), etc.

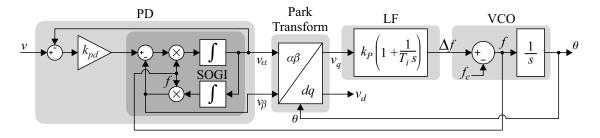

Nesse trabalho, para realizar a sincronia da tensão da rede com a corrente injetada pelo inversor, é utilizado o SOGI-PLL. O diagrama do SOGI-PLL é apresentado na da Figura 20.

PD Transformada LF VCO  $v_{\alpha}$   $v_{\alpha$

Figura 20 – Estrutura do SOGI-PLL.

Fonte: Adaptado de (TEODORESCU; LISERRE; RODRIGUEZ, 2011).

O PD gera dois sinais defasados em 90°,  $v_{\alpha}$  e  $v_{\beta}$ , os quais são dados pelas equações:

$$\frac{v_{\alpha}}{v}(s) = \frac{k_{pd} \cdot \omega' \cdot s}{s^2 + k_{pd} \cdot \omega' \cdot s + {\omega'}^2},$$

(3.37)

$$\frac{v_{\beta}}{v}(s) = \frac{k_{pd} \cdot {\omega'}^2}{s^2 + k_{pd} \cdot {\omega'} \cdot s + {\omega'}^2}.$$

(3.38)

É feita a transformada de Park dos sinais  $v_{\alpha}$  e  $v_{\beta}$ , resultando  $v_d$  e  $v_q$ . O módulo do sinal  $v_d$  resulta na amplitude do sinal de entrada. Já o sinal  $v_q$  passa pelo controlador PI, Equação 3.39, resultando no valor de desvio de frequência em relação a frequência nominal,  $\Delta f$ .

$$\frac{\Delta f}{v_q} = \frac{K_p \cdot s + K_i}{s} \tag{3.39}$$

Dessa forma, somando  $\Delta f$  com o valor da frequência nominal, tem-se a frequência de operação do sistema, em Hz. O valor da frequência é passado por um integrador que resulta no valor de fase da rede.

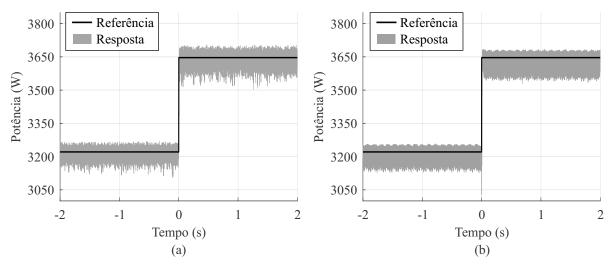

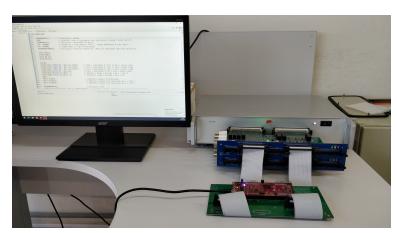

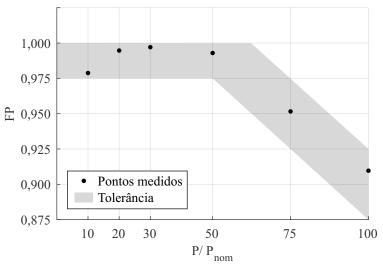

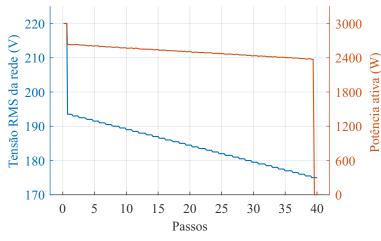

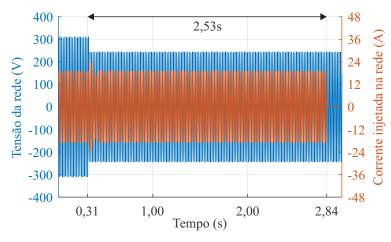

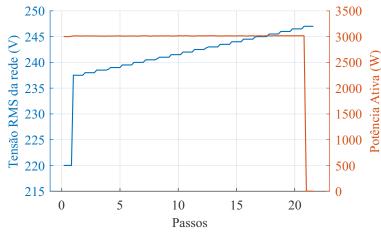

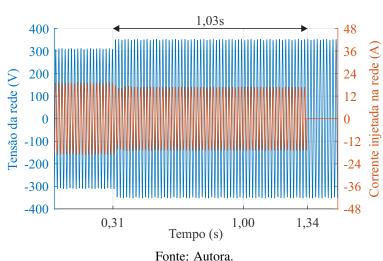

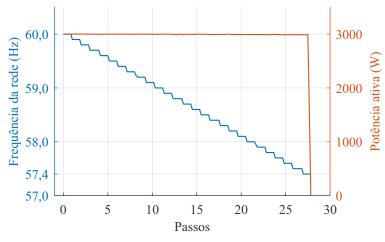

# 3.4.2 Gerador de referência de corrente do estágio de saída